Part 01

前言

作為一名硬件工程師,從接觸單片機的那天,就看到MCU的旁邊經常看到會用到晶振,經常的旁邊往往會放兩個電容,有時候還會再放個電阻,很多硬件工程師都是看別的工程師放多大的電容,電阻,自己也跟著放,這樣也沒錯,但是知其然不知其所以然,對你的硬件水平提高是沒有任何幫助的,今天我們就講一下晶振電路,以及晶振外圍阻容器件的選型計算,下一篇文章會講晶振和MCU是否匹配已經晶振常見問題處理。

Part 02

晶振電路

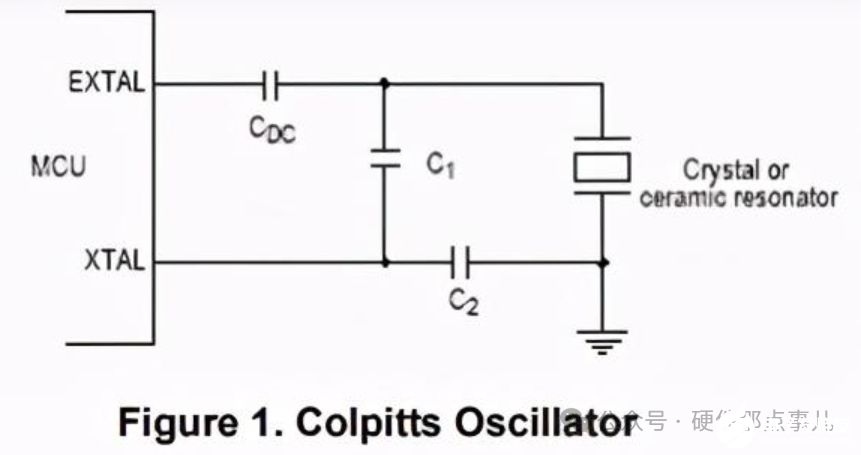

晶振電路有兩種,一種是Pierce電路,另外一種是Colpitts電路,其實就是兩種晶振拓撲,比較常用的是Pierce電路。所以我們大概介紹一下Colpitts電路的特點就跳過了,采用Colpitts電路的晶振的缺點是晶振兩端會有雜散電抗,此時比較難考慮雜散電抗的影響,說白了就是計算起來比較麻煩,電路可靠性也更低,還會在晶振兩端形成DC偏置電壓,優點是電路有振幅限制,從而功耗更低,對外部電路輻射干擾更小。

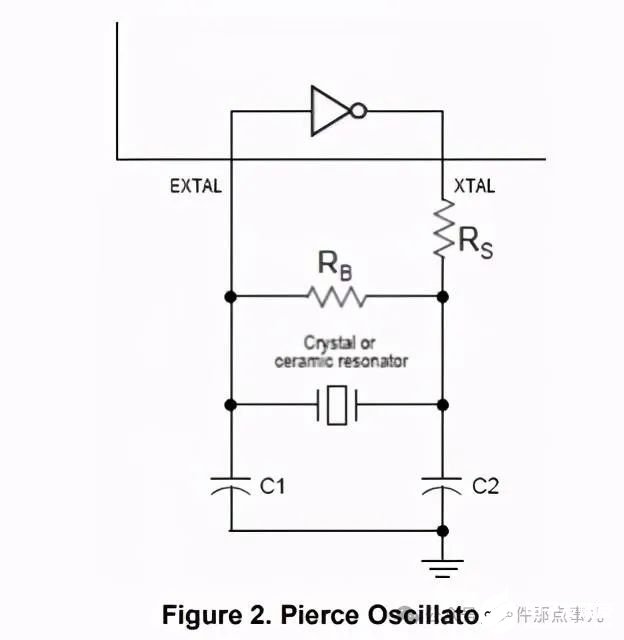

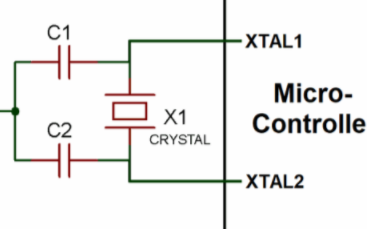

我們重點要介紹的是Pierce電路,具體電路就是下圖這種形式,也是最常見的拓撲圖,該電路一般由非門電路(增益特別大的運放),反饋電阻,負載電容構成,電容和晶振是外置的,一般要自己選型,運放和反饋電阻一般集成在IC內部,啟動速度更快,可靠性更高,所以說除非有很嚴苛的功耗要求,一般推薦使用此電路。

1)Rs是限流電阻,Rs的值越小,晶振啟動速度越快,為了避免晶振過驅動,Rs也不能過小,在高頻晶振中,Rs可以短路。

2)Rb是反饋電阻,為運放輸入提供反饋,讓運放工作在線性區,當運放工作在線性區時,晶振才能正常起振,當然反饋電阻Rb也會影響運放的環路增益,反饋電阻越大,增益越大。

Part 03

阻容元件計算

1)負載電容計算

Cl=(C1*C2) / (C1+C2)+Cs+Cp

Cs就是晶振內部的雜散電容,晶振規格書中一般會標出該值,Cp就是PCB板上的走線以及晶振引腳的寄生電容,Cs和Cp的電容加起來總計2-8pF,最準確的方法是通過測試晶振輸出波形來確認負載電容是否合適。負載電容越大,晶振頻率越低。C1越大,反饋越弱,越不利于晶振起振,晶振就無法穩定工作,當然了反饋過強,會導致晶振過驅動,也會有問題。

大家需要注意的是負載電容一定要選用NP0或C0G電容才可以,溫度穩定性更高,這樣頻率才會更穩定。

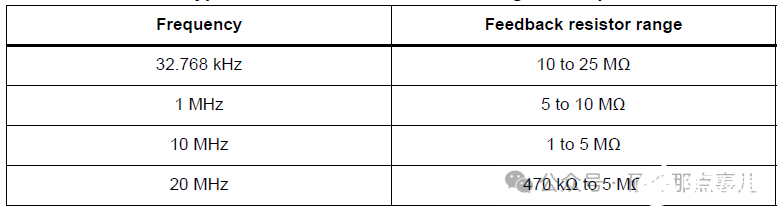

2)反饋電阻計算

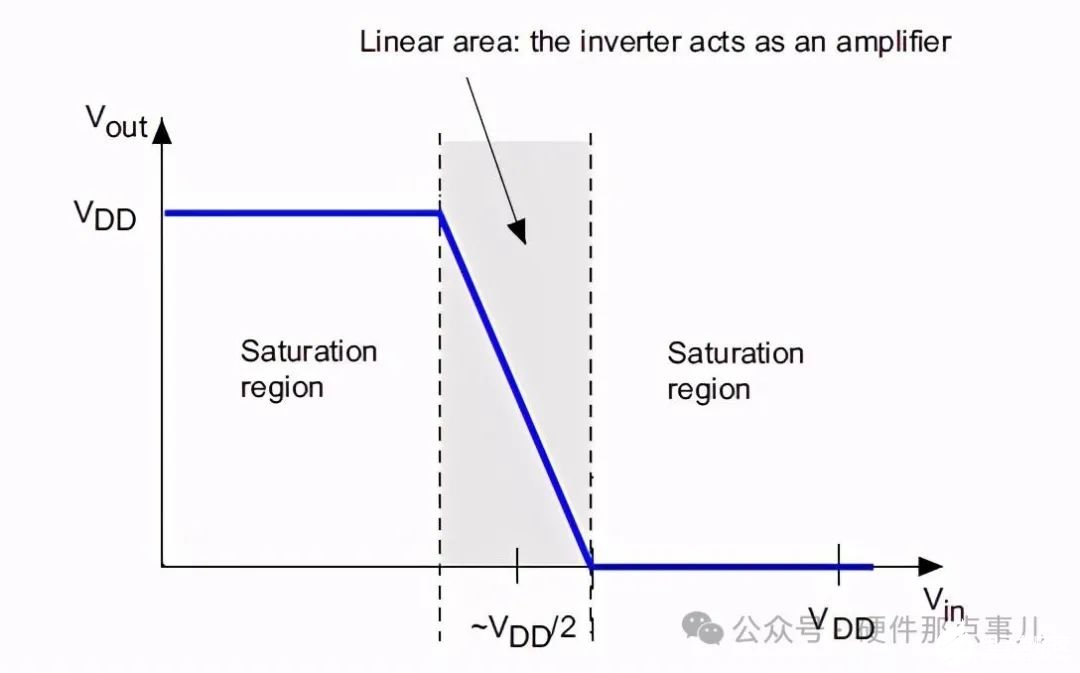

反饋電阻的作用是讓晶振電路的反相器工作在線性區,也就是下圖的陰影區時,這時候電路沒有飽和,屬于負反饋放大電路,才會穩定持續工作,反饋電阻的作用就在這里,那么反饋電阻怎么計算呢?我查閱了很多文檔,都沒有給出計算公式,但是找到了一份配置表,大家可以參考。

今天我們就講到這里了,下一篇文章會講一下晶振電路和MCU的兼容性計算,這點非常重要,因為晶振電路到底行不行還要看你選的MCU是否認可,那么怎么通過計算確認呢?敬請關注。

▼硬件那點事兒▼

-

mcu

+關注

關注

146文章

17901瀏覽量

362200 -

晶振

+關注

關注

35文章

3230瀏覽量

69776 -

系統電路

+關注

關注

0文章

4瀏覽量

6796 -

晶振電路

+關注

關注

7文章

96瀏覽量

25769

發布評論請先 登錄

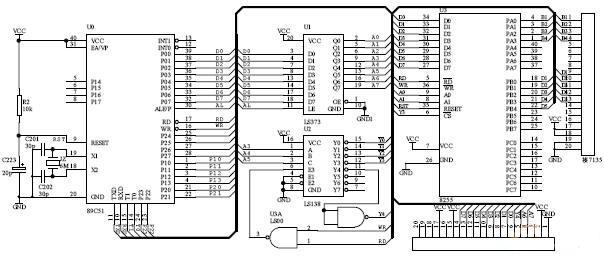

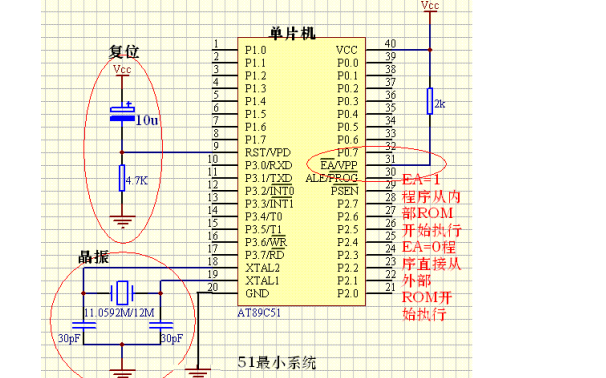

最小系統電路圖

51單片機的最小系統電路圖和復位電路的詳細資料說明

51單片機最小系統是什么?51單片機最小系統的電路介紹

MCU最小系統電路設計指南

MCU最小系統電路中的晶振電路如何選型計算呢?1100字搞定它!

MCU最小系統電路中的晶振電路如何選型計算呢?1100字搞定它!

評論