近日,三疊紀(廣東)科技有限公司在東莞松山湖隆重舉行了TGV板級封裝線的投產儀式,標志著我國正式邁入TGV板級封裝技術的先進行列。作為國內首條投產的TGV板級封裝線,這一里程碑式的成就不僅彰顯了我國在半導體和集成電路產業領域的創新實力,更為行業的未來發展注入了強勁動力。

TGV,即玻璃通孔技術,是實現穿過玻璃基板垂直電氣互連的關鍵手段。該技術以高品質硼硅玻璃、石英玻璃為基石,通過一系列精密復雜的工藝流程——包括種子層濺射、電鍍填充、化學機械平坦化、RDL再布線以及bump工藝引出——構建出三維互聯的先進封裝結構。這一技術的突破,被視為下一代先進封裝集成的核心技術,對于提升半導體器件的性能、可靠性及集成度具有重大意義。

三疊紀科技有限公司此次投產的TGV板級封裝線,與國際前沿技術同步起步,實現了從“跟跑”到“并跑”乃至“領跑”的跨越。這一成就不僅展示了我國半導體和集成電路產業在技術創新方面的強勁勢頭,更為行業的高質量發展提供了有力支撐。未來,隨著TGV板級封裝技術的廣泛應用,我國半導體和集成電路產業將迎來更加廣闊的發展空間和更加美好的發展前景。

-

集成電路

+關注

關注

5416文章

11926瀏覽量

366877 -

半導體

+關注

關注

335文章

28509瀏覽量

231793 -

封裝

+關注

關注

128文章

8447瀏覽量

144699

發布評論請先 登錄

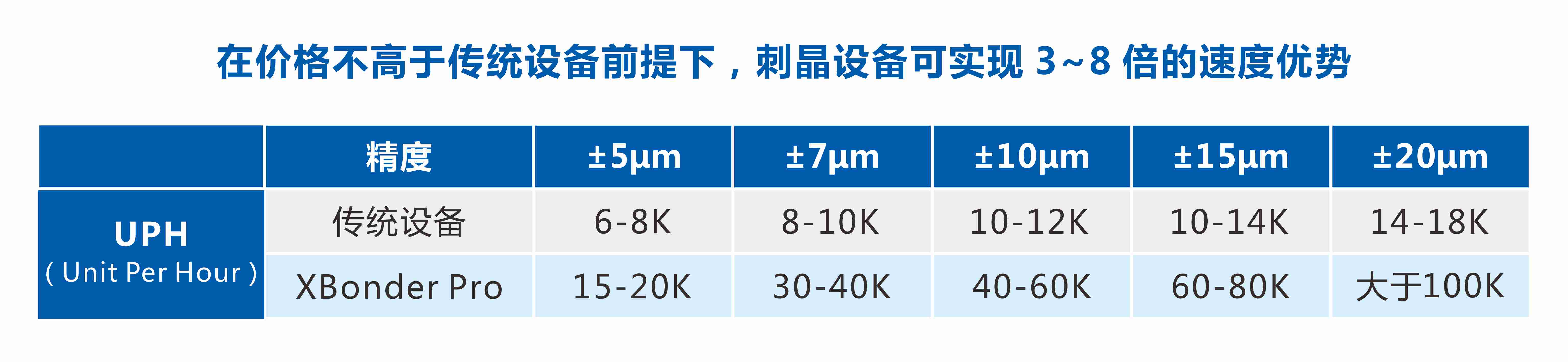

簽約頂級封裝廠,普萊信巨量轉移技術掀起晶圓級封裝和板級封裝的技術革命

玻璃通孔(TGV)技術深度解析

玻璃通孔(TGV)技術原理、應用優勢及對芯片封裝未來走向的影響

一文了解玻璃通孔(TGV)技術

正式投產!天成先進12英寸晶圓級TSV立體集成生產線

又一項目開工!聚焦TGV玻璃基板等產線!

Manz集團成功交付多尺寸板級封裝RDL量產線

Manz亞智科技RDL制程打造CoPoS板級封裝路線,滿足FOPLP/TGV應用于下一代AI需求

Manz亞智科技RDL制程打造CoPoS板級封裝路線, 滿足FOPLP/TGV應用于下一代AI需求

一文了解芯片三維封裝(TSV及TGV)技術

評論