隨著集成電路工藝技術的不斷發展,為了提高集成電路的集成度,同時提升器件的工作速度和降低它的功耗,集成電路器件的特征尺寸不斷按比例縮小,工作電壓不斷降低。為了有效抑制短溝道效應,除了源漏的結深不斷降低和溝道的摻雜濃度也不斷增加外,柵氧化層的厚度也不斷降低,從而提高柵電極電容,達到提高柵對溝道的控制能力,同時調節閾值電壓。柵氧化層的厚度是隨著溝道長度的減小而近似線性降低的,每一代大概是前一代的0.7倍左右,從而獲得足夠的柵控能力。另外,隨著柵氧化層厚度的不斷降低,MOS 管的驅動能力也會相應提高。

20 世紀60年代,最初的柵極材料是鋁金屬,氧化層的介質層是純二氧化硅,柵極疊層結構是由純二氧化硅和金屬柵極組成。后來開發出多晶硅柵極,柵極疊層結構變為由純二氧化硅和重摻雜的多晶硅柵極組成。因為通過多晶硅柵極可以實現自對準,另外也可通過調節摻雜多晶硅柵的類型調節器件的閾值電壓。NMOS 柵極的多晶硅摻雜類型是n 型,PMOS柵極的多晶硅摻雜類型是p 型。對于厚度大于4nm 的柵氧化層,它是理想的絕緣體,因為SiO2的禁帶寬度高達9eV,Si的禁帶寬度是1.12eV,它們之間會形成巨大的勢壘高度,在器件正常的偏置電壓的條件下,電子或者空穴不可能越過柵氧化層與硅形成的勢壘,所以不會形成柵極漏電流。

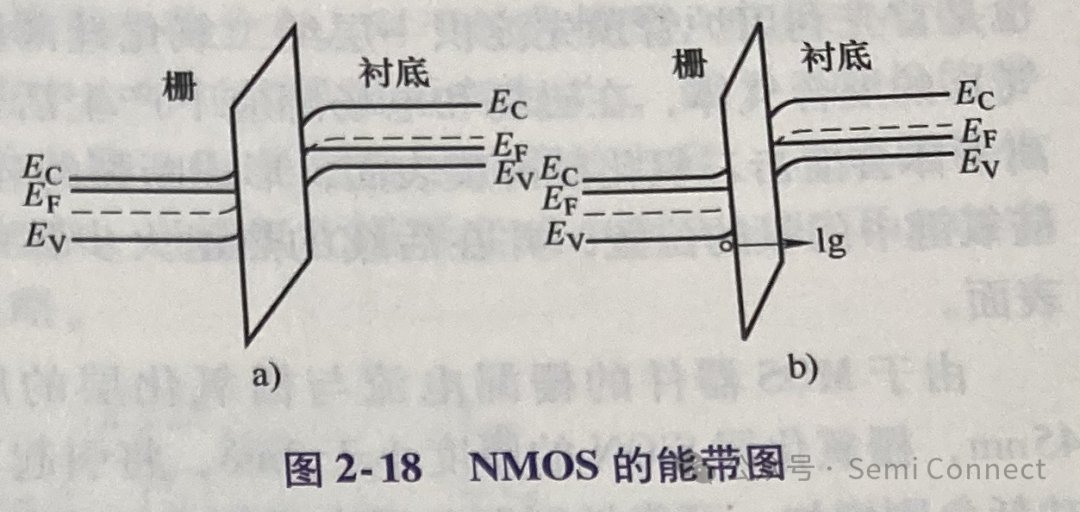

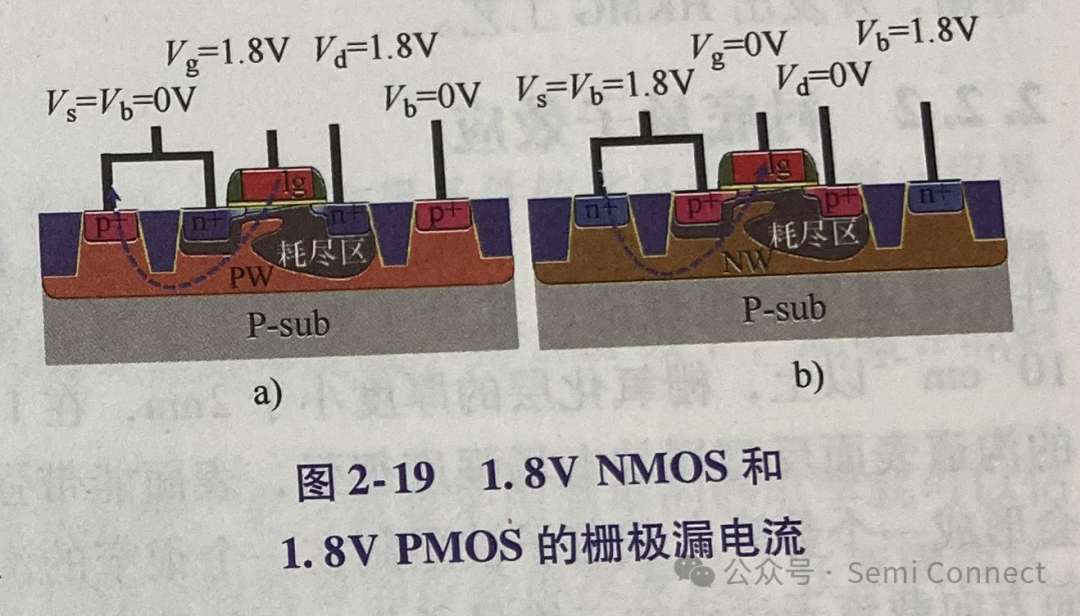

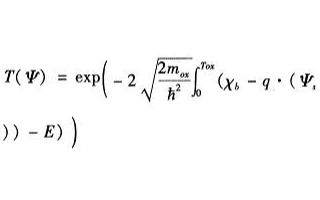

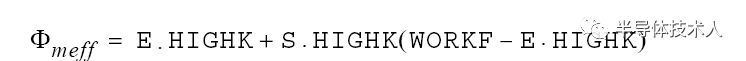

圖2-18所示為 NMOS的能帶圖,圖2-18a 是柵氧化層的厚度大于4nm,襯底與柵之間沒有形成明顯的漏電流。隨著柵氧化層厚度的不斷降低,當純二氧化硅的厚度小于3nm 時,它不再是理想的絕緣體,柵極與襯底之間將會出現明顯的量子隧穿效應,襯底的電子以量子的形式穿過柵介質層進入柵,形成柵極漏電流。柵極漏電流會隨著柵氧化層厚度的減小而呈現指數級增長,柵氧化層物理厚度每減小0.2nm,隧穿電流就增大10倍,柵極漏電流增加會導致集成電路的功耗急劇增加,功耗增加導致集成電路發熱從而影響集成電路的可靠性。另外,PMOS多晶硅柵極中的硼離子也會穿過柵介質層進入襯底,導致閾值電壓漂移。圖2-18b是柵氧化層的厚度小于3nm 時,多晶硅柵極的空穴不再進入柵氧化層的價帶,而是表現為波動性,直接以量子的形式隧穿柵氧化層的梯形勢壘,進入襯底形成漏電流。圖2-19所示為1.8V NMOS 和1.8V PMOS 的柵極漏電流方向。NMOS 的柵極漏電流是由柵極流向襯底,PMOS 的柵極漏電流是由襯底流向柵極。

當集成電路器件的特征尺寸進入0.18μm時,柵氧化層的厚度小于3nm,半導體業界利用SiON 代替純二氧化硅作為柵氧化層的介質層的材料。SiON 具有三方面的優點:第一點是SiON具有較高的介電常數,在相同等效柵電容的情況下,SiON 會具有更厚的物理氧化層;第二點是 SiON具有較高的電子絕緣特性,在相同物理厚度的情況下,利用SiON 作為柵氧化層的柵極漏電流大大降低;第三點是 SiON 中的氮元素對PMOS 多晶硅柵極摻雜的硼離子具有較好的阻擋作用,SiON可以防止硼離子在熱退火處理的過程中擴散并越過柵氧化層到達襯底的溝道中影響器件的閾值電壓。

早期生長柵氧化層 SiON 材料是利用爐管預先淀積一層純二氧化硅薄膜,然后再利用原位和非原位熱處理氮化二氧化硅薄膜形成 SiON 薄膜,氮化的氣體是N2O、NO 和NH3中的一種或幾種。這種工藝技術簡單,缺點是摻雜氮元素的含量太少,對硼離子的阻擋作用有限,并且SiON 中的復元素不是均勻分布在柵氧化層中的,它主要分布在靠近SiO2和Si襯底的界面,造成SiO2和Si 襯底之間的界面缺陷,會導致溝道的載流子散射,降低載流子的遷移率。用爐管熱處理氮化得到的氮氧化硅(SiON)主要應用于工藝特征尺寸在0.11μm及以上的工藝技術。

隨著工藝特征尺寸進入90nm 及以下,柵氧化層厚度縮小到2nm 左右,柵極漏電流和硼離子擴假變得越來越嚴重,這就要求作力柵氧化層的氮氧化硅的氮元素含量越來越高,同時使它靠近上表面從而改善SiO2和Si襯底之間的界面。更先進的等離子氮化工藝被應用于生長柵氧化層SiON材料,以提高柵介質層中的氮含量,并較好的控制氮的分布。這種技術也是首先利用爐管預先淀積一層純二氧化硅薄膜,然后利用氮氣和惰性氣體(如氦氣或氬氣)的混合氣體,在磁場和電場感應下產生活性極強的氮等離子體,同時活性極強的氮等離子體會撞擊二氧化硅薄膜表面,形成斷裂的硅氧鍵,活性極強的氮離子會取代部分斷裂的硅氧鍵中的氧的位置,并在后續的熱退火步驟中形成穩定的硅氮鍵,從而使氮元素靠近上表面。

由于MOS器件的柵漏電流與柵氧化層的厚度成指數關系,隨著工藝特征尺寸進入45nm,柵氧化層 SiON的厚度小于2nm,將引起不希望的高柵漏電流,導致整個芯片的待機功耗急劇增加、可靠性問題和柵介質層完整性問題,所以用由SiON 和多晶硅組成的柵極疊層結構已經不能滿足 MOSPET 器件高性能的要求。另外,NMOS 柵極漏電流是柵氧化層物理厚度縮小的主要制約因素,NMOS的柵漏電流是 PMOS柵漏電流的10 倍,因為柵漏電流主要是由載流子的隧穿引起的,而空穴隧穿要通過更高的勢壘。

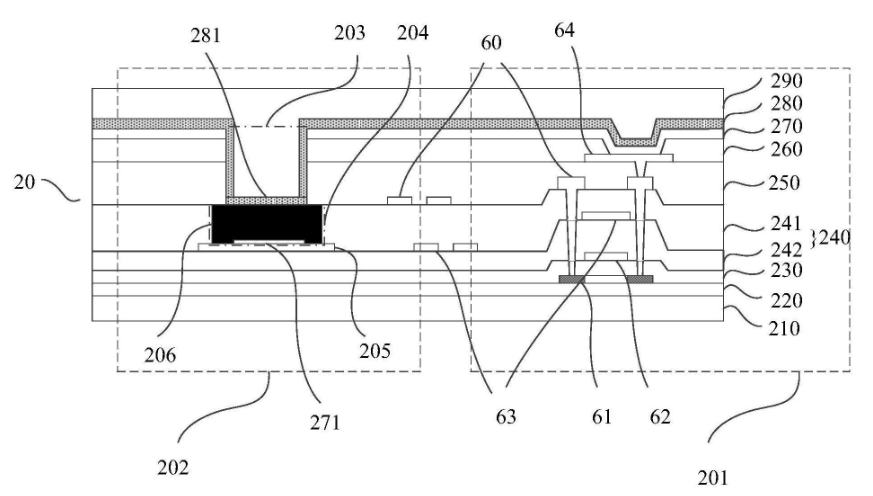

2007年1月,Intel 公司宣布在45nm 技術節點利用新型High-k(高K介電常數)介質材料HfO2,來代替傳統 SiON 作為柵介質層來改善柵極漏電流問題,同時利用金屬柵代替多晶硅柵,開發出HKMG工藝。

-

集成電路

+關注

關注

5387文章

11530瀏覽量

361641 -

MOS管

+關注

關注

108文章

2410瀏覽量

66760 -

NMOS

+關注

關注

3文章

294瀏覽量

34350

原文標題:柵介質層的發展和面臨的挑戰

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

集成電路的發展趨勢與設計挑戰

片式疊層陶瓷介質電容器基礎介紹

【轉】一文看懂MOS器件的發展與面臨的挑戰

分析MOS管未來發展與面臨的挑戰

高介電柵介質材料研究進展

MOSFET柵漏電流噪聲特性、模型的特性和局限性研究分析

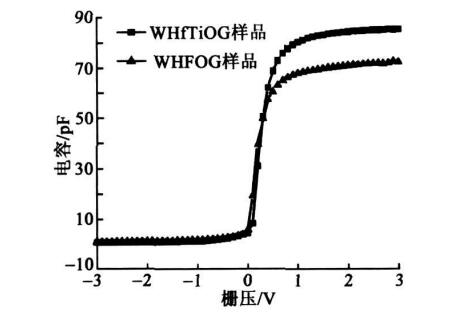

一文讀懂HfTiO高柵介質GeMOS電容

高遷移率二維半導體Bi2O2Se的紫外光輔助插層氧化方法

高K介質(High-k Dielectric)和替代金屬柵(RMG)工藝介紹

高k柵介質NMOSFET遠程聲子散射對溝道遷移率的影響

未來是什么材料的世界?探索介質層材料的新趨勢和挑戰

柵介質層的發展和挑戰

柵介質層的發展和挑戰

評論