要處理CPU亂序調度中的內存數據依賴,通常涉及兩個步驟:

1.計算內存訪問的有效地址

2.檢查所有未處理完的load/store的地址,并確保沖突的load/store不能亂序執行

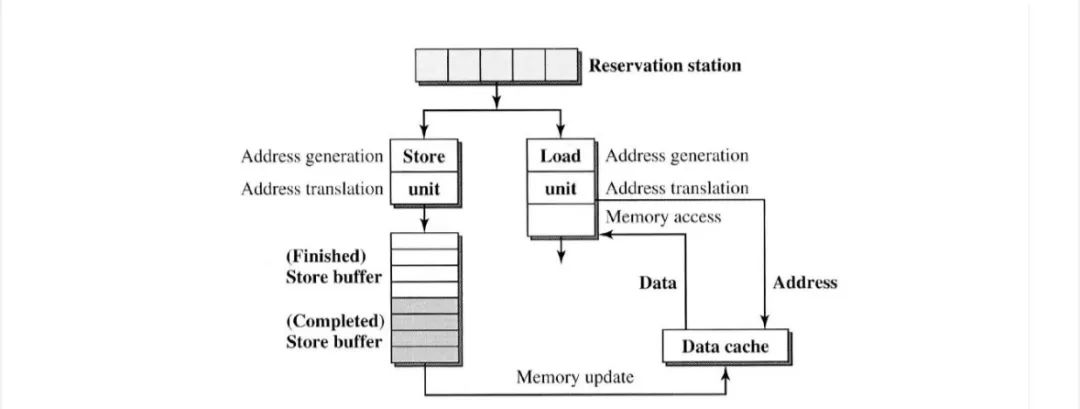

A Load / Store Processing Model

load/store處理模型,如下圖所示。

load和store指令首先發給reservation station ,然后發送到load單元或store 單元。

在store單元中,store 指令首先經過有效的地址計算和地址轉換,然后駐留在“Finished ”store 緩沖區中。 “completed ”store 緩沖區中的store 指令最終會提交到內存中。

同樣,load指令首先通過地址生成和翻譯,并最終讀取數據cache 以從內存中獲取數據。

我們可以做出的一個假設是,store 指令需要按程序順序完成,因此WAW數據依賴性是默認強制執行的。從本質上講,處理數據依賴項可以簡化為處理load/store 依賴項(RAW和WAR)。

Handling Data Dependencies with In-order Load / Store Dispatch

最直接的解決方案是按程序順序向公共reservation station 發出load/store 指令,并從reservation station 按FIFO順序發送。只有當store 緩沖區為空時,才能發送load。然而,load指令的延遲很長,不可預測。盡早執行load至關重要。

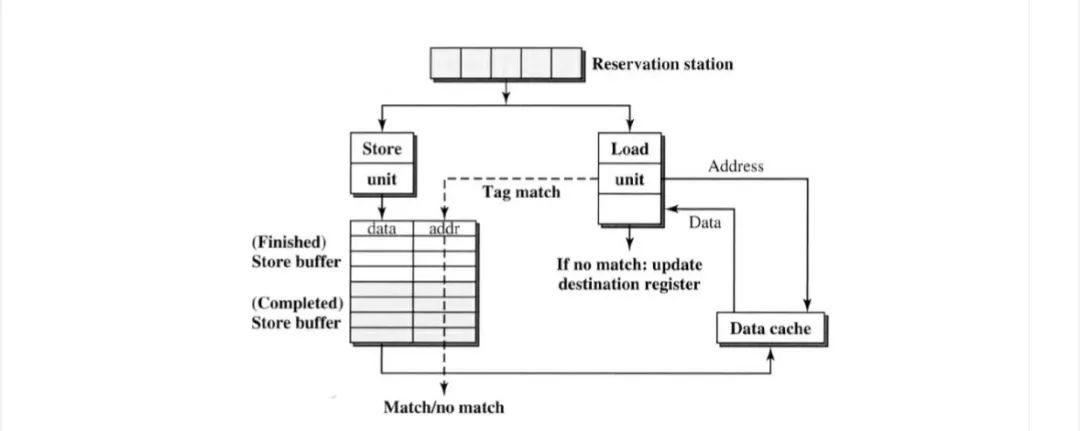

改進的方案是支持不同地址的load bypass ,如果store 緩沖區中有地址匹配,則stall load指令。因此,不同地址的load可以繼續進行。

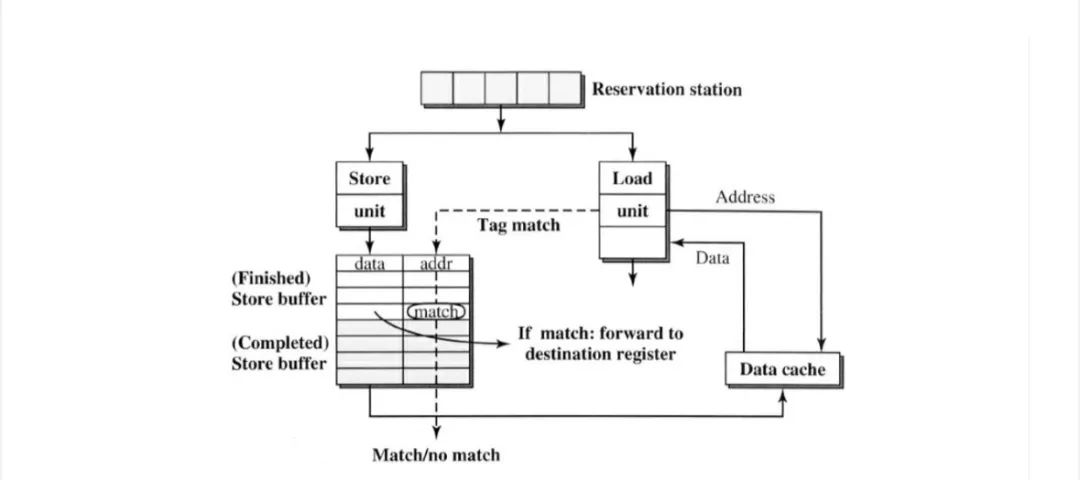

為了進一步加快load。如果存在地址匹配,但store buffer數據不可用,則load stall;如果存在地址匹配和store 數據可用,則將數據直接forward 到load。由于load直接從store buffer接收數據,因此可以盡早執行load指令,并避免數據cache 訪問。

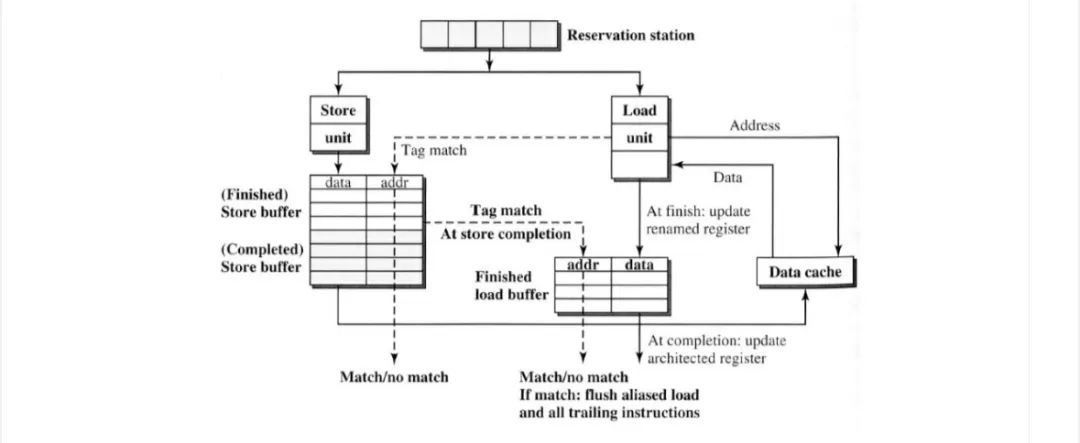

Handling Data Dependencies with Out-of-order Load / Store Dispatch

如果我們亂序調度load/store,可以在store之前發放load。由于無法檢查地址匹配,因此存在潛在的RAW依賴關系。

與store指令類似,如果從reservation station 發送的store在“finished ”load buffer中發現匹配的load,則應刷新所有指令。

這種放松也引入了可能的WAR數據依賴性。load地址可能與后續store的地址匹配,因此會觸發不正確的數據forward 。一個簡單的解決方案是stall 匹配地址的“finished ” store的load,僅具有匹配地址的“completed ”store上數據forward 給load。

-

cpu

+關注

關注

68文章

10854瀏覽量

211583 -

內存

+關注

關注

8文章

3019瀏覽量

74003 -

數據依賴

+關注

關注

0文章

2瀏覽量

5669

原文標題:CPU面試題Q7:如何處理內存中的數據依賴?

文章出處:【微信號:數字芯片實驗室,微信公眾號:數字芯片實驗室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Cjson協議申請不到內存如何處理?

如何處理好FPGA設計中跨時鐘域間的數據

labview寫入access數據庫亂序問題

如何處理存儲在非易失性設備中的內存數據集損壞

如何處理才能使CPU的效率更高呢?

stm32如何處理數組中數據

如何處理cpu風扇轉速過快

小型Hadoop集群的數據分層調度處理算法分析

基于GPU/CPU的流程序多粒度劃分與調度

證明CPU指令是亂序執行的

當我們在談論cpu指令亂序的時候,究竟在談論什么?

如何處理CPU亂序調度中的內存數據依賴

如何處理CPU亂序調度中的內存數據依賴

評論