SIC的作用機理

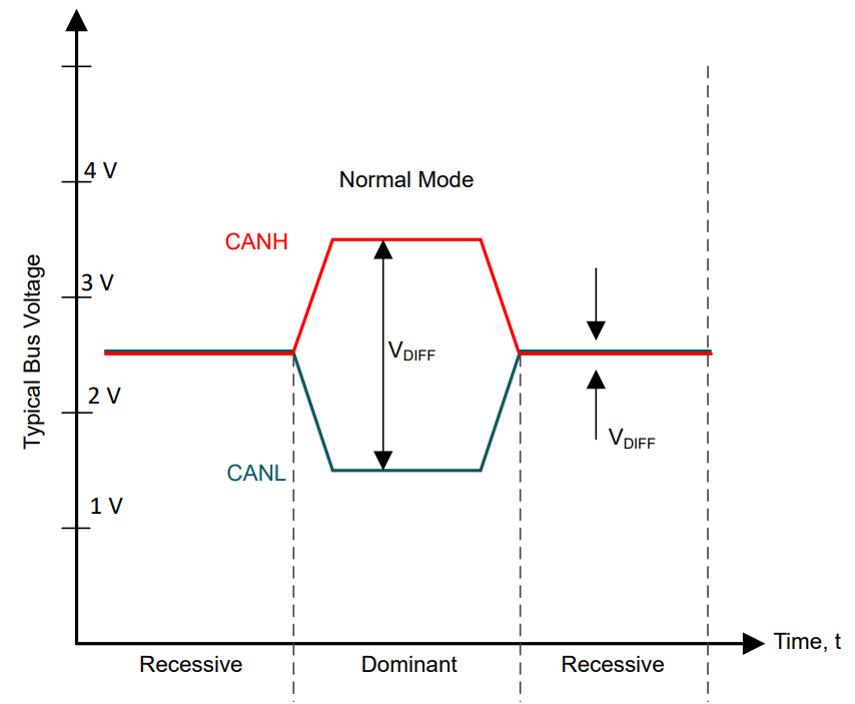

在CAN總線上,通過CAN_H和CAN_L兩根線上的電位差來表示CAN信號。CAN總線上的電位差分為兩種:顯性電平(Dominant Voltage)和隱性電平(Recessive Voltage),其中顯性電平為邏輯0,隱性電平為邏輯1,如下圖所示。

CAN總線電壓電平

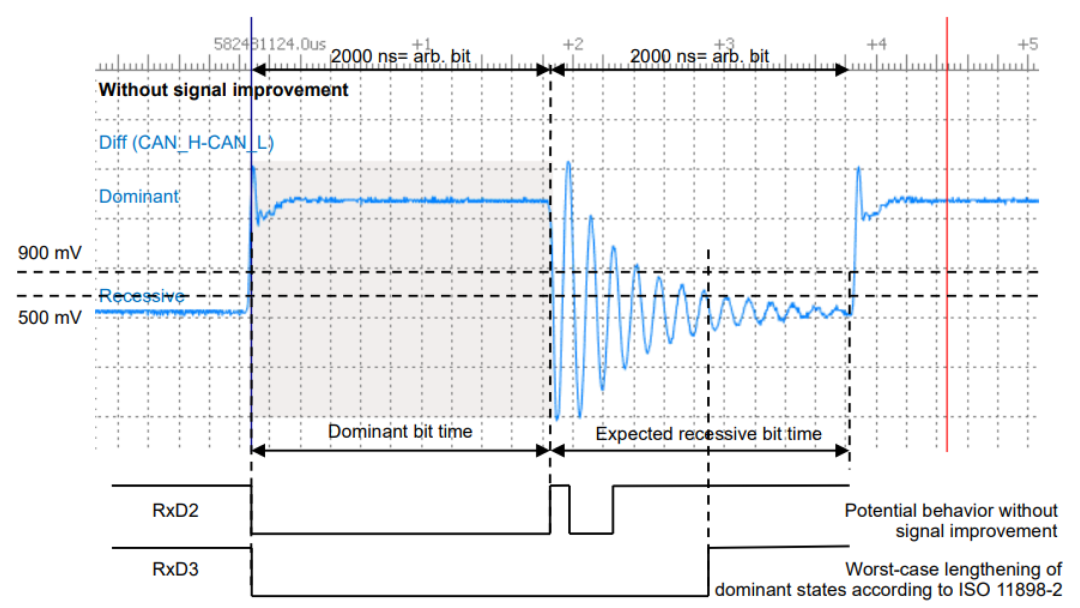

當TXD輸出邏輯0時,總線輸出的差分電壓VDIFF為顯性狀態,當TXD輸出邏輯高電平時總線通過接收器內部的高阻值輸入電阻器 (RIN)偏置為VCC/2,為隱性狀態,在仲裁期間,顯性狀態會覆蓋隱性狀態。CAN收發器在顯性階段的差分發送器輸出阻抗約為50Ω,與總線特征阻抗緊密匹配,通常不會引起信號反射。對于常規CAN FD收發器,當驅動器輸出顯性電平切換到隱性電平時,差分輸出阻抗會由50Ω變為約60kΩ,此時,反射回來的信號遇到端口的阻抗不匹配,并且這些反復的反射疊加在輸出端口,從而導致了信號振鈴的產生。

CAN總線振鈴波形

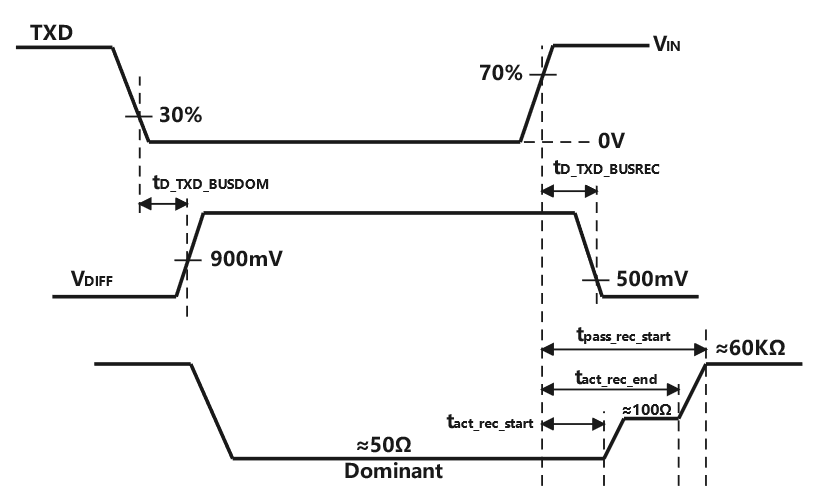

對于具有SIC功能的CAN芯片而言,當發送器檢測到TXD上出現從顯性到隱性的邊沿時,內部驅動器會激活振鈴抑制(SIC)電路。CAN驅動器繼續強力驅動總線至隱形電平,直至tpass_rec_start,以便減少反射,確保采樣點處的隱性位很干凈。在這一主動隱性階段,發送器輸出阻抗較低(約為100Ω)。反射的信號沒有遇到顯著的阻抗不匹配,并且驅動電阻可有效吸收反射信號,因此振鈴會大大減弱。在該階段結束后驅動器進入被動隱性階段,其輸出阻抗上升至約60kΩ。

CAN SIC阻抗時序圖

在SIC作用的主動隱性階段,其持續時間最長可達530ns(tpass_rec_start,如上文所列)。由于CAN FD協議的數據階段最低位寬為200ns(5Mbps),因此振鈴抑制可在整個的隱性位持續時間內保持活動狀態,從而保證CAN總線和RXD信號的翻轉正常進行。

SIC芯片對于組網的優勢

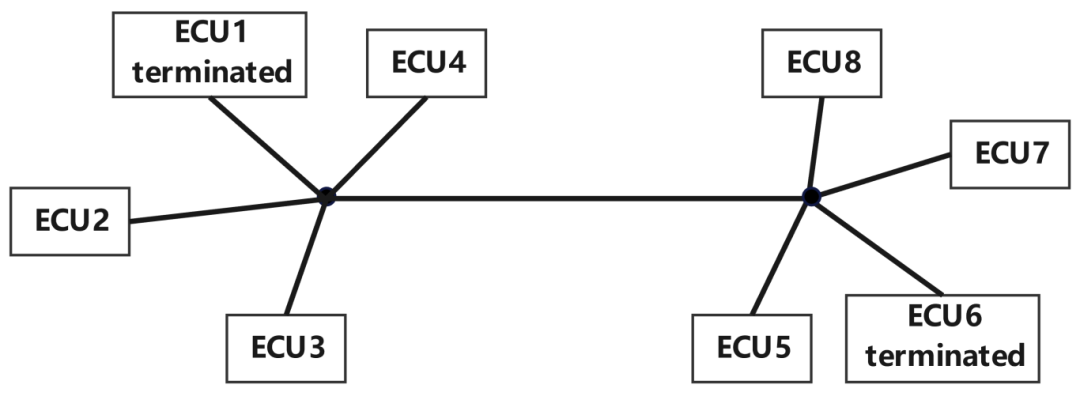

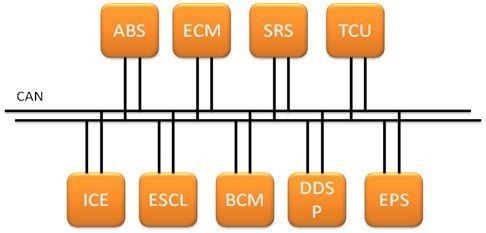

相比常規CAN芯片,CAN SIC可采用更為靈活的組網方式,如下圖所示;常規CAN芯片由于信號振鈴的限制,為了保證CAN FD的高速率要求,所有節點需采用手拉手的菊花鏈組網方式,且每個節點的分支線纜不超過0.3m,采用SIC芯片后可靈活調整組網方式和提高總線速率上限,可根據實際應用場景進行布線,有效節省組網線材成本和車身重量。

常規CAN組網方式

在常規組網環境中在若出現某一節點斷開時,信號會因為斷開節點后留下的分支線導致信號振鈴,若是使用常規CAN芯片該振鈴無法避免,易導致節點收到錯誤幀,如果其中一個終端異常斷開的話,基本很難保證總線通信了,若是使用CAN SIC芯片可抑制信號振鈴,可保證信號在異常場景下正常通信。

CAN SIC組網方式

CAN SIC收發器有更嚴格的位時間對稱性,這使得CAN信號在惡劣的組網環境中能夠提供更多裕量。收發器對上升沿和下降沿的斜率要求更快,可保證單bit的有效位寬,因此可以以8Mbps的速率可靠運行。與CAN FD收發器相比,其SIC的環路延時最大僅為190ns,遠低于CAN FD收發器的255ns最大環路延時的要求,更有助于延長最大組網長度。

TPT1462

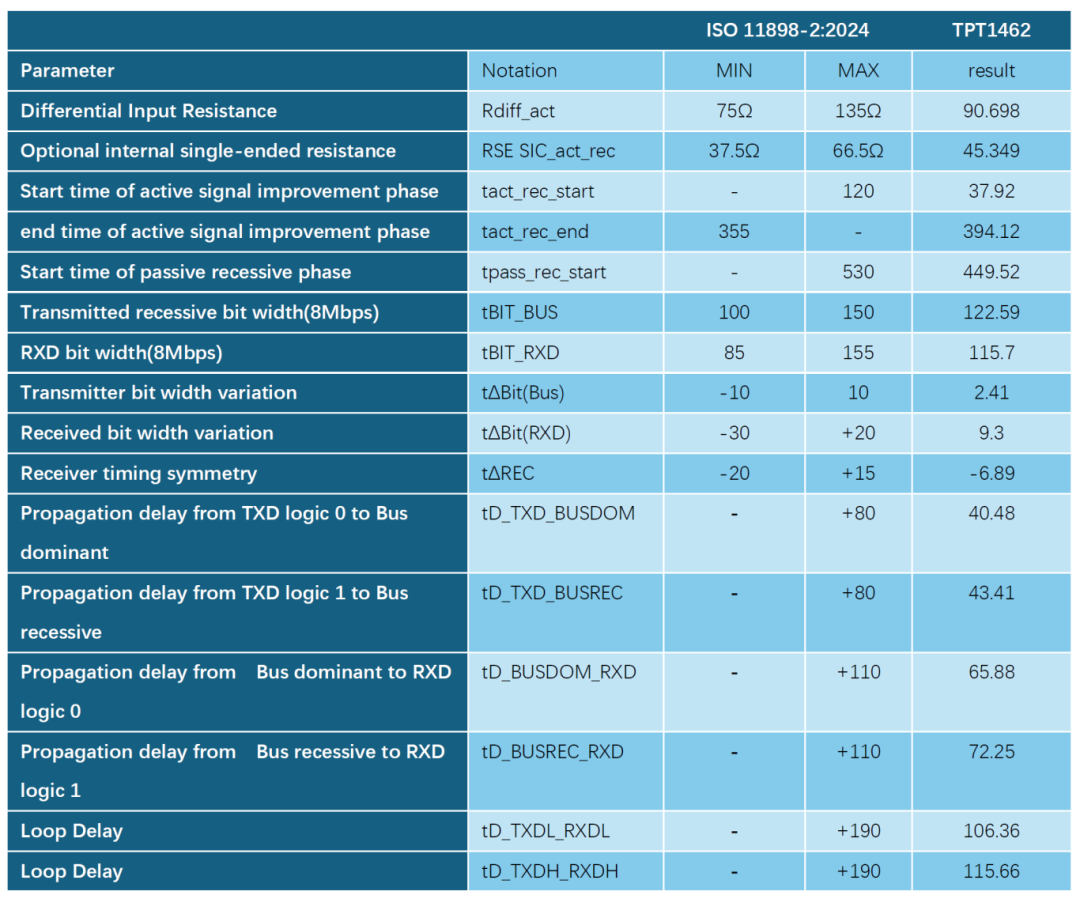

思瑞浦推出基于其自主創新設計振鈴抑制電路專利的車規級CAN SIC(信號改善功能,Signal Improvement Capability)TPT1462Q芯片,相比當前主流的CAN FD車載通信方案,TPT1462Q滿足最新的ISO 11898-2:2024標準(見下表),同時兼容CiA 601-4標準,可實現≥8Mbps的傳輸速率。可與常規CAN FD的CAN芯片(TPT1044/TPT1042)兼容和混合組網,還具有待機模式和遠程喚醒功能,此外其優異的EMC表現,以及靈活的VIO供電選擇(低至1.8V)可有效助力工程師簡化系統設計、并打造更高質量的車載通信系統。

表1、TPT1462關于ISO 11898-2:2024標準測試數據

在工況復雜的汽車應用中,環境中惡劣的電磁干擾可通過電纜耦合到芯片的CAN總線,這可能導致CAN芯片傳輸異常,甚至導致芯片損傷。思瑞浦推出的CAN SIC芯片TPT1462Q具有國際領先的抗干擾能力,為汽車安全通訊奠定堅實的基礎;此外TPT1462Q采用思瑞浦自主設計對稱性調節模塊專利技術,用于調節第一輸出驅動級和第二輸出驅動級的對稱性;借助于該對稱性調節模塊,確保差分輸出級的對稱性,優化芯片的EMI性能,依照IEC 62228-3標準進行傳導發射的EME測試,表現如下:

無共模電感時TPT1462Q的EME測試圖

TPT1462實戰效果

總線振鈴一般是CAN總線的通信過程中,由于阻抗不匹配導致的信號反射等原因,使得信號在傳輸線上多次反射,進而產生的一種振蕩現象。振鈴現象可能會對CAN總線的通信質量產生負面影響,甚至有可能導致通信失敗。TPT1462Q采用自研的振鈴抑制專利,允許工程師在多節點、復雜拓撲情況下有效減少總線中的信號反射,降低振鈴現象發生的概率(如下圖)。

常規CAN-FD在星型網絡多節點通信波形

CAN SIC芯片在星型網絡多節點通信波形

同時由于架構的優化TPT1462Q可維持高達10Mbps的通信傳輸速率,并且可保證優質的總線對稱性,大幅提升車載通信質量,為下一代CAN技術發展奠定基礎。

在10Mbps通信速率下的波形

TPT1462產品系列提供帶VIO(TPT1462VQ)與不帶VIO(TPT1462Q)兩個版本,可根據系統需求靈活選擇簡化系統設計,提供SOP8和DFN8兩種封裝,可Pin-to-Pin兼容市場主流經典CAN和CAN FD收發器。TPT1462Q已通過AEC-Q100車規認證要求,支持–40°C~125°C的寬工作溫度范圍,提供過溫保護;同時,TPT1462Q還具備TXD顯性超時保護,待機模式下支持遠程喚醒。此外,該產品的VIO設計可低至1.8V,這一設計不僅提高了產品的靈活性,還可進一步減少系統中對LDO或電平轉換器的需求,從而為工程師在成本控制方面提供有力支持。

-

收發器

+關注

關注

10文章

3660瀏覽量

107479 -

CAN

+關注

關注

57文章

2895瀏覽量

466893 -

通信

+關注

關注

18文章

6182瀏覽量

137424 -

SiC

+關注

關注

31文章

3171瀏覽量

64530

發布評論請先 登錄

降低隔離式CAN收發器有什么作用?

基于MCP2561/2下的高速 CAN 收發器

茂睿芯通用CAN MCAN1042:高性能、低功耗的CAN收發器

SIT1145AQ CAN FD收發器特點 SIT1145AQ CAN FD收發器工作模式

汽車CAN收發器的作用、原理及構成

CAN SIC收發器助力復雜CAN網絡高效可靠通信(1)

評論