主從觸發器(又稱為脈沖觸發器)和邊沿觸發器在波形上的比較主要體現在它們的觸發方式和輸出響應上。以下是對兩者波形比較的具體分析:

一、觸發方式

- 主從觸發器 :

- 邊沿觸發器 :

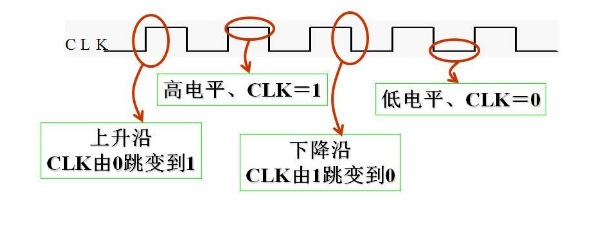

- 邊沿觸發器僅在時鐘信號的約定邊緣(如上升沿或下降沿)到來時接收輸入信號,并更新其輸出狀態。

- 在時鐘信號的其他階段(如高電平或低電平期間),邊沿觸發器不響應輸入信號的變化。

- 邊沿觸發器的輸出狀態變化直接由時鐘信號的邊緣和此時的輸入信號共同決定。

二、波形特性

- 主從觸發器 :

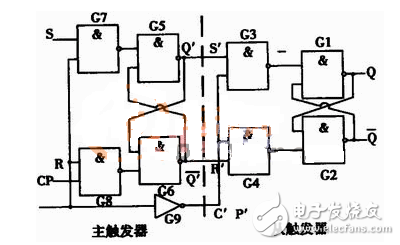

- 主從觸發器的波形圖通常顯示出兩個階段的特征:主觸發器接收信號階段和從觸發器更新輸出階段。

- 在CLK為高電平時,主觸發器的輸入變化可能會被檢測到,但這些變化不會立即反映到輸出上。

- 直到CLK的邊緣到來,從觸發器才根據主觸發器的狀態更新其輸出,這可能導致輸出波形相對于輸入信號有一定的延遲。

- 邊沿觸發器 :

- 邊沿觸發器的波形圖更加直接地反映了輸入信號和時鐘信號邊緣之間的關系。

- 當時鐘信號的邊緣到來時,邊沿觸發器立即根據此時的輸入信號更新其輸出狀態。

- 由于邊沿觸發器只在時鐘信號的邊緣時刻接收輸入信號,因此它的輸出波形通常更加清晰、穩定,且沒有不必要的延遲。

三、抗干擾能力

- 邊沿觸發器通常比主從觸發器具有更強的抗干擾能力。這是因為邊沿觸發器只在時鐘信號的邊緣時刻接收輸入信號,這大大減少了輸入端受干擾的時間窗口。相比之下,主從觸發器在CLK為高電平時都會接收輸入信號,這使得它更容易受到輸入端干擾的影響。

綜上所述,主從觸發器和邊沿觸發器在波形上的主要區別在于它們的觸發方式和輸出響應特性。邊沿觸發器由于只在時鐘信號的邊緣時刻接收輸入信號并更新輸出狀態,因此通常具有更強的抗干擾能力和更穩定的輸出波形。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

主從觸發器

+關注

關注

0文章

13瀏覽量

6508 -

輸入信號

+關注

關注

0文章

472瀏覽量

12839 -

時鐘信號

+關注

關注

4文章

465瀏覽量

29083 -

邊沿觸發器

+關注

關注

0文章

34瀏覽量

4136

發布評論請先 登錄

相關推薦

熱點推薦

主從觸發器,主從觸發器的原理和特點有哪些?

主從觸發器,主從觸發器的原理和特點有哪些?

1.電路組成和符號 主從RS觸發器電路和邏輯符號如圖Z1406所示。其中A、

發表于 03-08 14:06

?1.2w次閱讀

邊沿觸發器波形圖

主從觸發器可以有效克服鐘控觸發器的空翻現象,但主從觸發器還存在一次翻轉現象,降低了抗干擾能力。邊沿觸發器:只有在CP的上升沿(前沿)或下降沿

發表于 01-31 10:38

?2.5w次閱讀

主從rs觸發器波形圖介紹

主從觸發器由主觸發器和從觸發器組成,時鐘信號CP經由非門,變成CP’控制從觸發器。當CP=1時,CP‘=0,主觸發器動作,從

發表于 02-08 13:40

?2.2w次閱讀

主從觸發器和邊沿觸發器的區別是什么

主從觸發器(Master-Slave Trigger)和邊沿觸發器(Edge Trigger)是數字電路中兩種不同類型的觸發器。它們在設計和功能上有一些關鍵的區別:

主從觸發器都是下降沿觸發嗎

主從觸發器(Master-Slave Flip-Flop)是一種常見的數字邏輯電路,用于存儲一位二進制信息。主從觸發器通常由兩個觸發器組成,一個作為主觸發器,另一個作為從

主從觸發器和同步觸發器的區別在哪里

定義: 主從觸發器(Master-Slave Trigger)是一種用于實現時鐘同步的觸發器結構,它由兩個觸發器組成,一個為主觸發器(Master Trigger),另一個為從

主從觸發器和脈沖觸發器的區別是什么

主從觸發器和脈沖觸發器是數字電路中常見的兩種觸發器類型,它們在邏輯功能、電路結構、工作原理等方面存在一些區別。 定義和功能 主從觸發器(Master-Slave Flip-Flop)是

主從觸發器和邊沿觸發器的特點及應用

在數字電路設計中,觸發器是一種非常重要的基本邏輯元件,用于存儲一位二進制信息。觸發器的種類繁多,但主要分為兩大類:主從觸發器(Master-Slave Flip-Flop)和邊沿

主從觸發器和邊沿觸發器的區別

主從觸發器和邊沿觸發器是數字電路設計中常用的兩種觸發器類型,它們在觸發機制、動作特點、應用場景等方面存在顯著的區別。以下是對兩者區別的詳細闡

主從jk觸發器和邊沿jk觸發器的區別

主從JK觸發器和邊沿JK觸發器是數字電路中常用的存儲元件,它們在功能和應用上既有相似之處,也存在顯著的區別。以下將從多個方面介紹這兩種觸發器

評論