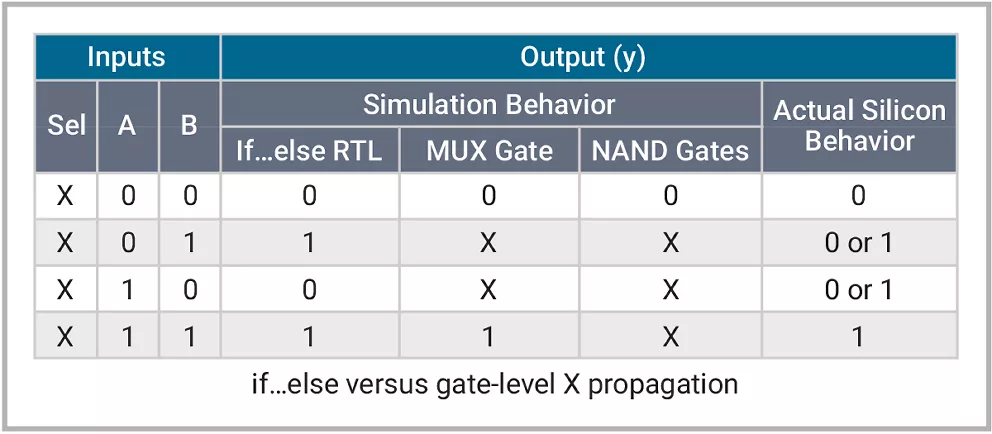

造成調(diào)試?yán)щy的因素有很多,其中包括取值未知(“X”)的情況。X是VHDL、Verilog、SystemVerilog等邏輯標(biāo)準(zhǔn)所定義的眾多邏輯值之一,可以代表1、0或Z,也就是說X的值是未知的,從而能夠預(yù)示設(shè)計(jì)或驗(yàn)證環(huán)境邏輯仿真中邏輯信號(hào)的不確定性。讓事情變得更加復(fù)雜的是,在RTL和Gate仿真中,X的不確定性是各有不同。默認(rèn)情況下,RTL邏輯仿真器的處理方式較為樂觀,也就是允許X在邏輯上被阻塞。舉一個(gè)比較典型的例子,多路復(fù)用器的選擇信號(hào)具有X值時(shí),這個(gè)X值是否會(huì)被傳播取決于其建模方式。具體請參閱下表。

▲圖1 該表格最初發(fā)表于一篇題為“I’m Still In Love with My X!”的DVCon 2013會(huì)議論文,作者是Sutherland HDL。

請重點(diǎn)留意在建模中如何確定仿真器是否允許多路復(fù)用器傳遞0、1或X值。請注意,在實(shí)際芯片中,信號(hào)值始終為1(高電壓)或0(低電壓)。

那么,為什么要關(guān)注這種樂觀的處理方式呢?

寬松的處理方式可能隱藏著一些潛在的設(shè)計(jì)缺陷。在上述表格中,如果Sel輸入未連接,則芯片電路的電氣行為將變得不可預(yù)測。如果預(yù)計(jì)輸出為1,但出現(xiàn)的是0,則實(shí)際的芯片電路可能不穩(wěn)定,需要重置多次才能獲得所需的值1。

門級(jí)仿真傾向于在技術(shù)邏輯單元中使用支持傳遞X值的機(jī)制(或邏輯表),因此與芯片值的相關(guān)性更大。X值的傳播讓用戶能夠在制造芯片之前發(fā)現(xiàn)一些不良行為。

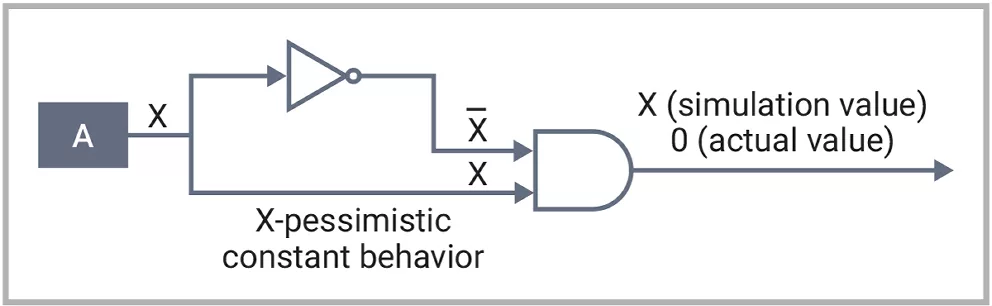

除了像RTL仿真中那樣因較寬松的傳播行為而阻塞X值之外,還存在一些場景,其中X值不應(yīng)該被傳播。就拿下圖這個(gè)簡單的例子來說:

無論模塊A輸出端的X值如何,邏輯本身應(yīng)始終在與門(AND)的輸出端生成0。在這種情況下,邏輯結(jié)構(gòu)的建模/仿真處理就過于悲觀了。雖然在這種邏輯結(jié)構(gòu)的輸出端上調(diào)試X值對于開發(fā)者來說有點(diǎn)浪費(fèi)時(shí)間,但對這種設(shè)計(jì)結(jié)構(gòu)類型加以了解將十分受用。

為什么很難找到X?

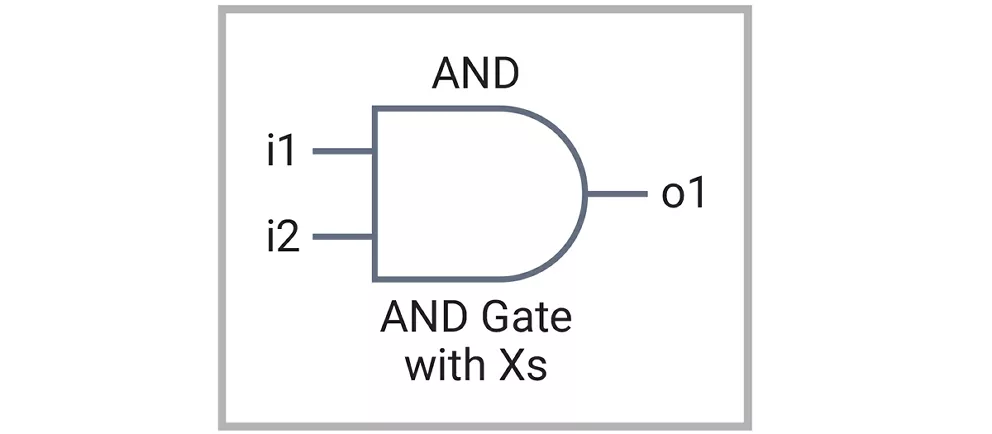

無論X在RTL或門級(jí)仿真中如何傳播,幾乎所有X都難以進(jìn)行調(diào)試。為什么會(huì)這樣?首先,產(chǎn)生X的根本原因或來源可能有很多。例如,某個(gè)邏輯門具有X輸入(非驅(qū)動(dòng));存儲(chǔ)器或觸發(fā)器未初始化為已知值;或是觸發(fā)器違反了建立時(shí)間或保持時(shí)間的規(guī)定,都有可能產(chǎn)生X。下圖是一個(gè)簡單的例子:就像這個(gè)與門,有一個(gè)X和同時(shí)有多個(gè)X的情況都很常見。輸入端i1和i2上的X導(dǎo)致輸出端o1輸出X。

當(dāng)輸入端出現(xiàn)多個(gè)X時(shí),用戶需要選擇其中一個(gè)作為調(diào)試X的起點(diǎn),然后反復(fù)回溯到所關(guān)注信號(hào)的驅(qū)動(dòng)源或扇入信號(hào),直到能夠找出最早出現(xiàn)的X值或根本原因。而當(dāng)所關(guān)注的信號(hào)或根本原因信號(hào)不是造成X值的唯一原因時(shí),用戶需要選擇另一輸入X來追蹤其根本原因。找到的第二個(gè)根本原因可能與前一個(gè)錯(cuò)誤的根本原因相同,也可能是另一個(gè)來源。這是造成X難以調(diào)試且費(fèi)時(shí)費(fèi)力的關(guān)鍵原因之一。

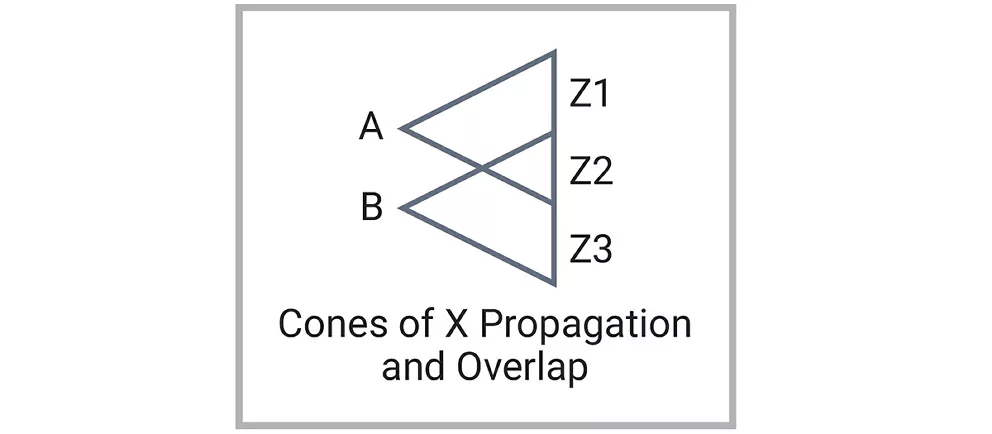

此外,X通常要在設(shè)計(jì)中傳播數(shù)千個(gè)RTL語句或門級(jí)邏輯,才能到達(dá)觀察點(diǎn)、調(diào)試入口點(diǎn)或輸出端口。當(dāng)然,這要取決于具體部署的環(huán)境類型、模塊級(jí)別、芯片級(jí)別或SoC。單個(gè)根本原因也可能傳播到多個(gè)觀察點(diǎn)。此外,這些根本原因和觀察點(diǎn)的邏輯錐可能交織在一起。各種因素盤根錯(cuò)節(jié),使得追蹤X難上加難。下圖說明了X態(tài)傳播和輸出端上X重疊的概念。輸出Z1僅接收到輸入A,輸出Z3僅接收到輸入B,但輸出Z2卻能接收到輸入A和輸入B。

這個(gè)追蹤過程需要多次迭代操作,非常繁瑣。此外,還需要了解來源/根本原因的類型。例如,系統(tǒng)可能有意設(shè)置了一個(gè)尚未重置或賦值的內(nèi)存數(shù)組,而某個(gè)地址可能錯(cuò)誤地指向了這個(gè)未初始化的數(shù)組。所以追蹤這個(gè)數(shù)組并理解這個(gè)地址的邏輯也非常關(guān)鍵。話雖如此,是否有一種方法可以自動(dòng)追蹤X的根本原因,并且在確定了根本原因后,對這些X進(jìn)行分類或解釋原由?這種自動(dòng)化將大大節(jié)省開發(fā)工作量,并大幅提升開發(fā)者的工作效率。

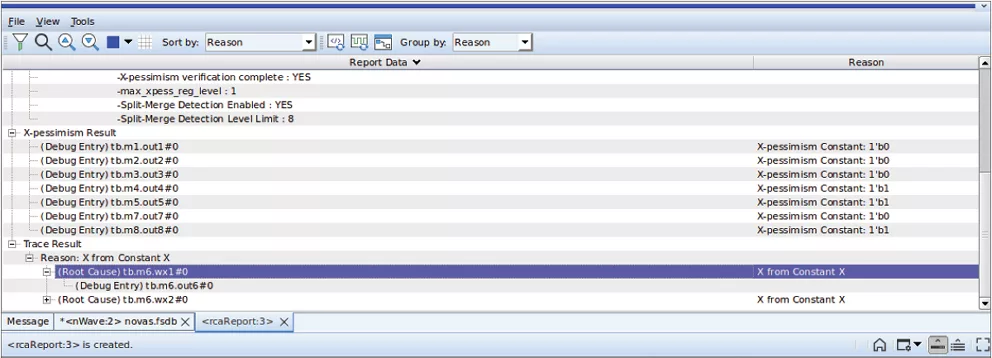

新思科技Verdi的XRCA組件

新思科技Verdi回歸調(diào)試自動(dòng)化的XRCA組件是一種先進(jìn)的根本原因分析工具,恰好能夠滿足上述自動(dòng)化要求。XRCA是追蹤X和進(jìn)行根本原因分析的出色引擎,不僅可以自動(dòng)掃描FSDB中的X信號(hào)并追蹤X信號(hào)的根本原因,而且可以批量處理大量X信號(hào)以縮短調(diào)試時(shí)間。此外還能生成邏輯清晰的報(bào)告,按不同類別列出根本原因。報(bào)告會(huì)加載到新思科技Verdi的RCA主設(shè)備中,以便觀察結(jié)果和追蹤路徑。

XRCA是在啟動(dòng)門級(jí)仿真和進(jìn)行回歸處理時(shí)調(diào)試X信號(hào)的理想工具。除了許多根本原因分類之外,XRCA還支持門級(jí)網(wǎng)表追蹤、RTL級(jí)追蹤、新思科技VCS X態(tài)傳播追蹤、低功耗組件X追蹤,以及X值悲觀處理檢測。

-

調(diào)試

+關(guān)注

關(guān)注

7文章

613瀏覽量

34770 -

RTL

+關(guān)注

關(guān)注

1文章

390瀏覽量

61198 -

多路復(fù)用器

+關(guān)注

關(guān)注

9文章

930瀏覽量

66111 -

新思科技

+關(guān)注

關(guān)注

5文章

872瀏覽量

51591

原文標(biāo)題:令人痛苦的X!為什么調(diào)試X那么困難?

文章出處:【微信號(hào):Synopsys_CN,微信公眾號(hào):新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評(píng)論請先 登錄

調(diào)試讀取發(fā)送狀態(tài)寄存器的值一直為0x1E是怎么回事

HCS12(X)仿真與調(diào)試資料

多核軟件調(diào)試方法與困難

C2837x入門:系統(tǒng)的調(diào)試仿真

iPhone 12系列真有那么值嗎

電路調(diào)試的步驟、注意事項(xiàng)及故障解決沒那么簡單!

評(píng)論