在電子系統(tǒng)設(shè)計(jì)中,無任是用CPU作為系統(tǒng)的主要器件,還是用FPGA作為系統(tǒng)的主要器件,系統(tǒng)設(shè)計(jì)中首先要考慮到的問題就是處理器的啟動(dòng)加載問題。 XILINX推出的ZYNQ可擴(kuò)展處理平臺(tái),片內(nèi)包括兩個(gè)高性能的ARM Cortex A9硬核(稱為處理系統(tǒng)processing system (PS))和FPGA(稱為可編程邏輯programmable logic (PL)),在基于該平臺(tái)的系統(tǒng)設(shè)計(jì)時(shí)具有極大的靈活性,本文就ZYNQ系統(tǒng)設(shè)計(jì)時(shí)都會(huì)遇到啟動(dòng)加載問題作一個(gè)拋磚引玉的描述,如有不當(dāng)之處還請(qǐng)高手斧正。

一、器件配置單元

ZYNQ器件都帶有一個(gè)器件配置單元(device configuration unit (DEVCFG) ),該模塊由PS控制,提供軟件控制下的PS和PL的初始化和配置功能。以前單個(gè)FPGA器件提供的下載方法已經(jīng)不在適用,PL的配置下載必須在PS的參與下進(jìn)行。

Zynq-7000的器件配置單元包括下面的PS單元:

① CPU

② OCM(引導(dǎo)ROM和共享RAM)

③ 部分頂層總線和外設(shè)

④ PS器件配置模塊

在PL側(cè),下面的單元也將參與:

① PLS器件配置邏輯和接口

② 解密/鑒權(quán)硬件

③存儲(chǔ)在eFUSE單元或者電池備份RAM(BBRAM)內(nèi)的解密密鑰

下圖為PS器件配置子系統(tǒng)框圖:

提供的關(guān)鍵特性如下:

A.提供3種不同的PS配置方法,包括2種主模式和1種從模式。

① 加密主模式

② 非加密主模式

③ 非加密從模式

B.3種不同的主模式啟動(dòng)源

① NOR FLASH

② NAND FLASH

③ QSPI FLASH

C:JTAG非加密從模式

D:用AES-256和HMAC (SHA-256)進(jìn)行PS/PL的加密下載

E:高速配置用的主DMA接口

F:100 MHz 32-bit PCAP流接口

H:SoC加密調(diào)試功能

在系統(tǒng)上電復(fù)位時(shí),PS采樣專用bootstrapping signals引腳電平來決定從什么方式引導(dǎo)器件。這個(gè)引導(dǎo)過程是由一個(gè)Cortex A9核執(zhí)行片內(nèi)的ROM code實(shí)現(xiàn)的,ROM code的功能是初始化L1 cache和基本的總線系統(tǒng),加載相應(yīng)的NAND, NOR, Quad-SPI, and PCAP驅(qū)動(dòng),從指定接口加載第一級(jí)BOOTLOADER(the first stage boot loader (FSBL))到片內(nèi)執(zhí)行。由于OCM RAM大小有限制,第一級(jí)BOOTLOADER大小最大為256KB。用戶只需要按要求提供啟動(dòng)映像和設(shè)置正確的bootstrapping signals引腳電平,系統(tǒng)上電復(fù)位時(shí)由ROM code自動(dòng)加載到片內(nèi)并且程序調(diào)轉(zhuǎn)到啟動(dòng)映像,此時(shí)系統(tǒng)的全部控制功能交由用戶的啟動(dòng)映像控制,用戶如要實(shí)現(xiàn)的第二級(jí)BOOTLOADER功能由啟動(dòng)映像的程序?qū)崿F(xiàn)。

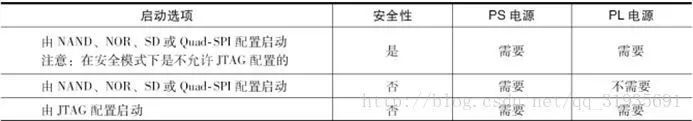

對(duì)于加密配置方法,需要用到AES-256解密代碼和SHA-256簽定(簽名)算法, PS需要用PL內(nèi)硬連線的AES-256 和SHA-256模塊,這時(shí)就要求在加密配置情況下PL就必須上著電,既使系統(tǒng)并不配置PL部分也需上電。器件的加密密鑰可以由用戶選擇是存儲(chǔ)在片內(nèi)的eFUSE單元(具有掉電非易失性)或者內(nèi)部電池供電的BBRAM內(nèi)(具有掉電易失性,適用于安全級(jí)別要求更高的場合), 下表總結(jié)了配置模式和相關(guān)信息:

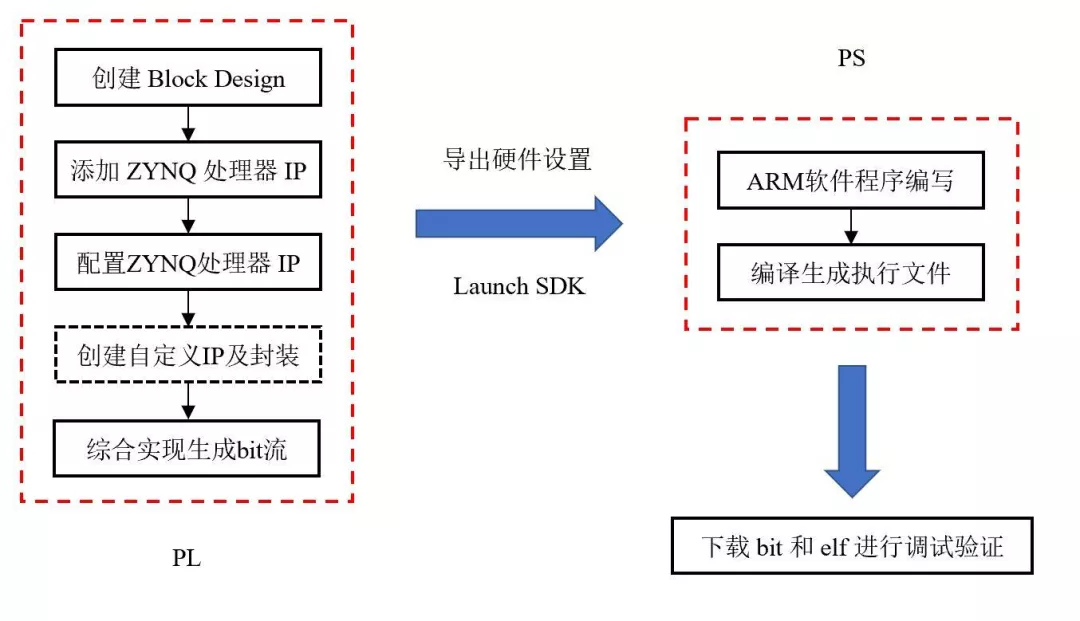

二、PS非加密主模式配置過程

這種模式下PS啟動(dòng)映像是直接從外部非易失存儲(chǔ)器(NAND, NOR, Quad-SPI)內(nèi)加載到片內(nèi)OCM內(nèi),隨后PL映像可以直接配置到PL內(nèi),整個(gè)過程如下圖示:

PL映像的配置可由配置接口模塊用DMA來高速實(shí)現(xiàn),在非加密情況下速度可以達(dá)到400MB/s, 加密情況下速度可以達(dá)到100MB/s, 這在FPGA需要部分重配置時(shí)十分有用。

三、PS加密主模式配置過程

PS加密主模式用到了位與片內(nèi)PL部分的硬件AES-256解密模塊和SHA-256模塊來對(duì)PS啟動(dòng)映像進(jìn)行解密和完整性鑒定,器件密鑰存儲(chǔ)在片內(nèi)的eFUSE單元或者內(nèi)部BBRAM內(nèi),當(dāng)PS加載成功后,用戶可以選擇用下面缺省的PL引導(dǎo)過程來配置PL部分,如下圖示:

其中配置PL時(shí)的比特流既可以是已經(jīng)經(jīng)過AES-256加密的比特流,也可以是先經(jīng)過PS先進(jìn)行解密后成為明文比特流送到PL內(nèi),這個(gè)過程的保密性由用戶選擇使用。

在保密ROM引導(dǎo)階段如果PS完整性鑒定失敗,CPU就立即斷言PROG_B信號(hào)而清除PL內(nèi)容,同時(shí)發(fā)出一個(gè)加密復(fù)位信號(hào),這使PS內(nèi)部的RAM和寄存器進(jìn)行復(fù)位,然后CPU進(jìn)入睡眠模式,系統(tǒng)只有重復(fù)上電才能復(fù)位。PL配置發(fā)生在BOOT的第二階段,這個(gè)過程完成可以由用戶選擇自己的方法在任何時(shí)間內(nèi)來配置一次或多次,并不需要一定按缺省的PL引導(dǎo)過程來配置PL部分。

四、啟動(dòng)模式引腳

ZYNQ器件有5個(gè)啟動(dòng)模式信號(hào)mode[4:0],用來指出從哪里啟動(dòng),是否是JTAG模式,PLL是否旁路等。另外有兩個(gè)電壓模式信號(hào)vmode[1:0]用來指明MIO BANK的電壓模式,vmode[1:0] 信號(hào)和mode[4:0] 信號(hào)通過上拉和下拉來確定電平值,上拉和下拉電阻建議為20k歐姆,上拉是連接到VCCO_MIO0電壓,下拉是連接到地。系統(tǒng)在釋放PS_POR_B復(fù)位腳后這些啟動(dòng)模式引腳信號(hào)會(huì)被采樣3個(gè)PS_CLK時(shí)鐘用來確定啟動(dòng)方式。vmode[1:0] 信號(hào)和mode[4:0] 信號(hào)對(duì)應(yīng)的I/O管腳為MIO[8:2],各信號(hào)具體含義如下:

① Mode[0] 用來指明是否是JTAG 模正。

② Mode[3:1]用來選擇啟動(dòng)源,是從NOR Flash還是從NAND Flash還是從QSPI啟動(dòng)。

③ Mode[4]用來使能PLL。

④ Vmode[1:0] 用來配置I/O BANK電壓。

這些信號(hào)和MIO管腳的對(duì)應(yīng)關(guān)系如下表表示:

注:上表中X表示不關(guān)心。

實(shí)際設(shè)計(jì)中,由于MIO管腳數(shù)量有限(只有54個(gè)),且只分為兩個(gè)BANK(MIO Bank 0對(duì)應(yīng)管腳為PS_MIO[15:0],PS_CLK,PS_POR_B;MIO Bank 1對(duì)應(yīng)管腳為PS_MIO[53:16],PS_VREF_MIO和PS_SRST_B),并不建議系統(tǒng)設(shè)計(jì)為從并行的NOR Flash啟動(dòng),因?yàn)檫@種方式NOR Flash占用的MIO管腳數(shù)量大多(大于40個(gè)管腳),系統(tǒng)設(shè)計(jì)為從NAND Flash或QSPI啟動(dòng)都可以,這兩種方式占用的MIO管腳數(shù)量要少些,NAND Flash的優(yōu)點(diǎn)是容量比較大,缺點(diǎn)是讀寫速度要慢些(典型速度 10MB/s), QSPI也是一種NOR Flash,不過接口是四線串行接口,可以獲得比較高的讀寫速度(典型速度 50MB/s),如果系統(tǒng)希望從其它方式如USB, Ethernet, SD/SDIO等方式啟動(dòng),這都需要用戶在第一級(jí)啟動(dòng)映像內(nèi)自行設(shè)計(jì)啟動(dòng)引導(dǎo)代碼。

-

PS

+關(guān)注

關(guān)注

0文章

73瀏覽量

36422 -

Zynq

+關(guān)注

關(guān)注

10文章

609瀏覽量

47175

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

詳解Zynq的兩種啟動(dòng)模式

通過JTAG啟動(dòng)Linux的方法和腳本

Zynq在非JTAG模式下的啟動(dòng)配置流程

Zynq在非JTAG模式下的啟動(dòng)配置流程

ZYNQ器件的啟動(dòng)配置方法

ZYNQ 7系列FSBL的啟動(dòng)過程與配置方法

Xilinx FSBL如何操作啟動(dòng)Zynq器件

ZYNQ的啟動(dòng)原理和配置

Zynq的啟動(dòng)與配置過程詳解

如何在 Vitis 中調(diào)試 Zynq UltraScale 器件啟動(dòng)鏡像

一文詳解ZYNQ器件的啟動(dòng)配置方法

一文詳解ZYNQ器件的啟動(dòng)配置方法

評(píng)論