#01

PCIe Gen 5 簡介

PCIe 是用于硬盤、固態(tài)硬盤 (SSD)、圖形卡、Wi-Fi 和內(nèi)部以太網(wǎng)連接的先進(jìn)互連 I/O 技術(shù)。PCIe 由一組快速、可擴展且可靠的 I/O 標(biāo)準(zhǔn)組成,用于串行數(shù)據(jù)傳輸總線。PCIe 的物理層 (PHY) 還支持 SATA Express (SATAe) 和非易失性存儲器規(guī)范 (NVMe)。

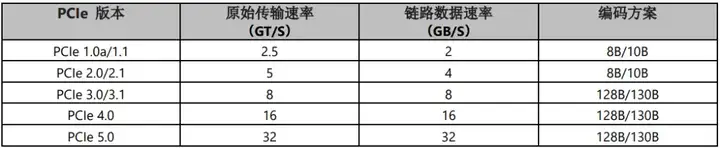

表 1 顯示了 PCIe 數(shù)據(jù)速率的演變,PCIe 5.0 的吞吐量較上一代 PCIe 4.0 增加一倍。需要注意的是 PCIe 原始傳輸速率的單位是 GT/s ,而鏈路數(shù)據(jù)速率的單位是 Gb/s。

表 1:五代 PCIe 的對比表

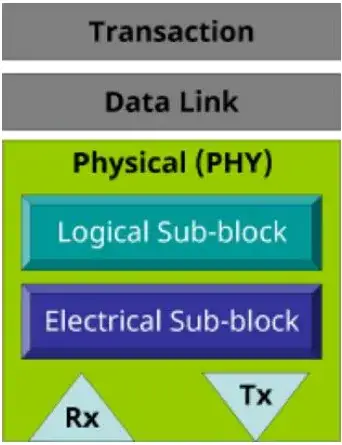

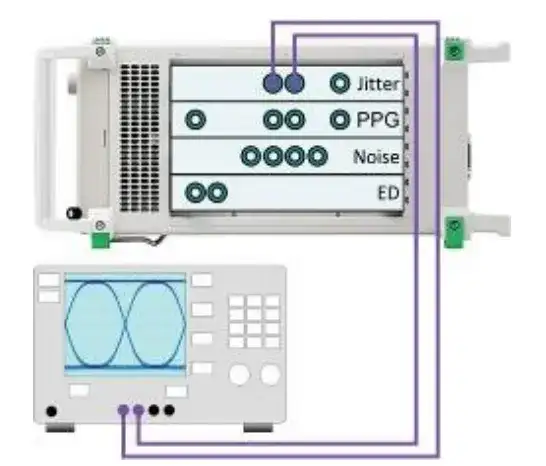

需要注意,編碼方案從 PCIe 2 的 8B/10B 更改為 PCIe 3 的 128B/130B,將開銷從 20% 降低到 2% 以下,使得原始傳輸速率從 5 GT/s 更改為 8 GT/s,鏈路數(shù)據(jù)速率從 4 Gb/s 更改為 8 Gb/s。本文研究了關(guān)鍵的 PCIe 5.0 串行器/解串器 (SerDes) 測試。PCIe 測試的關(guān)鍵設(shè)備包括誤碼率測試儀 (BERT) 和實時示波器。特別是 PCIe 5.0 測試,要求使用高質(zhì)量 BERT 的脈沖碼型發(fā)生器 (PPG) 和 BERT 的誤碼分析儀 (ED)。PPG 需要能精確生成特定損耗的信號,ED 應(yīng)能夠分析 SerDes 輸出誤碼率 (BER) 以確定待測件是否符合 PCIe 規(guī)范。對于最復(fù)雜的 SerDes 測試,如鏈路均衡訓(xùn)練,誤碼儀需要能夠模擬 SerDes。PPG 和 ED 必須在 PCIe 5.0 協(xié)議棧下的物理邏 輯子層與被測設(shè)備 (DUT) 進(jìn)行交互(圖 1),也就是說誤碼儀需要具備一定程度的協(xié)議交互功能。無論是要進(jìn)行發(fā)端還是接收端測試,SerDes 都會涉及到 ;為了清楚地區(qū)分,我們分別用“DUT-發(fā)端”和“DUT-收端”代替 DUT-SerDes。

圖 1:PCIe 協(xié)議棧。

下一章節(jié)將回顧以 32 GT/s 的速度傳輸 NRZ 信號所帶來的挑戰(zhàn),第 3 部分將比較 PCIe 4.0 與 PCIe 5.0 的測試方法,第 4 部分介紹鏈路訓(xùn)練,第 6-9 部分介紹關(guān)鍵的 SerDes 測試。本文最后討論為實現(xiàn)精準(zhǔn)的 PCIe 5.0 調(diào)試和一致性測試,需要配置哪些關(guān)鍵的測試設(shè)備功能。

#02

32 GT/s 下 NRZ 的挑戰(zhàn)

從 PCIe 4.0 的 16 GT/s 升級到 PCIe 5.0 的 32 GT/s 帶來的最大挑戰(zhàn)是在規(guī)定的 BER≤2.5×10-13的情況下,如何在高達(dá) 37 dB 的損耗下正常運行。為了遷移損耗所引起的問題,大多數(shù)運行速度超過 30 GT/s 的標(biāo)準(zhǔn)都采用了 PAM-4(4 電平脈沖幅度調(diào)制)。PAM-4 可以將帶寬減半,但代價是信噪比降低了 9.5 dB 以上。PCIe 5.0 繼續(xù)使用非歸零 (NRZ) 調(diào)制方案,以高電平表示邏輯 1s,以低電平表示邏輯 0s。預(yù)期 PCIe 6.0 將采用 PAM-4 并將達(dá)到 64 GT/s 的速率。在如此高的損耗下,符合 PCIe 5.0 規(guī)范的信號在均衡后的眼高可能會低至 10 mV,如此小的眼張開幅度需要非常靈敏的閾值判決電壓。為了支持更長的鏈路,當(dāng)損耗超過-36 dB 或信號通過兩個或更多連接器時,這時需要用到重定時器。從 PCIe 4.0 到 PCIe 5.0, 數(shù)據(jù)速率提升了一倍,但標(biāo)準(zhǔn)委員對一致性測試性要求做了最低程度的修改。為解決信號衰減問題, 對信道和連接器的損耗和反射提出了更為嚴(yán)格的要求,并且對接收器和發(fā)射器均衡進(jìn)行了小幅改進(jìn)。盡管如此,并沒有特定的創(chuàng)新來補償由于數(shù)據(jù)速率翻倍帶來的升降時間變短、單位間隔 (UI) 變小和插入損耗變大而引起的不可避免的問題。 2.1符號間干擾和均衡

符號間干擾 (ISI) 是由頻率相關(guān)的信道損耗引起的,每個傅里葉頻率分量損耗程度不同,會導(dǎo)致位重疊并產(chǎn)生干擾。“鏈路訓(xùn)練”自適應(yīng)均衡方案可以糾正 PCIe 5.0 中的 ISI。鏈路訓(xùn)練涉及發(fā)端和收端之間的通信,以優(yōu)化和協(xié)調(diào)可調(diào)節(jié)的均衡參數(shù):發(fā)端的前饋均衡器(FFE)的階數(shù)、收端 CTLE 增益和決策反饋均衡器 DFE 的階數(shù)。

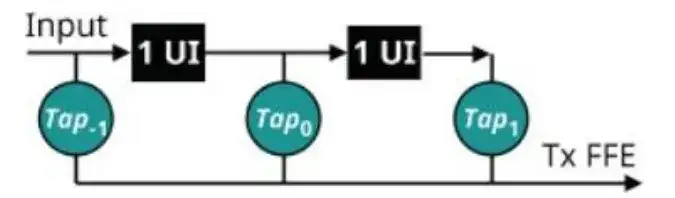

FFE 是對較低數(shù)據(jù)速率下使用的去加重方案,F(xiàn)FE 不僅僅是修改轉(zhuǎn)換位的的幅度,而是擴展到轉(zhuǎn)換位前后兩個或更多位的幅度 (圖 2)的修改。最終,發(fā)端 FFE 以某種方式對波形進(jìn)行預(yù)失真,從而部分補償由信道頻率響應(yīng)引起的失真。

圖 2:發(fā)端 3 階 FFE 的實現(xiàn)方式

隨著 PCIe 速率的不斷提高,抖動、噪聲、失真、串?dāng)_和 ISI 也會為設(shè)計帶來更大的挑戰(zhàn),PCIe 5.0 眼圖在收端完全閉合。為了實現(xiàn) BER ≤10-12,接收的實現(xiàn)會變得越來越復(fù)雜:其中包括時鐘恢復(fù)、發(fā)射端和收端的多個均衡方案、以及本文所述提及的為了評估誤碼率所需要的靈敏度要求等。

PCIe 規(guī)范規(guī)定了接收器性能要求,但從未規(guī)定接收器應(yīng)如何滿足這些要求。相反,PCIe 5.0 定義了具有時鐘恢復(fù)、CTLE 和 DFE 的“參考接收機”,我們可以將這一參考看作是專為評估發(fā)端而定義的合理的接收器實現(xiàn)方式。

#03

PCIe 4.0 和 5.0 SerDes 要求比較

PCIe 標(biāo)準(zhǔn)包含三個相互依賴的規(guī)范,旨在確保不同供應(yīng)商之間的 SerDes 和信道之間的互操作性:

? BASE 規(guī)范定義了芯片級性能,這是一份由上千頁內(nèi)容組成的綜合文檔。

? CEM 規(guī)范規(guī)定了插卡連接器的最低性能。

? 測試規(guī)范設(shè)置了一致性測試的規(guī)則。

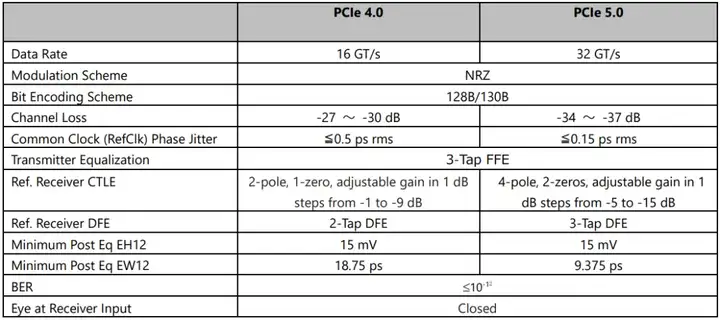

表 2 總結(jié)了 PCIe 4.0 和 5.0 SerDes 要求之間的區(qū)別。

表 2:PCIe 4 和 5 標(biāo)準(zhǔn)總結(jié)

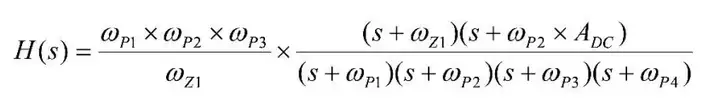

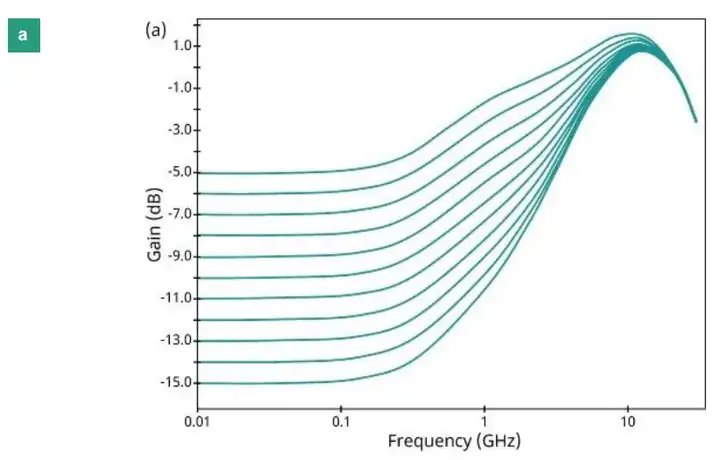

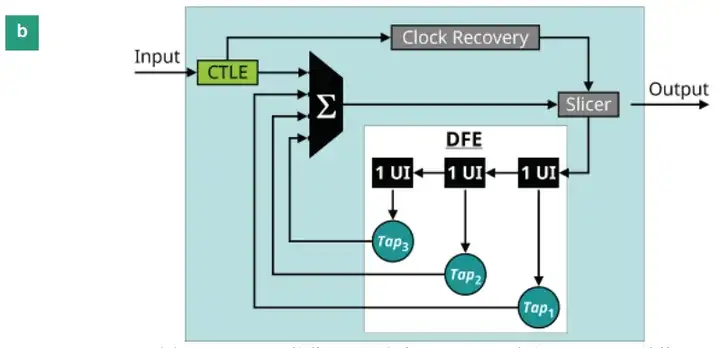

PCIe 4.0 和 5.0 有很多共同點,兩者均使用 NRZ 調(diào)制、128B/130B 編碼、相同的 10-12BER 目標(biāo)以及相同的連接器引腳。發(fā)端使用相同的 FFE 方案,有 11 組加重預(yù)設(shè) P0-P10。Gen 5.0 的參考接收機均衡方案更加詳盡;與 PCIe 4.0 中使用的 2 極點、1 零點 CTLE 響應(yīng)不同,PCIe 5.0 使用 4 極點、2 零點 CTLE 濾波器響應(yīng)(圖 3)。

新的 CTLE 提供更大的靈活性和更深的增益范圍,即 -5 到 -15 dB。PCIe 5.0 還為參考接收器 DFE 添加了第三個 tap。

圖 3:PCIe 5.0 接收器均衡方案:(a) CTLE 響應(yīng)和 (b) DFE 結(jié)構(gòu)。

發(fā)端的輸出電壓保持不變,PCIe 4.0 和 5.0 都單位間隔(UI)d 的抖動指標(biāo)是一樣的。但如果換算成皮秒單位時,抖動要成比例減少。在 PCIe4.0 中,分布式參考時鐘或共用時鐘的架構(gòu)是可選的,但是在 PCIe 5.0 是必須要求支持的。

速率從 16 GT/s 提升到 32 GT/s 的最大困難在于損耗需要從-28dB 增加到 -376dB;因此,信道要求進(jìn)行了重新定義,CEM 規(guī)范僅允許插卡采用表面安裝連接器,而不允許使用過孔連接器。

損耗增加意味著 PCIe 5.0 需要新的一致性測試板,PCIe5.0 的測試夾具只能從 PCI-SIG 購買。測試夾具包括 CBB 和 CLB,都可從外部對兩者進(jìn)行復(fù)位以及 Preset 的切換控制。

#04

鏈路訓(xùn)練

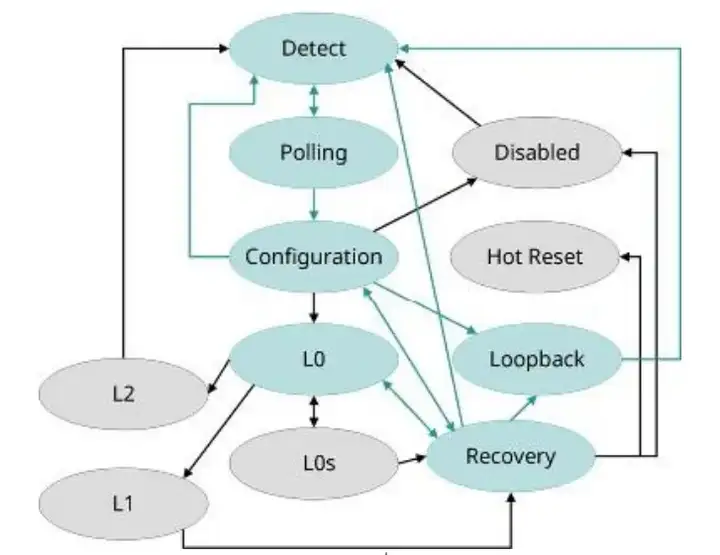

鏈路訓(xùn)練要求收端與處于 PCIe 協(xié)議棧物理層的電氣子層和邏輯子層的發(fā)端進(jìn)行通信,自適應(yīng)均衡方案通過鏈路訓(xùn)練狀態(tài)和狀態(tài)機 (LTSSM) 進(jìn)行工作,如圖 4 所示,LTSSM 將系統(tǒng)配置為以可能的最大數(shù)據(jù)速率工作。

LTSSM-鏈路培訓(xùn)狀態(tài)和狀態(tài)機

圖 4:控制自適應(yīng)均衡的 LTSSM。

從上電開始,LTSSM 會經(jīng)歷以下階段:

檢測:接收機檢測收到的發(fā)端信號。上電開始,發(fā)端以 2.5 GT/s 的速度發(fā)送 PCIe 1.0 信號。

輪詢:接收機同步波形并確定位速率和極性。

配置:確定通道寬度,即 PCIe 信道數(shù)。

L0:啟用鏈路訓(xùn)練。

恢復(fù):發(fā)端按照根據(jù)預(yù)設(shè)的 FFE tap 或者根據(jù)上一工作狀態(tài)優(yōu)化的一組 tap 工作。上電時,它在沒有 FFE 的情況下工作,這等同于將所有 tap 設(shè)為 1。PCIe 2.0 有兩組 preset,PCIe 3.0 有 10 組 preset,PCIe 4.0 和 5.0 都有 11 組 preset ,依次標(biāo)為 P0、P1、...P10。

環(huán)回:收端使用內(nèi)置的系統(tǒng)測試功能,例如 CRC,來檢查訓(xùn)練序列同步信號的 BER 性能。

a. 如果 BER 性能是可以接受的,并且系統(tǒng)以低于 PCIe 5.0 的速率(即 32 GT/s)運行,則收端向發(fā)端發(fā)送請求以提高數(shù)據(jù)速率,換言之,從 PCIe n 升級到 PCIe n+1,然后,接收器返回到檢測階段。

b. 如果 BER 性能不可接受,但是鏈路訓(xùn)練時間未超過最大時限,則會發(fā)生以下一種或多種情形:i. 收端發(fā)送請求,請求發(fā)端發(fā)送不同的 FFE tap:遞增、遞減、保持不變或加載另一個預(yù)設(shè)。ii. 收端修改自己的均衡方案,例如,調(diào)整 CTLE 增益和/或 DFE tap,但請注意,PCIe 僅指定接收器的 BER 性能,而不指定均衡技術(shù)。然后,系統(tǒng)返回到恢復(fù)階段。

c. 如果鏈路訓(xùn)練時間超過了最大時限,并且接收器尚未找到一種均衡方案以使它能以最大允許 BER 或 更高的 BER 工作,或者接收器失去同步,則系統(tǒng)將恢復(fù)為較低的數(shù)據(jù)速率。

在發(fā)端均衡測試時,BERT ED 充當(dāng)環(huán)回模式工作的參考接收器。它指示 BERT PPG 向 DUT-發(fā)端發(fā)送對不同 preset 的請求。示波器捕獲并分析發(fā)端的波形。

在接收測試時下,BERT PPG 充當(dāng)參考發(fā)射機。參考發(fā)射機通過 ISI 測試板將衰減幅度最大的信號發(fā)送到 DUT-收端。在階段 1 中,它發(fā)送基于協(xié)議的訓(xùn)練序列,將速率、極性和配置傳達(dá)給 DUT-接收器。到了階段 5,處于環(huán)回模式的 DUT 發(fā)送 FFE tap 請求;BERT PPG 接收并解釋這些消息,并相應(yīng)地修改其 FFE 方案。

#05

發(fā)端鏈路均衡測試

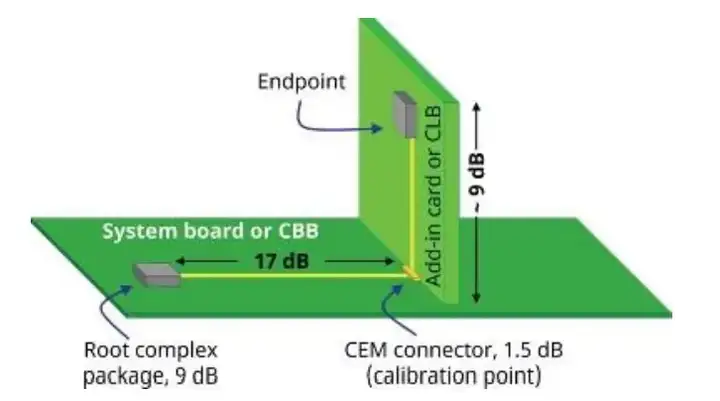

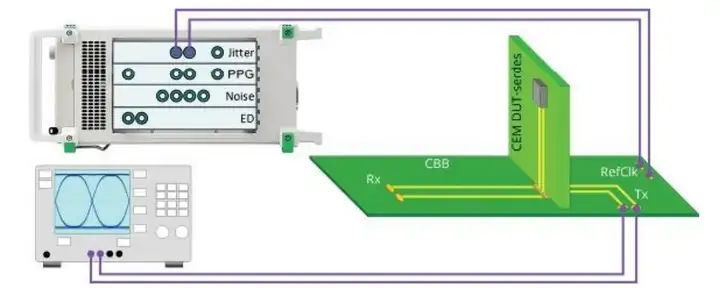

發(fā)端測試需要用到 PCI-SIG 提供的 SigTest 。圖 5 顯示了 CEM 或 BASE 測試圖。在 CEM 測試中,DUT 既包括 SerDes,也包括安裝 DUT 的插卡。在 BASE 測試中,DUT 只包含 SerDes 本身,并且安裝在系統(tǒng)板上。這兩個測試非常相似。我們將詳細(xì)研究 CEM 插卡測試,然后在第 9 部分 中介紹如何歸納這一測試并應(yīng)用到 BASE 測試。

圖 5:標(biāo)稱 PCIe 5.0 信道。

5.1 初始發(fā)射器均衡測試

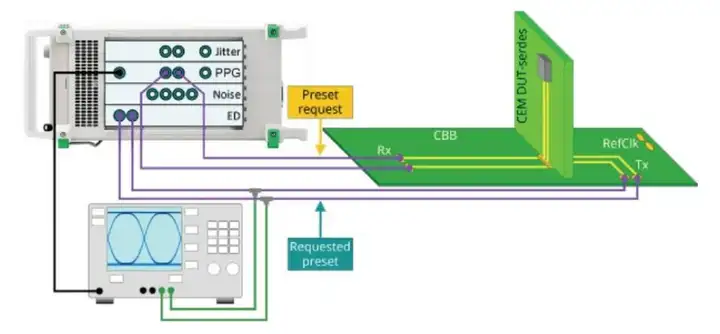

BERT PPG 通過 PCIe 物理層邏輯子塊協(xié)議將請求發(fā)送到 DUT-發(fā)端(圖 6)。BERT PPG 按照每個 PCIe 數(shù)據(jù)速率下的 FFE 預(yù)設(shè)依次向 DUT-SerDes 發(fā)送請求。DUT-發(fā)端修改其 FFE 方案并發(fā)射信號。DUT-發(fā)端輸出信號被分成兩路,以便其信號同時發(fā)送到示波器和 BERT ED。BERT ED 作為參考接收器確認(rèn)預(yù)設(shè)變化,而 BERT 使用 PPG 輔助輸出觸發(fā)示波器捕獲每個信號。示波器按照每個 FFE 預(yù)設(shè)和每個數(shù)據(jù)速率捕獲波形,然后運行安裝在示波器上的 SigTest。SigTest 會評判每個波形是否符合規(guī)范并給出結(jié)果。

圖 6:初始發(fā)射器均衡測試裝置。

5.2 發(fā)端鏈路均衡響應(yīng)測試

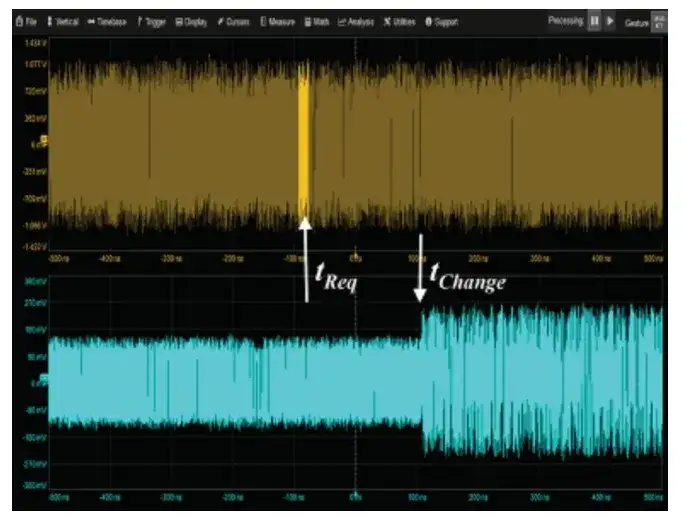

發(fā)端鏈路均衡響應(yīng)測試測量 DUT-發(fā)端響應(yīng) FFE tap 請求所花費的時間,并確定響應(yīng)是否正確。BERT 充當(dāng)環(huán)回模式下的參考 SerDes。示波器確定請求的時間 tReq 和 FFE tap 變化的時間 tChange。tChange - tReq 必須小于或等于指定的最大值,BASE 規(guī)定為 500 ns,CEM 規(guī)定為 1 μs。圖 7 顯示了測試設(shè)置。BERT PPG 差分輸出信號一分為二,分別將信號傳輸?shù)?DUT-收端和示波器。DUT-發(fā)端輸出也分為兩路,分別將信號發(fā)送到示波器和作為參考接收器的 BERT ED。

圖 7:發(fā)射器鏈路均衡響應(yīng)測試裝置。

測試從 BERT PPG 向 DUT-發(fā)射器發(fā)送預(yù)設(shè)請求開始,也就是從 PHY 層邏輯子塊中的協(xié)商開始。DUT 通過更改其 FFE tap 做出響應(yīng)。示波器還將接收并必須能夠識別預(yù)設(shè)請求才能測量 tReq;從這個意義上說,示波器必須具有某種協(xié)議功能。示波器也可以通過觸發(fā)信號來確定 tReq,但是由于觸發(fā)電纜的時間延遲,這種方法增加了測量的不確定性。圖 8 是示波器屏幕截圖,其中金色表示 BERT PPG 輸出,藍(lán)色表示 DUT-發(fā)端信號。DUT-發(fā)射器 FFE 預(yù)設(shè)變化時間 tChange 十分明顯。示波器通過標(biāo)記接收包含請求的數(shù)據(jù)包的時間來確定 tReq。

圖 8:示波器的屏幕截圖,金色表示 BERT PPG 的輸出,藍(lán)色表示 DUT-發(fā)端的輸出。

#06

接收機鏈路均衡測試

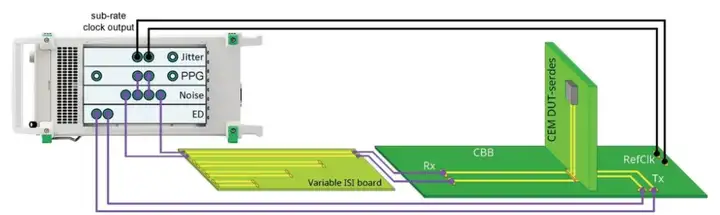

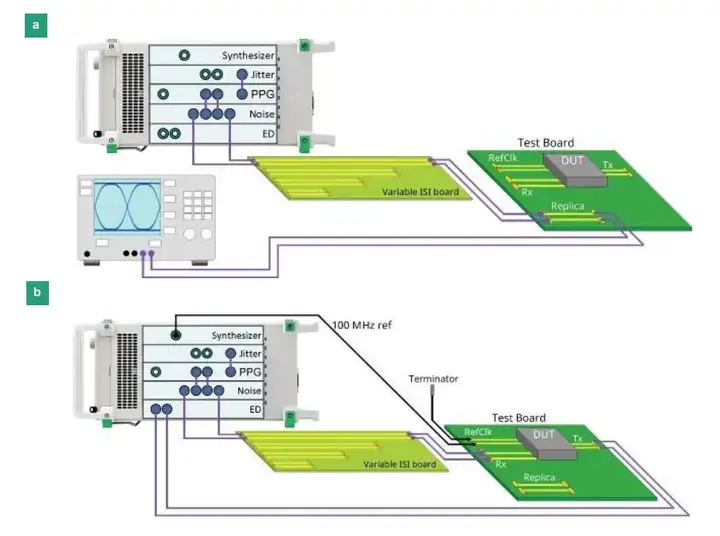

PCIe 5.0 接收機僅在物理層級別進(jìn)行一致性規(guī)范測試:通過在鏈路均衡測試中使用加壓信號,同時評估鏈路訓(xùn)練和加壓壓接收機容限。BERT PPG 傳輸包括抖動和干擾的測試信號:隨機抖動 (RJ)、正弦抖動 (SJ)、正弦差模干擾 (DMI) 和共模干擾 (CMI)。一個“可變 ISI”測試板具有多個差分跡線長度,損耗以 0.5 dB 為步長介于 34 到 37 dB 之間,適用于不同程度的損耗和 ISI。示波器用于校準(zhǔn)測試信號。接收機壓力容限測試的概念是讓 DUT-收端能夠適應(yīng)符合規(guī)范的最差信號。DUT-SerDes 必須能夠使用此最大加壓信號來訓(xùn)練鏈路。鏈路經(jīng)過訓(xùn)練,并且發(fā)端 FFE 和接收器均衡方案得到優(yōu)化后,DUT-收端就一定能以 BER ≤10-12的條件工作。圖 9 顯示了測試裝置。BERT PPG 將注入干擾噪聲的信號發(fā)送到可變 ISI 板。可變 ISI 板的輸出連接到 CBB,CBB 模擬系統(tǒng)板在最壞情況下的性能。測試信號通過 CBB 傳播到 CEM 連接器,并沿著插卡向上到達(dá) DUT-接收端。注意,BERT PPG 通過參考時鐘對信號施加抖動。DUT-發(fā)端的輸出發(fā)送到 BERT ED,BERT ED 既要測量 BER,又充當(dāng)參考接收器來訓(xùn)練鏈路。

圖 9:PCIe 5.0 CEM 插卡接收機鏈路均衡測試的設(shè)置。

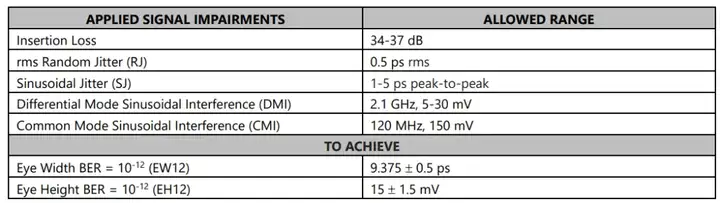

6.1 壓力眼校準(zhǔn) 加壓信號校準(zhǔn)是一個迭代過程,涉及信號生成和示波器 CTLE 的優(yōu)化。每個 BERT PPG preset 都必須進(jìn)行加壓信號校準(zhǔn),并且每組 FFE tap 必須符合規(guī)范。校準(zhǔn)的目的是配置一個最差 ISI 的信號,它具有最小的均衡后的 EH12(BER = 1E-12 時的眼高)和 EW12(BER = 1E-12 時 的眼寬),如表 3 所示。既然信號是用于發(fā)到 CEM 連接器上,因此必須在校準(zhǔn)過程中模擬最壞情況下的插卡損耗。為了最大程度地增加對均衡方案的壓力,應(yīng)按特定順序評估信號減損。為了達(dá)到期望的 EH12 和 EW12,需要為信號增加所需水平的 RJ 以及允許范圍內(nèi)的損耗、SJ、DMI 和 CMI,具體可參見表 3。

表 3:為達(dá)到期望的 EH12 和 EW12,可以添加到信號中的 RJ、SJ 和 DMI 范圍

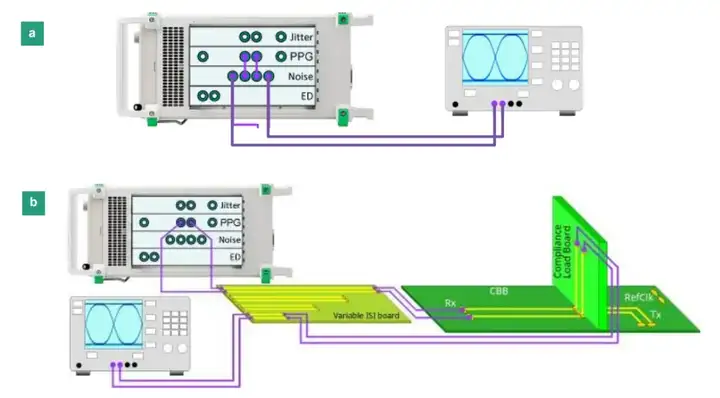

圖 10a 所示為抖動和噪聲校準(zhǔn)裝置。在這一步中,我們確定最壞情況下的 RJ、SJ 和 DMI 組合。 步驟 1:為校準(zhǔn)最壞情況下的抖動,將 BERT PPG 連接到示波器輸入,并確認(rèn) PPG 應(yīng)用了表 3 中所需水平的 rms RJ 和最大允許 SJ 幅度。步驟 2:為校準(zhǔn) DMI 和 CMI,將 BERT PPG 輸出連接到可變 ISI 測試板的最高損耗(最長)通道,即“兼容 37 dB”信道。將幅度為 5 至 30 mV、頻率 2.1 GHz 的正弦 DMI 和 CMI 通過測試板傳輸?shù)绞静ㄆ鳌S捎谠撔诺涝?2.1 GHz 頻率下約有 6 dB 的 損耗,因此 BERT PPG 輸出端的干擾幅度將與傳遞給 CBB 的信號的幅度不同。

圖 10:校準(zhǔn)裝置,(a) 抖動和干擾校準(zhǔn),以及 (b) 初始預(yù)設(shè)/CTLE 校準(zhǔn)。

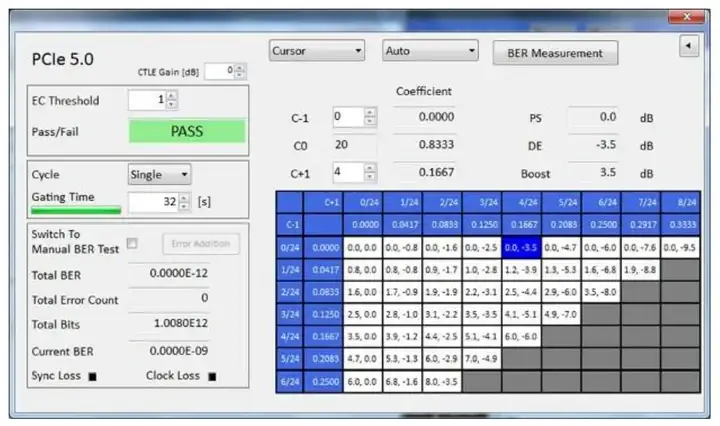

步驟 3:下一步是應(yīng)用最大 ISI,并為每個參考發(fā)端 preset 優(yōu)化示波器 CTLE。如圖 10b 所示,BERT PPG 輸出被發(fā)送到到可變 ISI 板上最壞情況下的 37 dB 信道。可變 ISI 板的輸出連接到 CBB。CBB 的輸出連接到可變 ISI 板的 9 dB 損耗信道,以模擬最壞情況下的插卡損耗。9 dB 信道輸出連接到示波器輸入。或者, 示波器可以嵌入插卡損耗。測量 EH12 和 EW12。如果任意一個值小于允許的最小值,請嘗試可變 ISI 板上的另一條通道。不斷嘗試,直到確定能夠得 到高于指定最低值的最小 EH12 和 EW12 組合的 ISI 通道。步驟 4:確定最佳的 BERT PPG 預(yù)設(shè)和相應(yīng)的 CTLE 增益。對于每個 preset,示波器應(yīng)捕獲至少五個重復(fù)波形。示波器應(yīng)能夠自動確 定最佳的 CTLE 增益。當(dāng)預(yù)設(shè)加上對應(yīng)的最佳 CTLE 增益能夠得到最大 EH12 和 EW12,就稱為最佳預(yù)設(shè)。步驟 5:得到最佳 preset 和 CTLE 增益組合后,如步驟 3 所述,增加可變 ISI 板上的信道損耗,直到找到 EH12 和 EW12 都超過 各自指定最低值的最小組合。現(xiàn)在重新優(yōu)化均衡方案。到目前為止,我們得到了具有最大損耗、最佳 FFE 預(yù)設(shè)和 CTLE 增益的信號。步驟 6:增加 DMI、CMI 和 SJ,直到 EH12 和 EW12 盡可能接近最小值。很快就會完成目標(biāo)壓力眼的校準(zhǔn)。 6.2 接收端鏈路均衡 BER 測試 一旦配置了 BERT PPG 參考發(fā)射機,并以最壞情況下的壓力和經(jīng)過優(yōu)化的 FFE 進(jìn)行了校準(zhǔn),收端鏈路均衡測試就相對容易了。測試裝置如圖 9 所示。 DUT-SerDes 遵循第 4 部分中所述的 LTSSM,DUT-收端檢測來自 BERT PPG 的發(fā)送信號,進(jìn)入回送模式。一旦進(jìn)入回環(huán)模式,DUT-發(fā)端就會請求 BERT PPG 的 FFE 預(yù)設(shè)。DUT 通過 LTSSM 工作,在嘗試不同的 BERT PPG FFE 預(yù) 設(shè)時,通過修改其接收器均衡方案來優(yōu)化鏈路均衡。BERT ED 在整個過程中監(jiān)視 BER,BER 測試本身需要大約一分鐘的時間,足夠 PCIe 5.0 系統(tǒng)傳輸 2 x 10 12 比特的數(shù)據(jù)。由 于 PCIe 5.0 指定收端的性能而不指定均衡技術(shù),因此最終預(yù)設(shè)可能與校準(zhǔn)期間獲得的預(yù)設(shè)不同。如果 BER <10-12,則 DUT 符合 PCIe 5.0(圖 11)。

圖 11:Anritsu MP1900A 顯示的 PCIe 5.0 接收器鏈路均衡 BER 測試結(jié)果。

6.3 調(diào)試收端鏈路均衡 識別 LTSSM 狀態(tài)之間的過渡以及過渡時間的能力有助于識別 DUT 故障點。Anritsu MP1900A BERT 會記錄 DUT 與 BERT 參考發(fā)端之間的協(xié)商過程。如果 DUT 在接收鏈路均衡測試中的任何步驟發(fā)生故障,可以分析 LTSSM 鏈路訓(xùn)鏈日志以確定故 障原因。

#07

發(fā)端 PLL 帶寬測試

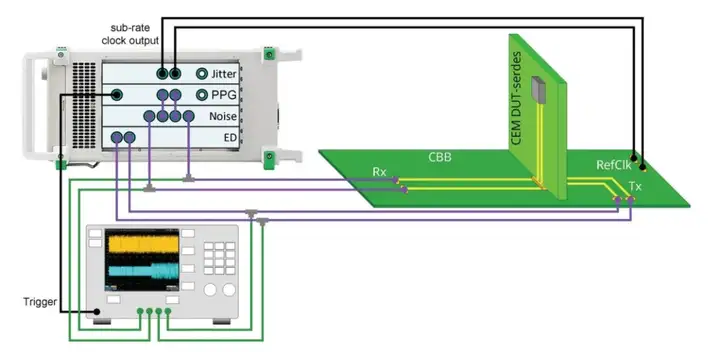

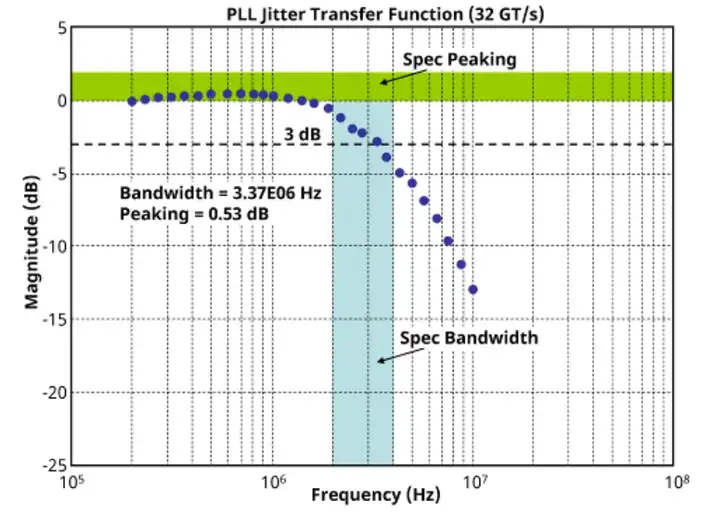

PCIe 5.0 發(fā)端以 100 MHz 參考時鐘 (RefClck) 工作,鎖相環(huán) (PLL) 用于計算參考時鐘與數(shù)據(jù)速率的乘積,串行器使用數(shù)據(jù)速率時鐘將較低速率的數(shù)據(jù)加載到符合 PCIe 的高速串行數(shù)據(jù)信號。 PLL 帶寬測試可測量 DUT-發(fā)端的抖動傳遞函數(shù);也就是進(jìn)入發(fā)射信號的參考時鐘抖動。PLL 帶寬測試可驗證卡 PLL 帶寬和峰值是否在允許的范圍內(nèi),并且是否符合 CEM 插卡規(guī)格要求。 DUT-收端的 -3 dB 的滾降特性必須在指定的頻率范圍內(nèi),并且不會超過峰值。發(fā)端的 PLL 和收端的時鐘數(shù)據(jù)恢復(fù) (CDR) 電 路之間存在互補關(guān)系。由于收端在其 CDR 帶寬以下的頻率具有較強的抗抖動性,而在 CDR 帶寬以上的頻率容易受到抖動 影響,因此發(fā)端的 PLL 必須濾掉高頻抖動,才能使系統(tǒng)以所需的 BER 運行。 該測試使用 BERT 子速率時鐘輸出將 SJ 應(yīng)用于 DUT 參考時鐘。其思路是在跨越指定 PLL 衰減頻率的頻率上應(yīng)用校準(zhǔn)后的 SJ 幅度,并測量每個頻率下 DUT-發(fā)射器的輸出抖動。示波器用于校準(zhǔn) PLL 滾降頻率范圍內(nèi)的 Sj 的幅度(圖 12)。

圖 12:PLL 帶寬測試校準(zhǔn)裝置。

測試裝置如圖 13 所示。抖動的子速率時鐘連接到 CBB 上的 PCI 參考時鐘輸,DUT-發(fā)端輸出連接到示波器。

圖 13:發(fā)端 PLL 帶寬測試設(shè)置

示波器針對所施加 SJ 的每個頻率測量輸出周期抖動 (PJ) 幅度。PCIe 5.0 規(guī)定了發(fā)生-3dB 滾降的允許頻率范圍以及峰值抖 動幅度的允許范圍(圖 14)。

圖 14:發(fā)端 PLL 抖動傳函的結(jié)果。

#08

接收機抖動容限測試 (JTOL)

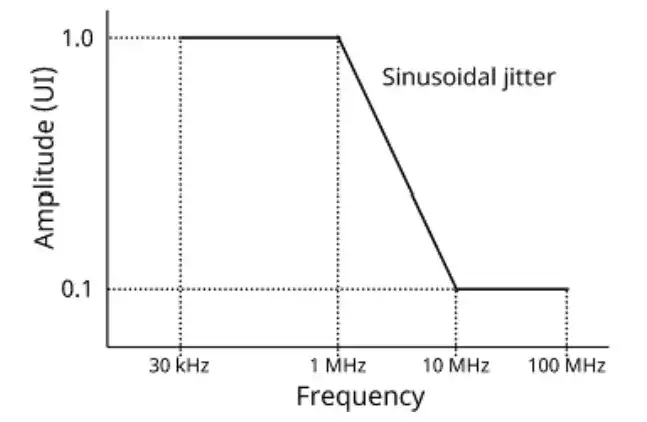

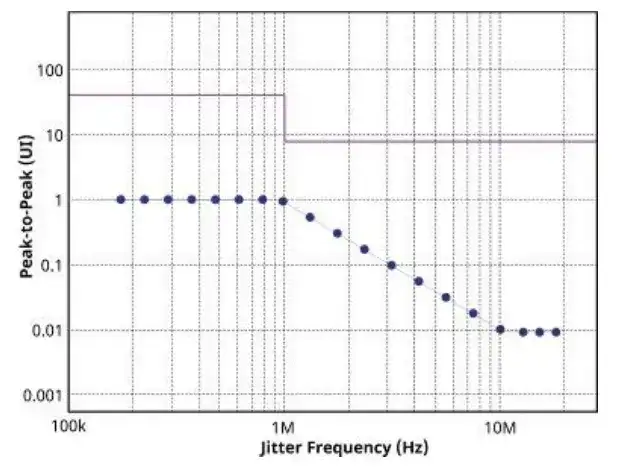

抖動容限測試 (JTOL) 是接收機端對發(fā)端 PLL 帶寬測試的補充。PCIe 5.0 規(guī)范中沒有 JTOL 要求,但 JTOL 是評估接收端容忍不同幅度和頻率抖動的能力的有效方法。 壓力信號是最壞的情況,但也是符合標(biāo)準(zhǔn)的信號,引入了 ISI、RJ、DMI 和 CMI。可以按照第 6 節(jié)“收端鏈路均衡測試”中所 述進(jìn)行校準(zhǔn),再結(jié)合 BERT PPG preset 和示波器參考接收器 CTLE 增益的優(yōu)化組合。作為一種調(diào)試方法或性能冗余度分析,JTOL 可以使用任何均衡方案進(jìn)行測試,根據(jù)圖 15 所示的幅頻模板將 SJ 添加到信號中。

圖 15:JTOL SJ 模板。

高幅度抖動應(yīng)用于低頻,而低幅度抖動應(yīng)用于高頻。從 1 MHz 到 10 MHz 的滾降特性遵循指定的 CDR 頻響特性。對于所有幅頻對,DUT-收端均應(yīng)遵守 BER <10-12(圖 16)。為了使測量保持在合理的時間長度,BER 通常最多測量到 BER <10- 6,并對 BER 概率的斜率推算來確保 BER <10-12。

圖 16:來自 Anritsu MP1900A 的自動化 JTOL 測試結(jié)果。

#09

BASE 規(guī)范符合性測試

以上,我們的討論重點是根據(jù) PCIe 5.0 CEM 規(guī)范進(jìn)行插卡測試,CEM 測試是 BASE 規(guī)范測試的超集。 要符合 BASE 規(guī)范,要求進(jìn)行嚴(yán)格的接收機容限測試,但不需要任何鏈路均衡測試。第 6.1 節(jié)中所述的等效校準(zhǔn)程序是必須要執(zhí)行的,CEM 測試點是 BASE 板插卡連接器,BASE 測試點是在 DUT-SerDes 的引腳上。 PCI-SIG 提供了用于 BASE SerDes 測試的測試板。分線板有兩個信道,一個通道用于 DUT,另一個通道用于校準(zhǔn) DUT-收端引腳上的加壓信號。圖 17 顯示了校準(zhǔn)和測試裝置。在加壓條件下,DUT-收端必須工作在 BER ≤10-12 的情況下。

圖 17:PCIe 5.0 BASE 加壓接收器容限測試裝置:(a) 校準(zhǔn)和 (b) BER 測試。

#10

所需的測試設(shè)備功能

10.1 示波器

示波器的最低要求如下:

實時采樣帶寬 > 50 GHz 為了進(jìn)行發(fā)端信號評估和壓力眼接收容限測試校準(zhǔn),示波器還必須支持 PCI-SIG 測試軟件分析工具。特別是:

眼圖和抖動分析

自動化測試夾具解嵌

PCIe PHY 邏輯子層協(xié)議解碼

自動化鏈路均衡測試 正如鏈路均衡測試描述中所討論的那樣,此功能將示波器的定義擴展到協(xié)議分析器領(lǐng)域。

10.2 BERT(誤碼率測試儀)

BERT 的最低要求如下:

多個以 32 Gb/s 速度運行的 NRZ 碼型產(chǎn)生和誤碼分析通道。

Anritsu MP1900A SQA-R 最多可提供 16 個 NRZ 信道,每個通道的速率可在 2.4 到 32.1 Gb/s 范圍內(nèi)調(diào)節(jié),或最多支 持 8 個 64GB/s 速率的 PAM4 信道。由于 PCIe 5.0 最多允許 16 個通道,因此 MP1900A 可一次性支持所有 SERDES的通道測試。MP1900A 支持 64 Gb/s(32 GBd)PAM4 信道,意味著符合 PCIe 6 規(guī)范要求。

低固有抖動和快速上升/下降時間。

Anritsu 在信號完整性方面始終領(lǐng)先競爭對手。MP1900A SQA-R PPG 通常具有 115 fs rms 的抖動和 12 ps 的上升/下 降時間(20%-80%)。

能夠應(yīng)用 3-tap FFE 的碼型發(fā)生器。

MP1900A 能提供多達(dá) 10 階的 FFE,每階可在-20 到+20 dB 之間調(diào)節(jié)。

集成了 CTLE 和 CDR 的誤碼分析儀。

MP1900A 誤碼分析儀集成了可調(diào)范圍超過 12 dB 的 CDR 和 CTLE。

具有 PCIe 物理邏輯子層的協(xié)議感知能力,能夠響應(yīng)并啟動 LTSSM 命令。

可應(yīng)用所有要求的校準(zhǔn)抖動和噪聲水平的 PPG。

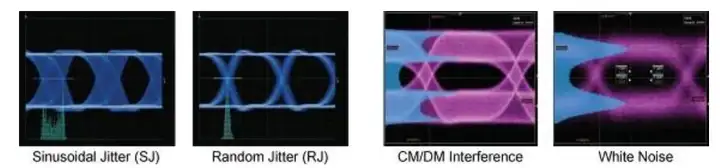

Anritsu MP1900A SQA-R 可以產(chǎn)生所有要求的信號(圖 18),此外,還支持超出 PCIe 5.0 規(guī)范要求的幅度范圍。

? RJ,幅度范圍 0-0.5 UIpp,覆蓋 10 kHz-1 GHz 的帶寬。 ? SJ,幅度范圍 0-2000 UI,對應(yīng)調(diào)制頻率范圍 10 kHz-100 kHz,幅度范圍 0-1 UI,對應(yīng)調(diào)制頻率范圍 10 MHz-250 MHz。 ? 第二個 SJ 頻率為 33 kHz、87 MHz、100 MHz 和 210 MHz。 ? 擴頻時鐘 (SSC),調(diào)制頻率為 28 kHz-37 kHz,幅度為 0-7000 ppm。? 具有所有標(biāo)準(zhǔn) PRBSn 模式的有界不相關(guān)抖動 (BUJ)。? 半周期偶奇抖動 (EOJ)。? 帶寬為 10 kHz-1 GHz 的外部抖動輸入。 ? 在 2 GHz-10 GHz 頻率范圍內(nèi)的正弦 DMI。 ? 在 0.1 GHz-6 GHz 頻率范圍內(nèi)的正弦 CMI。 ? 帶寬為 10 GHz 且波峰因數(shù)大于 5 的白噪聲 ? 內(nèi)部可變 ISI 高達(dá) 30-32 dB。

圖 18:Anritsu MP1900A PPG 不同情況下的信號屏幕截圖

Anritsu MP1900A SQA-R 擁有行業(yè)領(lǐng)先的硬件性能和廣泛的功能集,是適用于 SerDes、光收發(fā)模塊、有源光纜和高速互連 的合規(guī)性測試和調(diào)試分析的理想精密測試儀器,符合多種技術(shù)標(biāo)準(zhǔn):PCIe 5.0 可擴展到 PCIe 6.0、Thunderbolt 3、USB 3.1 Gen 1/2、IEEE 100/200/400 千兆以太網(wǎng)、OIF-CEI 3 和 4、Infiniband EDR/HDR 和 FibreChannel。

內(nèi)容來源:Anritsu

審核編輯 黃宇

-

測試

+關(guān)注

關(guān)注

8文章

5269瀏覽量

126599 -

SerDes

+關(guān)注

關(guān)注

6文章

198瀏覽量

34906 -

pcle

+關(guān)注

關(guān)注

0文章

29瀏覽量

5760

發(fā)布評論請先 登錄

相關(guān)推薦

pcie 4.0與pcie 5.0的區(qū)別

PCIe的最新發(fā)展趨勢

如何測試PCIe插槽的速度

Kioxia發(fā)布PCIe 5.0 EDSFF E1.S SSD

解讀MIPI A-PHY與車載Serdes芯片技術(shù)與測試

聚焦MIPI 系列之二:汽車 SerDes 發(fā)射機測試

DS320PR410支持PCIe5.0、CXL 2.0的四通道線性轉(zhuǎn)接驅(qū)動器數(shù)據(jù)表

FPGA的PCIE接口應(yīng)用需要注意哪些問題

英韌科技:無AI不存儲,國產(chǎn)PCIe 5.0主控率先發(fā)力

曜越發(fā)布M.2 2280 SSD散熱器,專為PCIe 5.0固態(tài)硬盤設(shè)計

下一代PCIe5.0 /6.0技術(shù)熱潮趨勢與測試挑戰(zhàn)

Nextorage發(fā)布首款PCIe 5.0固態(tài)硬盤,性能卓越

M31推出PCI-SIG的官方認(rèn)證PCIe5.0 PHY IP 攜手SSD存儲芯片公司InnoGrit推進(jìn)PCIe5.0新世代

PCIe 5.0 SerDes 測試

PCIe 5.0 SerDes 測試

評論