高速先生成員--黃剛

現在稍有經驗的layout工程師都知道在BGA里面不同封裝的去耦電容從小到大應該按下圖這樣放置:放置的順序是從小電容到大電容采取從近到遠的方式。

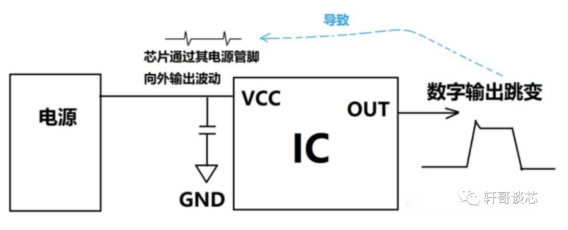

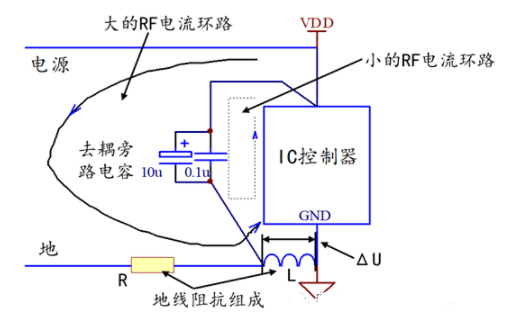

稍微具有SI,PI知識的工程師會說這樣有利于改善電源PDN系統的性能,理論上是電容都應該離芯片引腳越近放置越好,尤其是小電容,比大電容更應該靠近芯片端。為什么呢?專業用語叫小電容的去耦半徑更小。所謂去耦半徑,無非是研究噪聲源和電容補償電流之間的相位關系。當芯片電流發生變化時,會在電源平面的一個局部區域內產生電壓波動,由于信號在介質中傳播需要一定的時間,因此從局部電壓波動到電容感知到這一波動之間有一個時間延遲。同樣,電容的補償電流到達波動區域也需要一個延遲,因此必然造成噪聲源和電容補償電流之間的相位上的不一致。在嚴謹的場合中,Chris就是會這樣來描述這個名詞!

說完上面這一段,相信有不少粉絲感覺Chris什么都沒說似的。行吧,下面就以Chris的理解給大家解釋(fan yi)一下。從應用來說,就是每個電容在與它的自諧振頻率f(波長為λ)相同頻率下的噪聲補償效果最好,相位差越小越好,λ/4時電容失效,出現反諧振。在實際應用中,我們一般取小于λ/50比較穩妥。

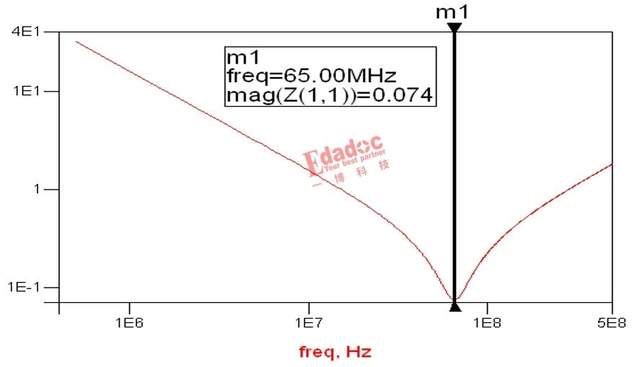

例如下面這個0402封裝的10nf的一款電容,它的真實阻抗如下所示:

從它自身的Z阻抗曲線來看,諧振頻率在65MHz,也就是我們通俗說的這個電容的去耦頻段在65MHz以內。

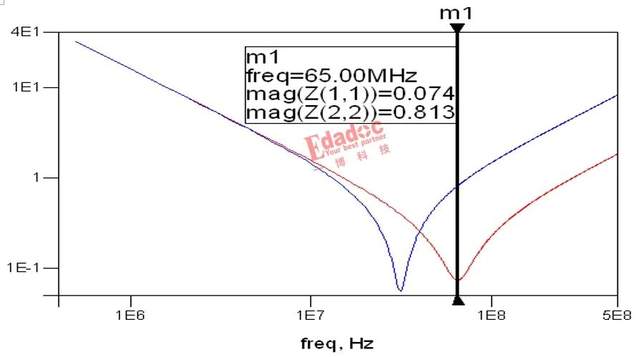

然而實際情況是電容到達Pin或多或少都會有一定的距離,這里假設距離為50ps(大概300mil左右),如下:

這樣的話,這兩者的z阻抗曲線對比就有差別了,經過傳輸線之后的z阻抗諧振點提前,在原諧振點的位置阻抗增加到了0.813歐姆。諧振點頻率也會相應的往前提了,就相當于這個電容的去耦頻段就不能達到那么高頻段了。Chris稍微計算一下去耦半徑:諧振頻率為65MHz,波長為92.7inch(假設在fr4中傳輸),那么λ/50=1.85inch(約300ps),然而從結果上看到50ps的時候變化都已經比較明顯了。

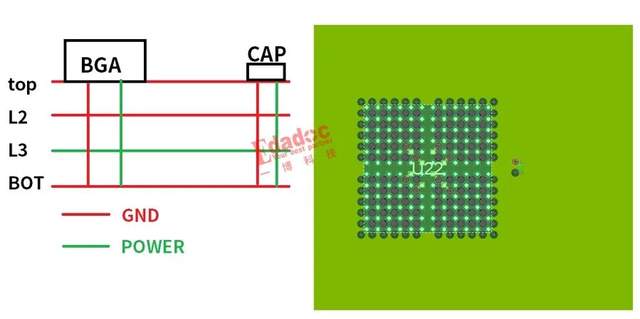

當然上面說的還是理論,只是對比于文字來說有點數字顯得沒那么理論。那應用到具體的PCB設計項目中會是怎么樣的呢?行!Chris大概做了一個簡單的仿真case,如下所示:1個用于仿真的4層板,一個小的BGA和一個0402-100nF的小電容都放在top層。

其中中間L3層是電源層,通過仿真看看電容放在距離BGA不同距離情況下PDN阻抗曲線的變化。

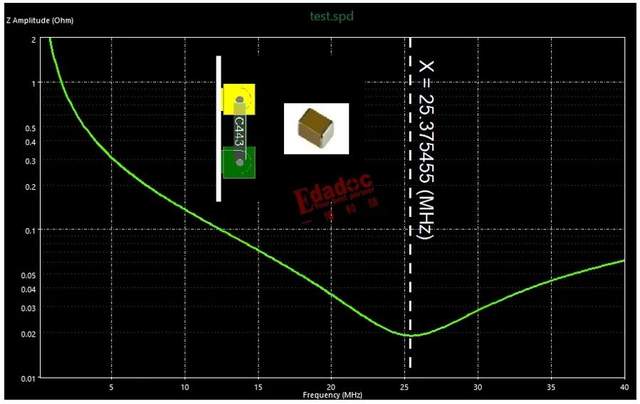

首先看到我們用的這個0402-100nF電容本身的PDN阻抗曲線如下所示:所以看到這個電容本身的諧振頻段在25MHz。這是一個初始的基準,也就是不放在PCB上的情況下,這個電容自己的特性展示。

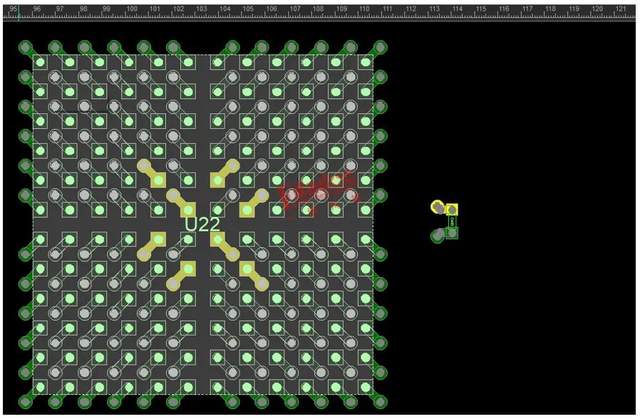

那么我們把電容放在距離BGA最近的位置上,距離BGA大概3mm的樣子。

在這個case下,BGA芯片的PDN阻抗曲線(藍)和單純電容的PDN阻抗曲線(綠)相比,就有了明顯的惡化,去耦的頻段大概變差了7MHz,這個是非常大的惡化了。

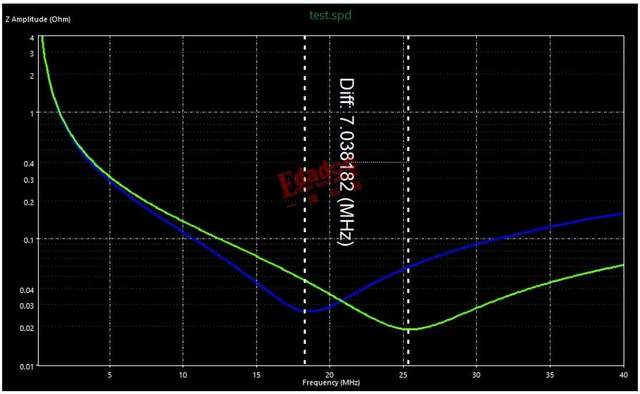

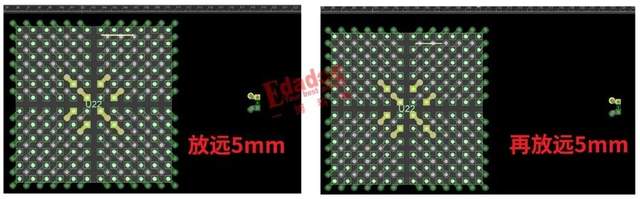

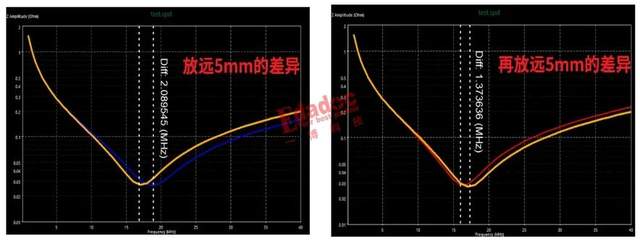

當然,單純理想的電容和放到PCB板上兩者肯定會變差不少。為了讓大家更好的感覺下擺放距離和PDN阻抗曲線的惡化程度,我們分別在距離BGA從上面的3mm,再拉大5mm和10mm的距離,如下所示:

從仿真結果來看,放遠5mm(橘)和原來放在3mm的距離(藍)的PDN阻抗曲線對比,去耦頻段減少了2MHz。再放遠5mm(紅)和放遠5mm(橘)又減少了1.4MHz的樣子。電容本身可以去到25MHz多的去耦頻段,隨著距離越來越遠,有效頻段直接快打了個骨折!

當然這個只是一個很簡單的仿真case,BGA很小,疊層也只有4層,電容也才1個。Chris只是大概通過這個仿真case讓大家形象的看到具體項目中電容隨著位置放遠之后的惡化。不同項目的分析方法其實也是一樣,只不過電容和層數更多,BGA或者PCB板更大,萬變不離其宗。一名優秀的工程師不僅要知道理論,更要知道理論怎么用于實際,從而來解決實際的問題哈!

審核編輯 黃宇

-

濾波

+關注

關注

10文章

667瀏覽量

56633 -

去耦電容

+關注

關注

11文章

315瀏覽量

22325

發布評論請先 登錄

相關推薦

關于陶瓷電路板你不知道的事

退耦電容和濾波電容的區別是什么

去耦電容的擺放位置和作用

巧了不是,原來你也不知道啥是去耦電容的“濾波半徑”啊!

什么是去耦電容 有什么作用

去耦電容越大越好嗎,去耦電容值的選擇

耦合和去耦有什么區別,耦合電容和去耦電容的作用分別是什么?

分享PCB中的去耦電容設計

巧了不是,原來你也不知道啥是去耦電容的“濾波半徑”啊!

巧了不是,原來你也不知道啥是去耦電容的“濾波半徑”啊!

評論