Incremental Compile增量編譯是Vivado提供的一項高階功能。目的旨在當設計微小的改變時,重用綜合和布局布線的結果,縮短編譯時間。

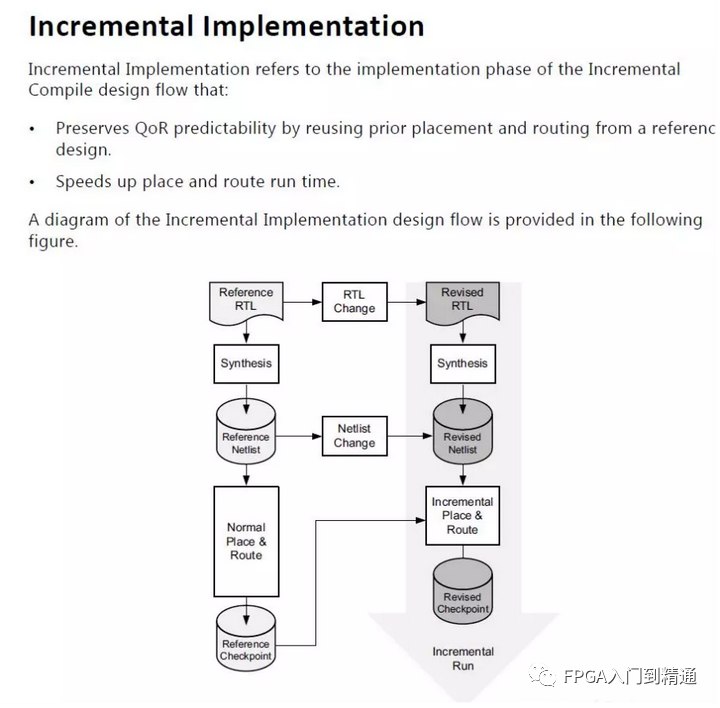

下圖是增量編譯的流程:

增量編譯需要已經編譯完成的原始設計的dcp文件作為參考,當我們在原始設計上做微小的改動時,就可以使用增量編譯的流程。這些改動包括:

- RTL代碼的微小修改

- 網表的微小修改,比如增加或者改變ILA

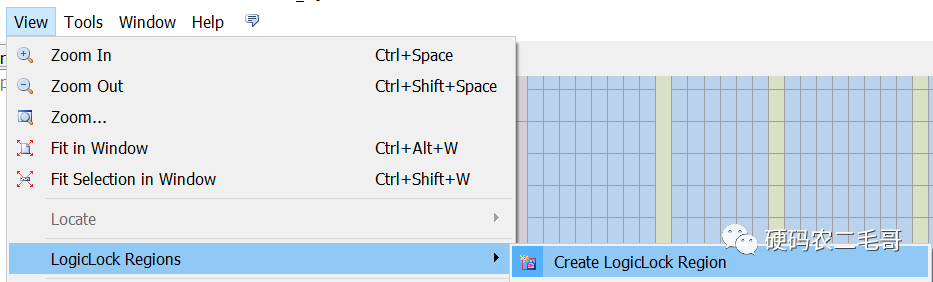

在Vivado里面,使能IncrementalCompile的方式非常簡潔,在Impl run上右鍵選擇“Set Incremental Compile…”,然后設置相應的參考dcp文件即可:

Tips:

1. 當參考設計和當前設計的相似度大于95%的時候,最適合用增量編譯技術

相似度低于75%時,工具會關閉增量編譯

2. 有些時候,即使很小的RTL改動,也會造成網表的巨大差異。比如

a) 改變HDL中的某些全局常量

b) 增加總線的位寬

-

Vivado

+關注

關注

19文章

834瀏覽量

68379

發布評論請先 登錄

Altium如何放置compile mask(編譯屏蔽)

誰能縮短大容量FPGA的編譯時間?增量式編譯QIC!

Vivado Design Suite 2015.3的新功能介紹

Vivado Design Suite 2015.3新增量編譯功能介紹

Vivado綜合引擎的增量綜合流程

Vivadoz中增量編譯與設計鎖定

Vivado增量編譯的基本概念、優點、使用方法以及注意事項

Xilinx Vivado使用增量實現

評論