新興的射頻數(shù)據(jù)轉(zhuǎn)換器——即RF DAC和RF ADC,就架構(gòu)意義而言,使小型多頻段收發(fā)器的創(chuàng)建變成了一種可能。但這些新設(shè)備固有的非線性卻是絆腳石。例如,RF設(shè)備的非線性在頻域有兩面:帶內(nèi)和帶外。帶內(nèi)非線性指的是TX帶內(nèi)不必要的頻率,而帶外非線性則指的是TX帶外的寄生頻率。

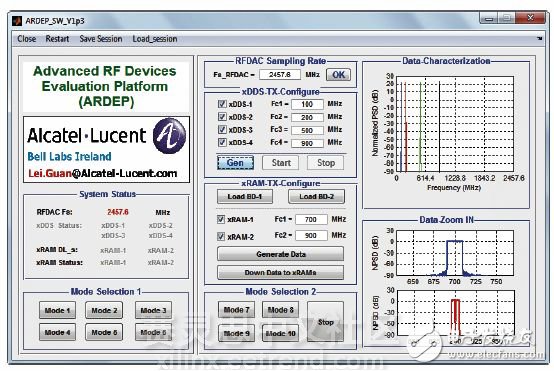

在愛爾蘭貝爾實(shí)驗(yàn)室,我們創(chuàng)建了一個(gè)靈活的軟硬件平臺(tái),用以對(duì)下一代無線系統(tǒng)的潛力股RF DAC進(jìn)行快速評(píng)估。這個(gè)研發(fā)項(xiàng)目有三大關(guān)鍵元素:高性能的Xilinx FPGA,Xilinx知識(shí)產(chǎn)權(quán)IP及MATLAB。我們?cè)谠噲D盡量少使用FPGA資源的同時(shí),又盡可能保持系統(tǒng)的靈活性。以下為系統(tǒng)框圖:

我們挑選了Analog Devices公司最新的RF-DAC評(píng)估板(AD9129和AD9739a)和Xilinx ML605評(píng)估板。ML605評(píng)估板配有Virtex-6XC6VLX240T-1FFG1156 FPGA器件,使用快速開關(guān)I/O (高達(dá)710 MHz)和串并收發(fā)器單元(高達(dá)5 Gbps)來聯(lián)接RF DAC。

設(shè)計(jì)有關(guān)FPGA的部分中涵括了時(shí)鐘分配單元、基于狀態(tài)機(jī)的系統(tǒng)控制單元和DDS基于內(nèi)核的多頻聲生成單元。另還包含了兩個(gè)建立在塊RAM的單元:基于BRAM的小型控制消息存儲(chǔ)單元(cRAM內(nèi)核)和基于BRAM數(shù)組的用戶數(shù)據(jù)存儲(chǔ)單元(dRAM 內(nèi)核)。

設(shè)計(jì)有關(guān)FPGA的部分中涵括了時(shí)鐘分配單元、基于狀態(tài)機(jī)的系統(tǒng)控制單元和DDS基于內(nèi)核的多頻聲生成單元。另還包含了兩個(gè)建立在塊RAM的單元:基于BRAM的小型控制消息存儲(chǔ)單元(cRAM內(nèi)核)和基于BRAM數(shù)組的用戶數(shù)據(jù)存儲(chǔ)單元(dRAM 內(nèi)核)。

時(shí)鐘就是FPGA的生命。為確保多個(gè)時(shí)鐘在FPGA內(nèi)存庫內(nèi)的合理分布,我們篩選了Xilinx時(shí)鐘管理內(nèi)核,該內(nèi)核能以簡單互動(dòng)的方式對(duì)時(shí)鐘進(jìn)行定義和說明。狀態(tài)機(jī)周圍還建立了緊湊的指令內(nèi)核,用以充當(dāng)系統(tǒng)控制單元。

我們?cè)O(shè)計(jì)了兩款測試方案:連續(xù)波(CW)信號(hào)測試(xDDS)和帶寬信號(hào)測試(xRAM)。多頻連續(xù)波測試一直是射頻工程師測試射頻組件非線性特征的首選。秉承相同的測試?yán)砟睿覀冇謩?chuàng)建了一個(gè)基于直接數(shù)字合成器(DDS)的可調(diào)四頻段邏輯內(nèi)核,該內(nèi)核可以在兩個(gè)獨(dú)立的頻帶中,使用一對(duì)深淺不一的信號(hào)來刺激RF DAC。通過單獨(dú)調(diào)整四頻段,便可以評(píng)估RF DAC的線性性能——即,在頻域的位置及互調(diào)刺激的功率。CW信號(hào)測試則是一個(gè)固有的窄帶操作。為進(jìn)一步評(píng)估RF DAC的寬帶性能,則必須使用并發(fā)多波段、多模信號(hào),如:雙模UMTS和LTE2.1 GHz和2.6 GHz信號(hào)。

選擇MATLAB作為主機(jī)軟件的原因是,其在數(shù)字信號(hào)處理(DSP)方面具有諸多優(yōu)勢(shì)。并且,MATLAB也可以提供一個(gè)名為GUIDE的實(shí)用工具,用于布局為平臺(tái)創(chuàng)建的圖形用戶界面(GUI)。以下圖表對(duì)GUI進(jìn)行了說明:

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8696瀏覽量

147098 -

dac

+關(guān)注

關(guān)注

43文章

2291瀏覽量

190984

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

RF DAC多頻帶發(fā)射器線性性能怎么評(píng)估?

一個(gè)針對(duì)多頻段應(yīng)用的直接RF發(fā)射機(jī)例子

雷達(dá)發(fā)射機(jī)的任務(wù)和基本組成

多標(biāo)準(zhǔn)無線電基站發(fā)射機(jī)測試

單片機(jī)串行通信發(fā)射機(jī)單片機(jī)串行通信發(fā)射機(jī)

實(shí)驗(yàn)用雷達(dá)發(fā)射機(jī)的系統(tǒng)設(shè)計(jì)

TR前端組成和雷達(dá)發(fā)射機(jī)

UG-1432:ADF5902 24 GHz、ISM波段多通道FMCW雷達(dá)發(fā)射機(jī)評(píng)估

ADF7011:高性能ISM頻段ASK/FSK/GFSK發(fā)射機(jī)IC數(shù)據(jù)表

RF-DAC多頻帶發(fā)射器線性評(píng)估

一文詳解DAC多頻段發(fā)射機(jī)的線性評(píng)估

一文詳解DAC多頻段發(fā)射機(jī)的線性評(píng)估

評(píng)論