高速先生成員--黃剛

在行業內,要是問PCB工程師的大多數設計規則是參考哪些公司的設計指導的話,高速先生相信intel的設計指導書一定會榜上有名!事實上,從高速先生看到的業界主流芯片或平臺的設計指導書中,intel的design guide,也簡稱PDG一定是各位PCB工程師們的“童年噩夢”,那長達上千頁的內容,而且都還是全英文的,大家掌握起來的難度不可謂不大。

不過有一說一,雖然很難讀,但是它的設計指導參考意義還是非常大的,里面記載著很多PCB工程師使用的設計技巧和方法,使得工程師們在不用具備仿真能力的情況下也能把設計做得很好。當然,正因為這樣,行業內就慢慢有了一定要遵守intel設計規則的傳說了!

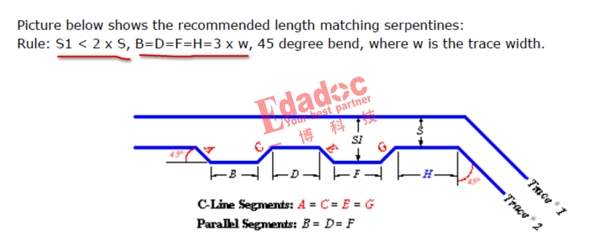

在其中上千頁內容當中,這一條設計規則相信大家也倒背如流了,那就是俗稱的差分線對內等長下的“3W-2S規則”。

是什么意思呢?它說的是在高速差分線對內去做等長設計時,短的那根線進行繞線補償時補償的高度和寬度的約束,3W只是兩個繞包的距離為3倍的線寬W,2S是指繞包最遠的位置與另外一根線距離不大于2倍的差分線對內間距S。這樣說大家應該就很清楚了吧?

當然本來Chris這周打算歇息下,不更新文章了,畢竟也想著讓大家好好消化之前的文章,重質量不重數量嘛(額,其實主要是項目比較忙)。但是上海分部的設計達人強哥一條微信懟過來給Chris,內容大概就這個樣子的。

這個是上海的一個我們比較重要的客戶的疑問,Chris在略微思考下,雖然心理已經有了大概的答案,但是的確也是沒有具體仿真的證明,于是Chris靈機一動,就回復到。。。

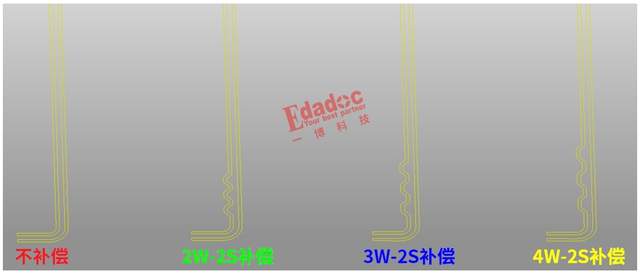

嗯,對!就是這個緣由,所以大家今天就能看到這篇文章了。說干就干,于是強哥根據它之前設計的習慣,大概做了幾組case來讓Chris仿真對比,如下所示:

當然不補償的設計是作為讓大家直觀感受下差距,另外在intel的規則“3W-2S”的旁邊還做了兩種不同的對比case,分別是“2W-2S”和“4W-2S”,Chris想仿真驗證下不按intel要求的“3W-2S”設計的話,其他兩種case的性能差距有多大!

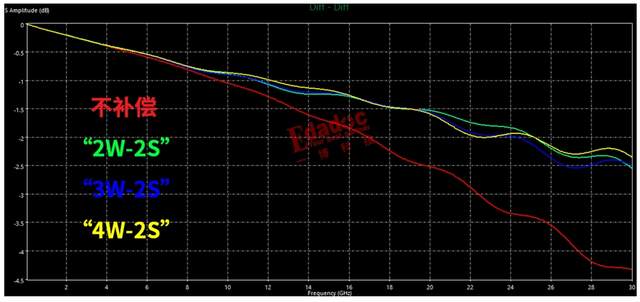

唰的一聲,仿真的結果就出來了。那按照慣例還是先看無源再看有源哈,從無源的插損指標來看,我們能發現兩個點:

1,不補償的設計真差的很多(這還用說嘛!);

2,“2W-2S”、“3W-2S”和“4W-2S”的插損表現,額,不知道你們能不能分出來明顯差距,反正Chris感覺分不出來哈!如果硬要放大看的話,的確是能看到“3W-2S”在15GHz以前(對應差不多25Gbps速率的信號吧)的波動相對小一點。

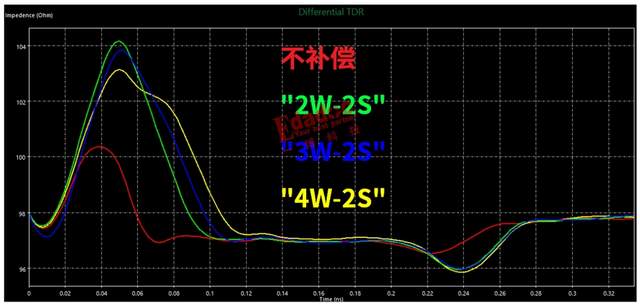

當然Chris會讓大家看到為什么不同“W”之間對插損的波動程度略有區別,我們來看看幾個case的TDR阻抗的對比圖,從阻抗對比可以看到,不同的“W”會導致阻抗不等長(繞線區域的阻抗會增加)的長度不同,所以能看到波動的程度不一樣。

看到這個TDR阻抗圖,很多人就會問了,那不是“2W-2S”的阻抗波動長度越短嗎,那為什么不應該是它的效果最好,為什么intel要推“3W-2S”呢?

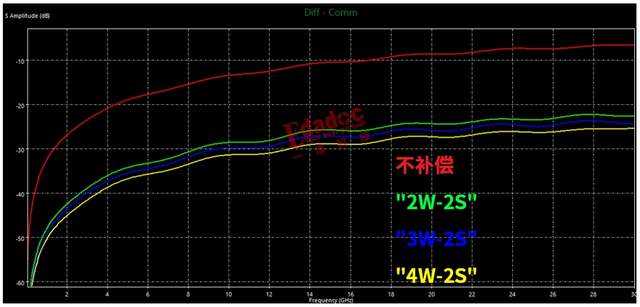

這個問題問得好!這其實跟我們為什么不選不補償的這個case是同一個道理,我們從幾個case的模態轉換結果來看,從模態結果來看你們就會發現一個問題:當然不補償的模態肯定很差了,但是從“2W”到“4W”的對比中,你們會驚訝的發現,最好的反而是“4W”。這就說明了兩個繞包的距離比較近的時候,這跟走線本身也會耦合,導致時序的微微變化,距離越遠,耦合度越差,這樣時序反而相對較好。

從TDR阻抗和模態兩個相矛盾的無源維度來分析,可能intel推薦的“3W-2S”就在兩者中找到一個平衡吧!

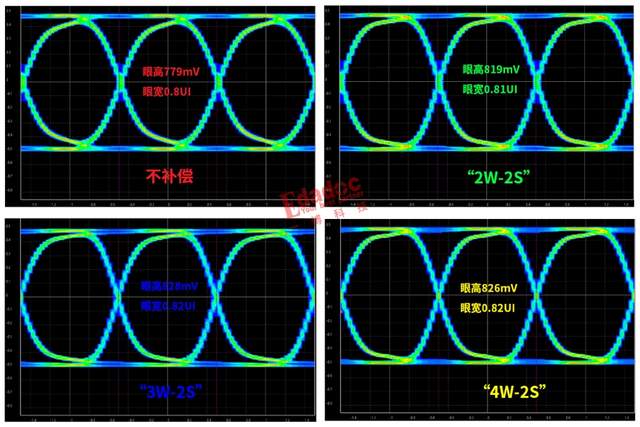

OK,最后我們再來對比下大家更為熟悉的眼圖的結果。我們分別在這4個case的走線中去跑25Gbps速率的碼型,從眼圖的結果也能看到這一點。不補償眼圖明顯差很多這個不用懷疑,三種不同“W”之間的差異其實都不大,哪怕是“3W-2S”的結果是最好的,但是和其他兩種“W”的差異也很小很小。

最后總結下哈,當然intel推薦的“3W-2S”原則首先的確在一定速率的高速信號設計中效果還是很好的,但是Chris想說的話,也沒必要把它神化到一個非常非常非常高的高度哈,在不同的設計場景中,例如板子的密度不同,沒法嚴格的遵守“3W-2S”的情況下,稍微變點“W”的大小或者是“S”的大小也不是一定會很影響信號質量,很多情況下,他們的差異都比intel粉絲們的想象中要小!最后,希望讓Chris寫這篇文章的客戶包括其他也有同樣疑問的朋友們都能順利刷到這篇文章吧!

問題:大家設計中一般都遵守怎么樣的設計規則去做差分對內等長呢,具體談談你們的設計方法?

審核編輯 黃宇

-

intel

+關注

關注

19文章

3482瀏覽量

185922 -

PCB

+關注

關注

1文章

1795瀏覽量

13204

發布評論請先 登錄

相關推薦

不按INTEL的“3W-2S”規則設計,出問題的概率有多大?

不按INTEL的“3W-2S”規則設計,出問題的概率有多大?

評論