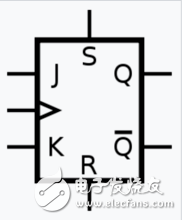

JK觸發器,也被稱為通用可編程觸發器,是數字電路中的一種重要且功能強大的基本存儲器件。其名稱源自其兩個輸入端口J(置位)和K(復位),以及一個關鍵的控制端——時鐘信號控制端(CP)。JK觸發器的原理和功能涉及多個方面,包括其內部結構、工作模式、功能特性以及在數字電路中的廣泛應用。以下是對JK觸發器原理和功能的詳細闡述。

一、JK觸發器的原理

1. 內部結構

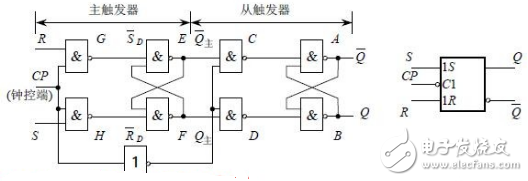

JK觸發器的內部結構通常可以用NAND門(與非門)鎖存器來解釋。與非門是一種邏輯門,其輸出是其輸入的邏輯與的補碼。JK觸發器由兩個與非門構成,形成一個正反饋回路。輸入J和K連接到第一個與非門的輸入,而第一個與非門的輸出連接到第二個與非門的輸入。第二個與非門的輸出再連接到第一個與非門的輸入,形成反饋回路。這種結構使得JK觸發器具有記憶功能,能夠在時鐘信號的作用下保持或改變其輸出狀態。

2. 工作原理

JK觸發器是邊沿觸發觸發器,這意味著它僅在時鐘信號的上升沿或下降沿(具體取決于觸發器類型)到來時觸發狀態轉移。在時鐘信號的非觸發邊沿期間,JK觸發器的輸出狀態保持不變。當時鐘信號CP的上升沿或下降沿到來時,JK觸發器將根據J、K輸入的值來決定是否改變其輸出狀態。

二、JK觸發器的功能

JK觸發器具有置0、置1、翻轉和保持四種功能,這是其作為集成觸發器中功能最為齊全的觸發器之一的重要原因。

1. 保持模式

當J和K輸入均為低電平時(J=0, K=0),JK觸發器將保持其先前的狀態不變,即Q和Q'的輸出將維持原樣。這種模式下,JK觸發器作為存儲元件,能夠穩定地保持數據。

2. 復位模式

當J為低電平而K為高電平時(J=0, K=1),JK觸發器將進入復位狀態,此時Q輸出為0,Q'輸出為1。這種模式下,JK觸發器可以清除其存儲的數據,將輸出置為初始狀態。

3. 置位模式

當J為高電平而K為低電平時(J=1, K=0),JK觸發器將進入置位狀態,此時Q輸出為1,Q'輸出為0。這種模式下,JK觸發器可以將輸出置為特定的狀態,實現數據的設置。

4. 翻轉模式

當J和K輸入均為高電平時(J=1, K=1),JK觸發器將進入翻轉狀態,即其輸出將取反先前的狀態。如果先前Q=0,則翻轉后Q=1;如果先前Q=1,則翻轉后Q=0。這種模式下,JK觸發器可以根據輸入信號的變化靈活地改變其輸出狀態。

三、JK觸發器的功能特性

1. 通用性和靈活性

JK觸發器能夠模擬其他多種類型觸發器的行為,具有極高的通用性和靈活性。通過改變J和K的輸入值,JK觸發器可以實現SR觸發器、D觸發器、T觸發器等多種觸發器的功能。

2. 抗干擾能力強

由于JK觸發器是邊沿觸發觸發器,其狀態轉移僅在時鐘信號的上升沿或下降沿發生。這種特性使得JK觸發器在輸入信號變化時具有較強的抗干擾能力,能夠穩定地工作。

3. 高速工作性能

JK觸發器具有較短的傳輸延遲時間和較高的工作速度。這使得JK觸發器在需要高速處理的數字電路中具有重要的應用價值。

四、JK觸發器在數字電路中的應用

JK觸發器在數字電路中具有廣泛的應用領域,包括時序電路、頻率分析電路、數碼集成電路等多種場合。

1. 時序電路

在時序電路中,JK觸發器常用于構建計數器、分頻器、寄存器等電路。通過合理的組合和連接JK觸發器,可以實現復雜的時序控制功能。

2. 頻率分析電路

在頻率分析電路中,JK觸發器可以用于測量信號的頻率和周期。通過計數一定時間內信號的變化次數,可以計算出信號的頻率;而通過測量信號從一種狀態變化到另一種狀態所需的時間,可以計算出信號的周期。

3. 數碼集成電路

在數碼集成電路中,JK觸發器常用于存儲二進制信息。在計算機的寄存器中,JK觸發器可以存儲和處理大量的二進制數據,實現數據的讀寫和傳輸。

五、總結

JK觸發器作為數字電路中的一種重要存儲器件,具有置0、置1、翻轉和保持四種功能。其內部結構由兩個與非門構成的正反饋回路實現記憶功能,而工作原理則依賴于時鐘信號的邊沿觸發。JK觸發器具有通用性強、靈活性高、抗干擾能力強和高速工作性能等優點,在時序電路、頻率分析電路、數碼集成電路等多種場合中具有廣泛的應用價值。通過深入理解和靈活應用JK觸發器的原理和功能,我們可以設計出更加復雜和高效的數字電路系統。

-

NAND

+關注

關注

16文章

1685瀏覽量

136246 -

JK觸發器

+關注

關注

1文章

43瀏覽量

15940 -

數字電路

+關注

關注

193文章

1608瀏覽量

80693

發布評論請先 登錄

相關推薦

jk觸發器是什么原理_jk觸發器特性表和狀態轉換圖

JK觸發器的原理和功能

JK觸發器的原理和功能

評論