接口處理

top接口

output system_i2c_0_io_sda_writeEnable,

output system_i2c_0_io_sda_write,

input system_i2c_0_io_sda_read,

output system_i2c_0_io_scl_writeEnable,

output system_i2c_0_io_scl_write,

input system_i2c_0_io_scl_read,

soc接口處理

.system_i2c_0_io_sda_write(system_i2c_0_io_sda_write),

.system_i2c_0_io_sda_read(system_i2c_0_io_sda_read),

.system_i2c_0_io_scl_write(system_i2c_0_io_scl_write),

.system_i2c_0_io_scl_read(system_i2c_0_io_scl_read),

WriteEnable信號的處理

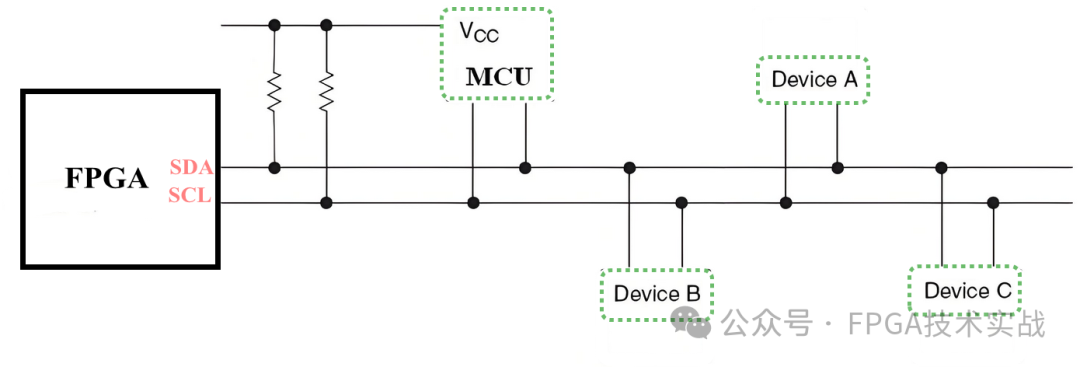

I2C的SDA和SCL對應FPGA雙向IO,需設置為弱上拉。

I2C對應的三態門的OE信號:需要賦值為I2C SDA/SCL的write信號;rtl中的表述如下:

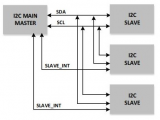

主要原因在于:i2c的通信過程中,當總線空閑時,兩根線均為高電平。連到總線上的任一器件輸出的低電平,都將使總線的信號變低,即各器件的SDA及SCL都是線"與"關系。

2)引腳在輸出信號的同時還將引腳上的電平進行檢測,檢測是否與剛才輸出一致,為"時鐘同步"和"總線仲裁"提供了硬件基礎。

assign system_i2c_0_io_sda_writeEnable = !system_i2c_0_io_sda_write;

assign system_i2c_0_io_scl_writeEnable = !system_i2c_0_io_scl_write;

Interface配置示例

I2C寄存器設置

在I2C的設置中第一步是要配置寄存器。寄存器的說明在ds文檔中。

tsuData中,1代表10ns;

Timeout中,1表示10ns

tLow和tHigh的1代表10ns

10.1.3 軟件部分(Risc V)

l I2C通信主要包括以下幾個部分:

1、主設備發送起始位(Start)

2、主/從發送數據(TxData)(注:軟件處理時,主發送從設備的地址和讀/寫位,與發送數據處理方式相同)

3、主/從接收數據(RxData)

4、主/從發送應答信號(ACK)

5、主設備發送停止位(Stop)

l 對應的C函數:

1、主設備發送起始位(Start)

i2c_masterStartBlocking(I2C_CTRL);//master send start signal2、主/從發送數據(TxData)

i2c_txByte(I2C_CTRL, 0xC0);//master/slave send data3、主/從接收數據(RxData)

i2c_rxData(I2C_CTRL)//master/slave receive data4、主/從發送應答信號(ACK)

i2c_txAckBlocking(I2C_CTRL);//master/slave send ACKi2c_txNackBlocking(I2C_CTRL);//master/slave send NaCK#(不需要發送ACK,但是需要等待一個應答周期的時候,用Nack函數)

5、主設備發送停止位(Stop)

i2c_masterStopBlocking(I2C_CTRL);//master send stopl 小結:

RISC V中提供的關于I2C的函數,相當于把I2C通信過程中各個狀態進行了分解的,上述提到的各個函數功能,除了必須通過I2C主設備實現的功能:發送start和stop之外,函數本身并沒有主從之分;

當需要RISC V中的I2C做從設備時,只需監控總線狀態(如是否接收到有效的數據等),同時調用對應的函數,給主設備發送應答信號,根據主設備提供的指令,接收/發送相應的數據即可;

硬件驗證平臺

原文標題:RISC V的I2C操作

文章出處:【微信公眾號:易靈思FPGA技術交流】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

602991

發布評論請先 登錄

相關推薦

簡單認識I2C通信協議

如何通過cyusb3014的i2c操作界面操作ads1119的i2c接口?

什么是I2C協議 I2C總線的控制邏輯

i2c接口由哪幾根線組成 i2c接口可以接哪些器件

RISC V的I2C操作

RISC V的I2C操作

評論