低壓降線性穩(wěn)壓器(LDO)因其工作原理,雖然能以低成本提供高電源質量,但也會不可避免地產生損耗和發(fā)熱問題。面對大壓降、大電流,LDO將長時間處于較高的工作溫度范圍,可能影響其使用壽命和可靠性。因此,通過事先分析和評估LDO在特定工作環(huán)境下的溫度,并采取一定的措施,可以有效地避免芯片在長時間的高溫下發(fā)生熱關斷和老化。

芯片的結溫主要取決于其功耗、散熱條件和環(huán)境溫度。因此,通過選擇不同的封裝版本來降低芯片的結與環(huán)境的熱阻,是一種降低結溫的有效解決方案。

目錄

1. 芯片熱阻介紹

2. 使用熱阻矩陣進行熱分析

2.1. 對θJA的誤解

2.2. 理解ΨJC & θJC

3. 在EVM板上進行LDO結溫和熱阻測試

1. 芯片熱阻介紹

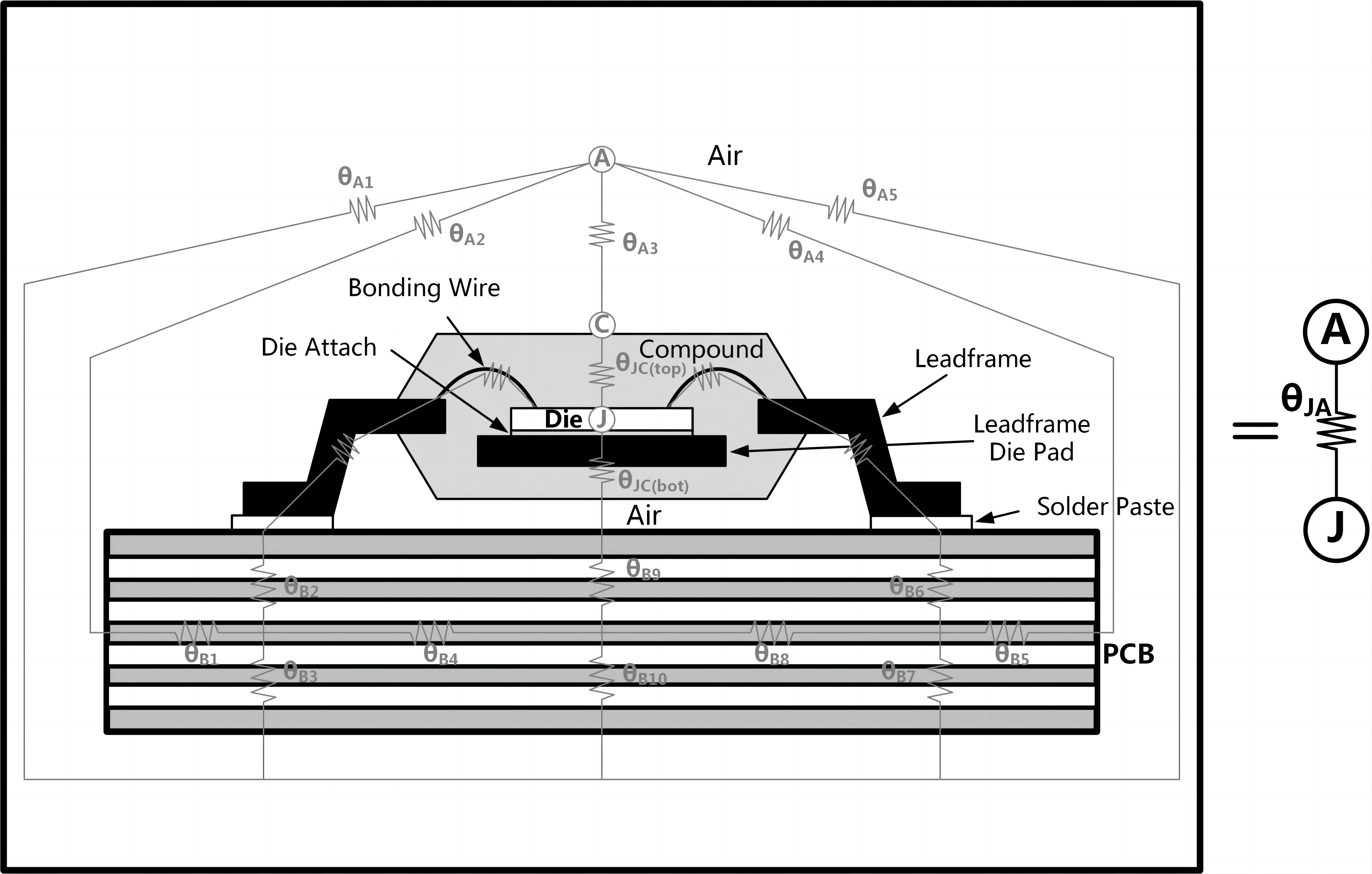

由于芯片結構復雜,通常通過仿真得到熱阻的理論計算值。而在芯片實際工程應用中,工程師們將理論熱阻與實際應用問題相結合,加以歸類,得出一些具有明顯物理意義的熱阻。下圖展示了芯片焊接在PCB上時的熱阻網(wǎng)絡。

圖1 芯片熱阻網(wǎng)絡(來源:納芯微)

圖中,熱量從結向上通過封裝體傳遞到封裝外殼的頂部,它們之間的熱阻之和被稱為θJC(top);熱量從結向下,通過粘合劑、引線框架基島傳遞到底部散熱焊盤,其熱阻之和被稱為θJB;此外,通過圖中所有材料和結構,從結到外部環(huán)境的所有方向的熱量,所有路徑的整體熱阻被稱為θJA。

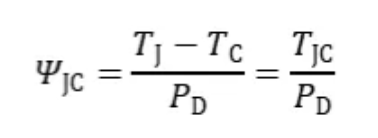

雖然這些熱阻可以通過建模仿真獲得,但由于存在制造誤差及其他原因,可能不甚準確。因此,在工程實踐中,通常通過芯片發(fā)熱和溫差,來計算熱阻。熱阻的定義如下:

(1-1)(來源:納芯微)

這意味著不論是減少芯片的發(fā)熱、改用散熱性能更好的大型封裝、增加散熱器和風扇,還是改進PCB的散熱設計,都可以減少芯片溫升。

2. 使用熱阻矩陣進行熱分析

2.1. 對θJA的誤解

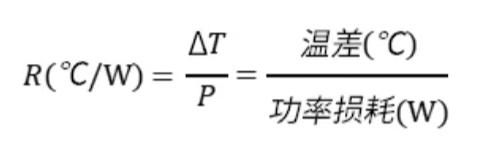

我們可以在芯片的數(shù)據(jù)手冊(datasheet)中找到一個熱阻信息矩陣,其中就包含了上述θJA和θJC(top)等參數(shù)。下表摘自NSR31系列LDO的數(shù)據(jù)手冊。NSR31完整版數(shù)據(jù)手冊官網(wǎng)鏈接:https://www.novosns.com/10v-low-consumption-ldo-685

表1 NSR31系列的熱阻信息(來源:納芯微)

需要注意的是,許多工程師會使用θJA、環(huán)境溫度和芯片功耗,來計算結溫,但這可能會產生較大的計算誤差。

從上節(jié)圖1的θJA定義可以看出,其值不僅由芯片本身決定,還很大程度上取決于具體使用的PCB。不同的應用PCB的散熱面積、層數(shù)、銅厚、板厚、材料、器件布局等方面各不相同,因此,θJA的值在不同的應用PCB上會有很大差異。大多數(shù)工程師都很關注自己PCB上芯片的狀態(tài)。因此,在熱設計中不建議使用θJA,θJA的主要優(yōu)勢在于比較不同封裝類型的熱性能方面。

通常而言,幾乎所有芯片數(shù)據(jù)手冊中的θJA,都是使用行業(yè)標準板測量或仿真而得的示例值。這些行業(yè)標準平臺被稱為JEDEC High-K或JEDEC Low-K板。此外,這些JEDEC 板僅由安裝在3"x3"板上的一個IC器件組成,與實際工程應用中的PCB有顯著差異。

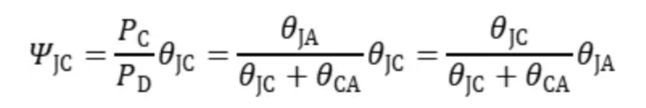

2.2. 理解ΨJC& θJC

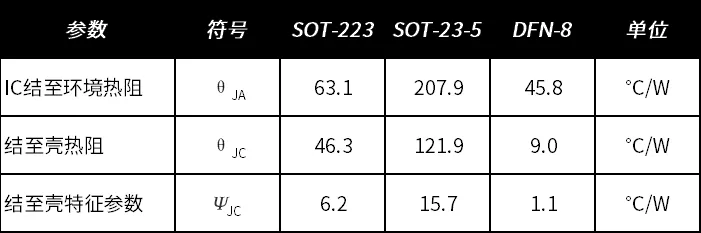

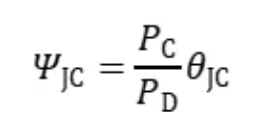

為了解決應用端的實際問題,表中還提供了熱特性參數(shù)Ψ。這是聯(lián)合電子器件工程委員會(JEDEC)在20世紀90年代定義的熱指標。就評估現(xiàn)代封裝器件結溫而言,它是一個更為便利的指標。Ψ代表的是結與參考點之間的溫差與芯片消耗的總功率的比值,它只是一個構造出的參數(shù)。雖然其公式和單位(°C/W)與Rθ非常相似,但Ψ實際上并不是一個“熱阻”參數(shù),其定義如下:

(2-1)(來源:納芯微)

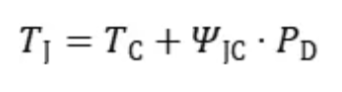

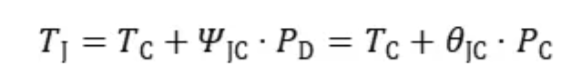

其中,ΨJC是結到殼的熱特性參數(shù),TJC是結到殼的溫差,PD是芯片的總耗散功率。因此,求TJ時,首先要測量外殼溫度TC,計算芯片的總耗散功率PD,再使用以下公式計算:

(2-2)(來源:納芯微)

其中,ΨJC可以通過數(shù)據(jù)手冊中的熱阻信息矩陣獲取。當芯片外部散熱條件固定時,ΨJC與θJC成正比。與不同應用端差異很大的θJA相比,雖然ΨJC也受到PCB散熱能力的影響,但我們可以近似地認為,在大多數(shù)應用中,該影響并不顯著。具體原因如下。

公式(2-2)可以進一步寫為:

(2-3)(來源:納芯微)

式中:PC是從結向上通過封裝體傳遞到封裝外殼頂部的熱功率。由此可得:

(2-4)(來源:納芯微)

即ΨJC與θJA成正比,其值為從結到殼頂部的熱功率與芯片總耗散功率的比值。

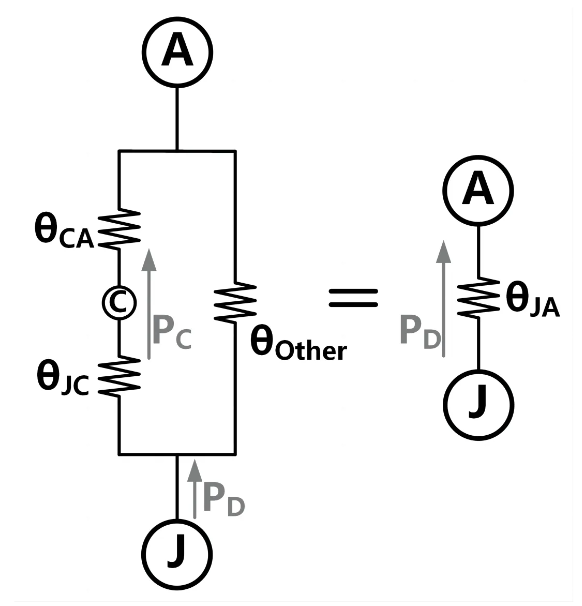

圖2 芯片熱阻網(wǎng)絡簡圖(來源:納芯微)

如圖2所示,根據(jù)熱阻網(wǎng)絡的“并聯(lián)電阻分流公式”關系,功率比相當于熱阻比的倒數(shù):

(2-5)(來源:納芯微)

式中:θCA為殼到環(huán)境的熱阻。當沒有在芯片表面安裝散熱器時,θCA遠大于θJC。由此可得,ΨJC小于θJA,因此,在工程上的實際PCB中,使用ΨJC估算結溫的誤差,遠小于使用θJA來估算的誤差。

3. 在EVM板上進行LDO結溫和熱阻測試

由于集成電路外部被塑封料(mold compound)包裹,結沒有暴露在外,因此我們無法通過熱電偶或紅外溫度計,直接測量芯片內部結點的溫度。對于許多大型封裝集成電路,例如CPU或GPU,通常會集成一個熱傳感器,用于測量TJ。但對于小型封裝集成電路,由于受到尺寸和成本的限制,大都沒有這種TJ傳感器的功能。因此,我們必須通過測試和熱分析來估算TJ。

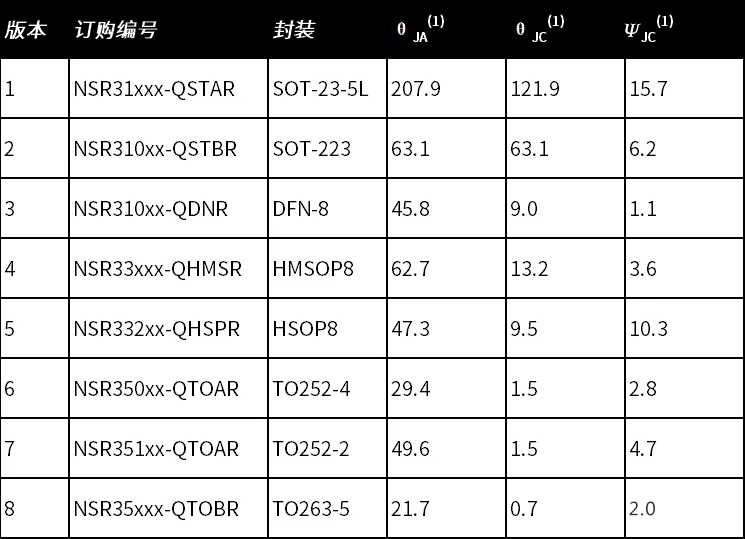

NSR31/33/35系列LDO有8種封裝,具體信息如表2所示。采用不同封裝的各類熱阻已在芯片數(shù)據(jù)手冊的熱阻矩陣中標明。其信息概述如下。

表2 NSR3x系列的熱阻信息(來源:納芯微)

(1)熱數(shù)據(jù)基于:JEDEC標準高K型材、JESD 51-7、四層板。

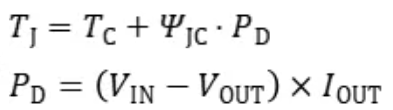

表2中所有參數(shù)均根據(jù)JEDEC標準獲得。通過表θJA比較可知,SOT-23-5L封裝的散熱性能最差,TO263-5封裝的散熱性能最好。當需要獲取LDO在特定應用電路板上的結溫時,可以使用公式(2-2):

式中:

(3-1)(來源:納芯微)

式中:VIN代表LDO輸入電壓,VOUT代表LDO輸出電壓,IOUT代表LDO輸出電流。

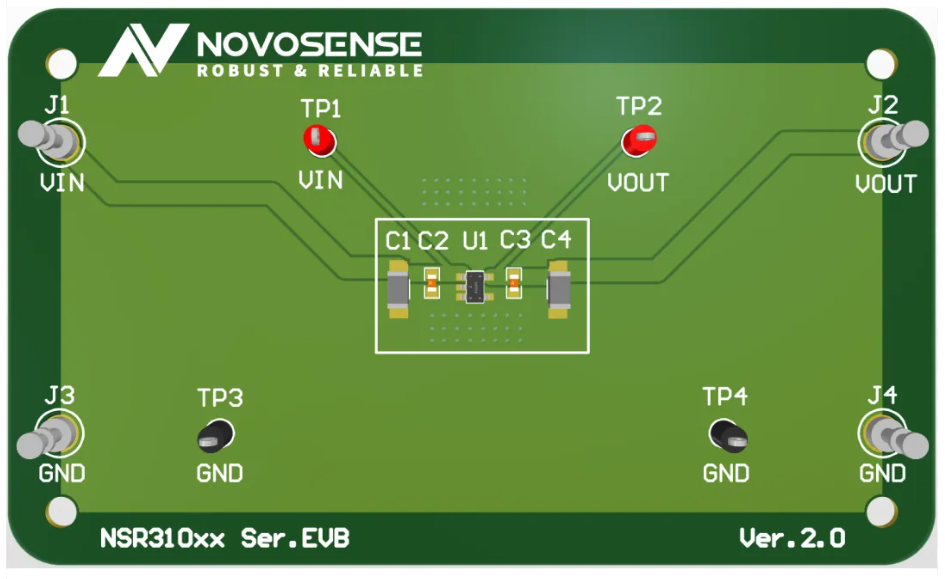

接下來以NSR31050-QSTAR為例,在EVM板上測量和計算其結溫和實際熱阻θ'JA,以供參考。具體來說,EVM板采用四層設計(88mm x 53mm),銅厚為1盎司,總散熱面積約為4600平方毫米,如圖3所示。

圖3 NSR31050-QSTAR EVM板(來源:納芯微)

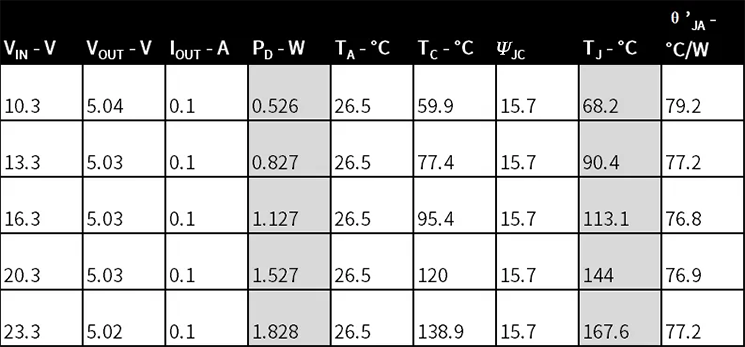

在室溫通風恒定的情況下,通過給LDO施加一定的電壓和負載,可以將其功耗從0W增加到接近熱關斷。在不同功耗設置下,讓芯片工作5分鐘溫度穩(wěn)定后,使用手持式紅外測溫儀測量芯片頂殼的溫度。利用環(huán)境溫度、殼溫、功耗和ΨJC的公式,來對EVM板上芯片的結溫和熱阻θ'JA進行估算。結果如表3所示。

表3 NSR3x系列的熱信息(來源:納芯微)

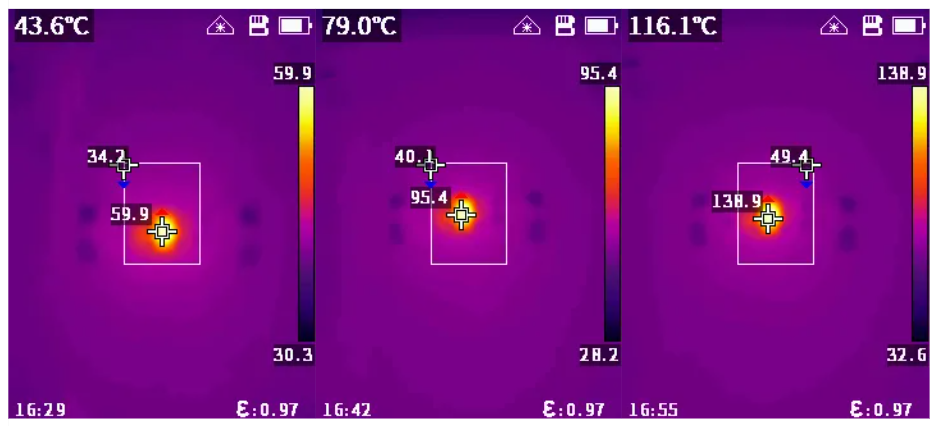

圖4 部分殼溫的紅外測量結果(來源:納芯微)

從表3可以看出,在此EVM板上,測得的結到環(huán)境的熱阻θ'JA約為77.5°C/W,遠低于JEDEC 標準的207.9°C/W。

綜上所述,在實際應用中,芯片存在多種熱傳導途徑,熱量亦通過多個通道傳遞。我們很難像估算總功耗一樣,準確得到由特定途徑傳導的功耗。因此,熱特性參數(shù)ΨJC更適合用于估算結溫,利用熱特性參數(shù)ΨJC,同時結合公式(3-1)來估算結溫更為準確和嚴謹。

審核編輯 黃宇

-

ldo

+關注

關注

35文章

2312瀏覽量

156204 -

熱阻

+關注

關注

1文章

114瀏覽量

16842 -

矩陣

+關注

關注

1文章

434瀏覽量

35198

發(fā)布評論請先 登錄

LED封裝器件熱阻測試與散熱能力評估

MOSFET熱阻參數(shù)解讀

功率器件熱設計基礎知識

什么是熱重分析(TGA)

同步熱分析儀:探索物質熱特性的利器

電源設計之對熱阻的認識

ADS58C20熱阻有頂面(9.3度/W)和底面(0.5度/W),請問一下折算為一面的熱阻怎么計算?

導熱界面材料對降低接觸熱阻的影響分析

功率器件的熱設計基礎(二)——熱阻的串聯(lián)和并聯(lián)

評論