靜態驗證與“設計左移”

近年來IC設計的規模和復雜度不斷增大,產品的迭代周期越來越短,傳統的驗證方式已經難以滿足設計團隊的要求。在“設計左移”這一理念的趨勢下,設計流程和方法學不斷進行創新和優化,其中,具備“設計左移”思想的靜態驗證方法實現了將原本在仿真、綜合、布局布線階段出現的問題移動到RTL階段進行檢測和分析,幫助IC設計者在早期發現和診斷設計缺陷,縮短芯片整體開發周期,降低成本。

不同于其他驗證方式,靜態驗證是通過分析設計的源代碼來發現設計中的錯誤。靜態驗證是對硬件設計經驗的總結提煉,是硬件設計的知識庫,硬件設計知識涵蓋了語法分析、可綜合性分析、時序優化技術、功耗優化技術、面積優化技術、可測性分析技術、跨時鐘分析技術等許多方面。

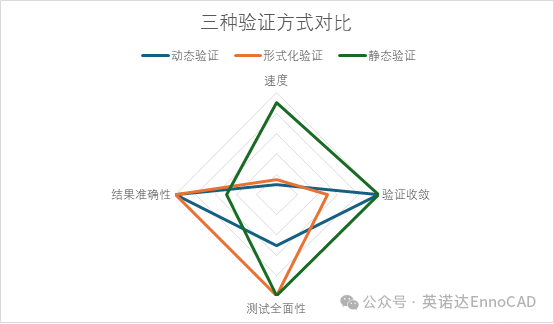

靜態驗證是IC設計驗證方法之一,是確保高質量設計輸出的關鍵步驟。相比需要激勵進行仿真的動態驗證(如軟件仿真、硬件仿真加速)與形式化驗證(如等價驗證、模型檢測)手段,靜態驗證(如STA、Lint、CDC等)可以在成本、速度、覆蓋率等方面彌補傳統驗證手段的不足。

Lint靜態驗證工具

Lint工具是一款代碼檢測工具,也是最常見的靜態驗證工具之一。通常設計團隊在編寫Verilog等代碼時,會犯一些無意識的代碼錯誤,或產生一些雖語法正確但后期可能有隱患的代碼。對于這些問題,設計團隊要在第一時間解決,否則將直接導致編譯或運行錯誤,影響開發效率和質量。

Lint本義是指除掉織物上的毛線和短絨,后來引申到計算機領域,這個概念最早源于1979年貝爾實驗室開發的針對C語言的Lint程序,它能夠進行更深入的檢查錯誤,找出編譯器可能忽略的潛在問題。

在芯片設計中,Lint工具可在RTL階段對HDL代碼的naming、coding style、structure、綜合以及仿真mismatch等問題進行檢查。Lint分析節約整體流程時間提升開發效率主要體現在3方面:

在RTL編碼階段即可進行驗證,無需等待驗證環境的搭建;

運行速度快;

直接從根因發現問題。

比如電路中的管腳的懸空輸入(floating input),往往會造成功耗損失,增加電路噪聲,更致命的是功能上的錯誤。這些錯誤如果在邏輯綜合或后仿真階段才被檢查出來,需要耗費大量的時間和精力溯源并修改相關的RTL代碼。如果一個人為的疏忽,直到芯片流片后都沒有發現,那么芯片流片后回來可能會變成產品功能缺失。而避免這樣的錯誤也很容易,在RTL設計階段使用Lint工具找到該問題并修改floating input就可以了。

作為一款靜態驗證工具,Lint非但不會對工程師現有的設計流程造成任何阻礙,反而能夠優化現有的流程,通過在早期發現設計錯誤并改善代碼質量,Lint可以幫助工程師更快地理解和解決復雜設計中的問題,實現效率與質量的雙重提升。

關于英諾達

英諾達(成都)電子科技有限公司是一家由行業頂尖資深人士創立的本土EDA企業,公司堅持以客戶需求為導向,幫助客戶實現價值最大化,為中國半導體產業提供卓越的EDA解決方案。公司的長期目標是通過EDA工具的研發和上云實踐,參與國產EDA完整工具鏈布局并探索適合中國國情的工業軟件上云的路徑與模式,賦能半導體產業高質量發展。英諾達首款自主研發的EnFortius?凝鋒?系列低功耗EDA工具,可有效幫助IC設計工程師定位并分析低功耗設計相關問題。在靜態驗證領域,EnAltius?昂屹?系列工具將在設計流程的早期增強可預測性,幫助IC設計工程師做出最優決策。英諾達的EnCitius?曜奇? SVS系統驗證平臺則利用EDA上云的優勢,為客戶打通驗證資源的渠道,提供全面的SoC及系統級驗證的一站式解決方案,提高芯片設計效率。此外,英諾達還可提供完整、可定制的前/后端設計服務。

-

IC設計

+關注

關注

38文章

1295瀏覽量

103918 -

靜態驗證

+關注

關注

0文章

7瀏覽量

5984 -

英諾達

+關注

關注

1文章

29瀏覽量

1957

原文標題:靜態驗證與設計左移:Lint工具如何為IC設計提質增效

文章出處:【微信號:gh_387c27f737c1,微信公眾號:英諾達EnnoCAD】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

C語言——代碼檢查工具

ASIC靜態驗證方法

靜態時序分析在IC設計中的應用

Lint靜態驗證工具如何助力IC設計

Lint靜態驗證工具如何助力IC設計

評論