ADC(Analog-to-Digital Converter,模數轉換器)采樣保持電路是ADC轉換過程中的一個重要組成部分,其工作原理和技術指標對于確保ADC轉換的精度和可靠性至關重要。以下是對ADC采樣保持電路工作原理和技術指標的詳細闡述。

一、ADC采樣保持電路的工作原理

ADC采樣保持電路,又稱為采樣保持放大器(Sample and Hold Amplifier,簡稱S/H),主要作用是在ADC進行模數轉換時,保持輸入模擬信號的電平值在一段時間內基本不變,以確保轉換的準確性。其工作原理可以概括為兩個階段:采樣階段和保持階段。

1. 采樣階段

在采樣階段,采樣保持電路的開關(通常是模擬開關)處于導通狀態,允許輸入模擬信號通過開關進入保持電容。此時,電容開始充電,其充電速度取決于電容的容值、開關的導通電阻以及輸入信號的幅度和頻率。如果電容值較小,電容可以在很短的時間內完成充電,使得輸出信號能夠緊密跟隨輸入信號的變化。在這個階段,采樣保持電路的輸出信號基本上與輸入信號保持一致。

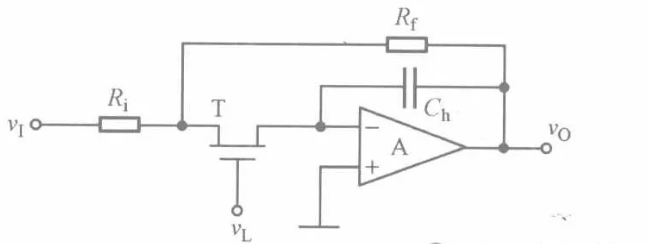

N溝道MOS管T作為采樣開關用。當控制信號比為高電平時,T導通,輸入信號VL經電阻Ri和T向電容Ch充電。若取Ri=Rf則充電結束后Vo=-Vi=VC。當控制信號返回低電平,T截止。由于Ch無放電回路,所以Vo的數值被保存下來。缺點:采樣過程中需要通過Ri和T向Ch充電,所以使采樣速度受到了限制。同時,Ri的數值又不允許取得很小,否則會進一步降低采樣電路的輸入電阻。

2. 保持階段

當采樣階段結束后,采樣保持電路的開關斷開,此時電容與輸入信號隔離,開始進入保持階段。由于開關的斷開以及集成運放(通常作為信號跟隨器使用)的輸入端呈高阻狀態,電容的放電變得非常緩慢。因此,即使輸入信號發生變化,輸出信號也會保持為斷開瞬間的信號電平值,直到下一次采樣開始。這樣,就為ADC提供了足夠的時間來完成模數轉換過程,而無需擔心輸入信號的變化對轉換結果的影響。

二、ADC采樣保持電路的技術指標

ADC采樣保持電路的技術指標是衡量其性能優劣的重要依據,主要包括以下幾個方面:

1. 偏移電壓(Offset Voltage)

偏移電壓是指在采樣模式下,當輸入端電壓為零時,輸出端的輸出電壓值。偏移電壓的存在會引入額外的誤差,影響ADC的轉換精度。因此,為了保證ADC能夠準確地采樣,偏移電壓的值應當盡可能小,并滿足系統對精度的要求。

2. 最大變化頻率(Maximum Frequency of Change)

最大變化頻率是指在采樣模式下,輸出電壓能夠跟隨輸入信號變化的最高頻率。這個頻率值受到保持電容容值大小的影響。如果電容容值較小,電容的充電時間就較短,能夠較好地跟蹤變化頻率較高的信號;反之,如果電容容值較大,電容的充電時間就較長,可能無法及時跟蹤高頻信號的變化。因此,在選擇保持電容的容值時,需要根據實際應用場景綜合考慮。

3. 降壓速率(Droop Rate)

降壓速率是指在保持模式下,輸出端的輸出電壓值隨輸入時間變化的速率。降壓速率越小,說明電容在保持狀態下的放電越慢,輸出信號的穩定性越好。然而,過小的降壓速率也可能導致系統響應速度變慢,影響實時性。因此,在設計采樣保持電路時,需要權衡降壓速率和響應速度之間的關系。

4. 饋通衰減量(Feedthrough Attenuation)

饋通衰減量是指在保持模式下,輸入信號的電壓值到經過采樣保持電路后,在輸出端輸出時的減少量。饋通衰減量越小,說明電路對輸入信號的衰減越小,輸出信號的保真度越高。為了使ADC能夠準確地采樣出信號,饋通衰減量應小于ADC的最低有效位(LSB)的1/2。

5. 采樣時間(Sampling Time)

采樣時間是指當電路由保持狀態切換為采樣狀態時,獲取輸入信號電壓值所需的最大時間。采樣時間越短,說明電路對輸入信號的響應速度越快。然而,過短的采樣時間也可能導致采樣結果不穩定或引入噪聲。因此,在設置采樣時間時,需要根據ADC的轉換速率和輸入信號的穩定性綜合考慮。

6. 孔徑延時(Aperture Delay)

孔徑延時是指當電路由采樣狀態變為保持狀態時,電容由充電開始到電壓穩定所經歷的時間。孔徑延時是一個十分重要的技術指標,它直接影響著采樣的速率和精確度。較短的孔徑延時意味著電路能夠更快地進入保持狀態并穩定輸出電壓值,從而提高采樣精度和響應速度。

三、結論

ADC采樣保持電路作為ADC轉換過程中的關鍵組成部分,其工作原理和技術指標對于確保ADC轉換的精度和可靠性至關重要。通過合理設計采樣保持電路的參數和結構,可以優化其性能并滿足不同應用場景的需求。同時,隨著半導體工藝和集成電路技術的不斷發展,未來ADC采樣保持電路的性能將得到進一步提升和完善。

-

adc

+關注

關注

99文章

6565瀏覽量

546606 -

模數轉換器

+關注

關注

26文章

3237瀏覽量

127232 -

采樣保持電路

+關注

關注

3文章

13瀏覽量

20001

發布評論請先 登錄

相關推薦

常被忽略的九項ADC技術指標

常被忽略的九項ADC技術指標

9個常被忽略的ADC技術指標

ADC工作原理、類型及主要技術指標資料下載

ADC采樣保持電路的工作原理和技術指標

ADC采樣保持電路的工作原理和技術指標

評論