Vivado 結果是否可重復用于相同的工具輸入?

解決方案大多數情況下是可以的,Vivado 應該可在涉及相同應用的運行之間生成相同的結果:

-

設計源

-

約束

-

Tcl 腳本及命令順序

-

工具與命令選項

-

Vivado 軟件版本

-

多線程設置

這適用于從 HDL 綜合到比特流生成的設計流程的各個環節。例如,構建腳本反復在同一系統或相似配置的機器上運行時,應該能生成相同的結果。

不同操作系統的結果通常可重復,但也不一定,特別是在使用 Linux 和 Windows 操作系統的情況下。

注意確定性

術語“可重復性”和“確定性”通常可交替使用,這種說法是不對的。Vivado 使用多線程來并行執行,因此它在定義上是不確定的。然而,Vivado 中的多線程可通過編程實現同步,因而多線程執行可重復。注意,除了多線程外,Vivado 也管理 OS 系統調用及內存管理等可導致不確定性的其它因數。

確定重復性問題

有分歧的運行最常見的癥狀是布線后時序結果的不同。如果您懷疑某個不可重復性的情況,并驗證工具輸入是完全相同,就可使用校驗和來進一步驗證分歧。Vivado 在每個實現方案命令的各個中間階段,都會在日志中報告一個校驗和,這是一個基于設計網表及物理數據的簽名。校驗和可以在不同的運行之間比較,校驗和不匹配可幫助發現哪里的結果有分歧。

實例:以下校驗和開始出現分歧,因此永遠不會收斂。如果所有輸入都是完全相同的,那這很可能就是一個可重復性問題。

檢查點與內存中的運行

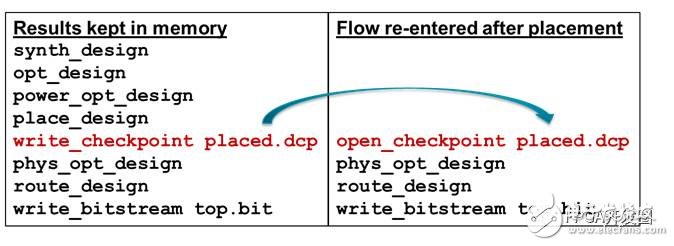

與同等意義的內存內設計流程相比,檢查點應生成可重復性的結果。請考慮以下命令順序,一個運行內存中的整個設計流程,另一個則使用放置的檢查點通過 phys_opt_design 命令再次從內存中的流程進入該流程。

這兩個運行應該給出相同的結果。盡管在執行 open_checkpoint 命令后,校驗和可能因為網表的排序差異而不同,但在第一次執行 phys_opt_design 命令后,校驗和應該可以收斂:

在運行之前,每一個執行命令都會自動排序,以確保網表的一致性,這樣結果就不會因網表差異而出現分歧。

最大限度提高可重復性

如果可重復性對于您的設計環境至關重要,下面的操作可幫助您最大限度地提高可重復性:

在單線程模式下運行。

在不同運行之間使用不同數量的 CPU 時,同步線程可能會按照不同的順序執行運算并造成有分歧的結果,即便運行使用相同的機器或系統也是如此。

要在單線程模式下運行,請使用:

set_param general.maxThreads 1

這不僅可禁用多線程,而且還可消除相關可重復性問題。

在相同機器上運行或者在使用相同操作系統的機器上運行。

這不僅可降低遇到內核運行方式所帶來的不可重復性的概率,而且還可從一個系統到另一個系統實現系統調用,特別是在使用 Windows 和 Linux 操作系統的情況下。

以下操作可進一步降低這一概率

1) 微調環境,消除下列情況:

-

同一操作系統的不同版本

-

不同的服務包級別 (Windows)

-

不同分銷或不同補丁級別 (Linux)

2) 消除計算硬件差異:

-

使用相同的通用物理及虛擬存儲器容量。

-

使用相同的處理器架構和相同數量的內核。

-

如果使用的是虛擬機,則要保證配置完全相同。

報告不可重復性問題

如果您遇到了輸入完全相同的不可重復性問題(如解決方案說明中所述),請打開服務請求并提供一個可演示該問題的測試案例。

沒有測試案例,可能很難確定并修復任務問題,但它可幫助提供盡可能多的信息。

Linux 和 Windows 之間偶爾會出現不可重復性問題,我們建議限制 Vivado 只在 Linux 上運行或只在 Windows 上運行。

-

Linux

+關注

關注

87文章

11519瀏覽量

213995 -

WINDOWS

+關注

關注

4文章

3615瀏覽量

91500 -

Vivado

+關注

關注

19文章

835瀏覽量

68872

原文標題:【專家坐堂Q&A】Vivado 結果是否可重復用于相同的工具輸入?

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Vivado 2017.4和2018.2不同的Linux和Windows之間的實現結果

我應該使用什么操作系統?

(良哥獨創)linux操作系統裝回windows操作系統

Windows XP操作系統 ppt課件

Linux是什么?這種操作系統為何如此流行?

Linux和Windows操作系統你更希望用哪個?

Windows 10操作系統會有專門的Linux子系統

怎樣實現在linux系統中對windows系統的遠程操作?

Linux操作系統與Windows操作系統的五大區別

Windows和Linux操作系統的流式處理API

Linux與Windows服務器操作系統有什么區別?

每次Vivado編譯的結果都一樣嗎

評論