LDO(Low Dropout Regulator,低壓差線性穩壓器)是一種常用的電源管理芯片,它能夠在較小的輸入輸出電壓差下穩定輸出電壓,廣泛應用于各種電子設備中。然而,在LDO的上電過程中,有時會出現一種現象,即輸出電壓會短暫地超過其設定值,這種現象被稱為“上電輸出過沖”。

一、定義與現象描述

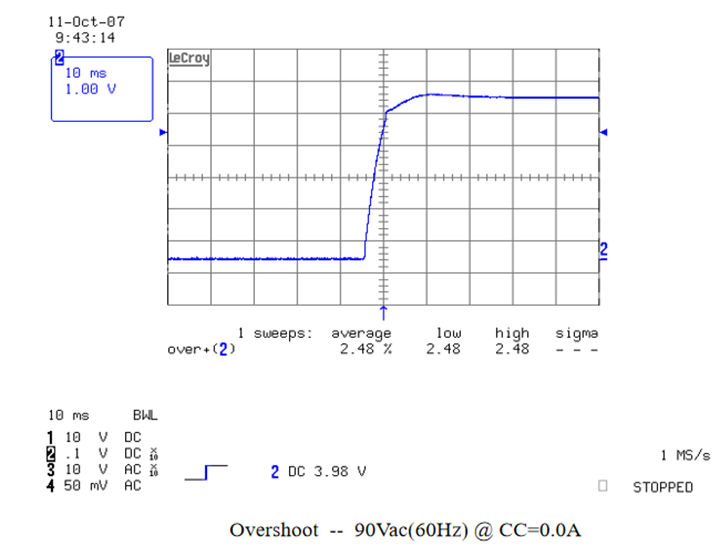

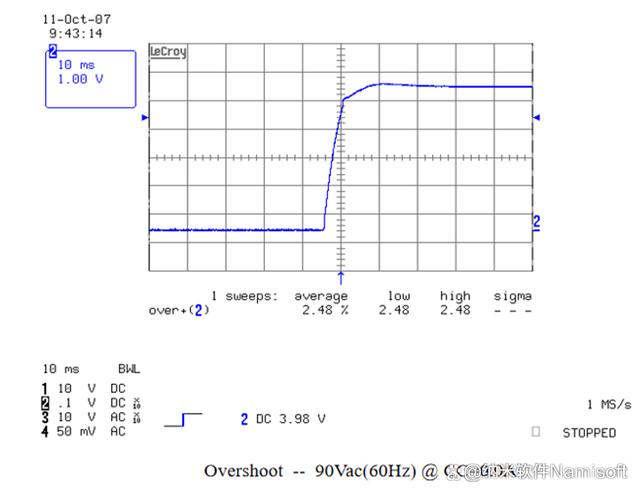

定義 :LDO上電輸出過沖是指在上電瞬間,LDO的輸出電壓會短暫地超過其正常設定值,形成一個尖峰脈沖。這個尖峰脈沖的幅度和持續時間取決于多種因素,包括LDO的內部設計、外部電路配置以及上電條件等。

現象描述 :在LDO上電時,由于電源電壓的突然施加,以及LDO內部電路和外部電容的充電過程,輸出電壓可能會在短時間內迅速上升并超過其設定值。這個過沖現象通常會在幾十微秒到幾毫秒的時間內發生,并隨后逐漸衰減至正常設定值。

二、產生原因

LDO上電輸出過沖的產生原因復雜多樣,主要包括以下幾個方面:

- 輸出端電容的寄生內阻(ESR) :

- 輸出端電容的ESR(Equivalent Series Resistance,等效串聯電阻)是影響LDO上電輸出過沖的關鍵因素之一。當ESR過小時,上電瞬間電容被視為短路,導致輸出電壓被拉低至接近零。此時,LDO內部的負反饋電路會進行大幅度的電壓補償,使輸出電壓瞬間升高,從而產生過沖現象。

- 內部反饋回路的響應時間 :

- LDO內部通常包含負反饋回路,用于穩定輸出電壓。然而,這個反饋回路需要一定的響應時間來響應輸出電壓的變化。在上電瞬間,由于輸出電壓的快速變化,反饋回路可能來不及完全調節,導致輸出電壓出現過沖。

- 輸入電壓的階躍變化 :

- 當輸入電壓在上電時發生階躍變化時(如熱插拔或接觸不良導致的電壓突變),若輸入電壓的變化速率超出LDO內部環路的響應速度,也會導致輸出端電壓短暫出現高于設定值的現象。

- 外部電路設計 :

- 外部電路的設計也會影響LDO的上電輸出過沖。例如,輸出電容的容量和類型、輸入濾波電路的設計等都會對過沖現象產生影響。

三、影響與危害

LDO上電輸出過沖雖然是一個短暫的現象,但其對電子設備的影響和危害卻不容忽視:

- 損壞后端設備 :

- 如果過沖電壓超過后端設備的極限耐壓值,可能會導致設備損壞或性能下降。特別是在一些對電壓敏感的應用場景中(如精密儀器、高速數字電路等),過沖現象可能帶來嚴重的后果。

- 影響系統穩定性 :

- 增加設計難度和成本 :

- 為了避免過沖現象對系統的影響,設計者需要在電路設計中采取一系列措施來抑制過沖。這些措施可能會增加設計的復雜性和成本。

四、抑制措施

針對LDO上電輸出過沖現象,可以采取以下措施進行抑制:

- 選擇合適的輸出電容 :

- 選擇具有適當ESR值的輸出電容可以有效抑制過沖現象。一般來說,ESR值不宜過小也不宜過大,需要根據具體的應用場景和LDO的規格要求進行選擇。

- 優化外部電路設計 :

- 通過優化外部電路的設計(如增加輸入濾波電路、調整電容布局和走線等)來減少輸入電壓的波動和噪聲干擾,從而降低過沖現象的發生概率。

- 使用軟啟動電路 :

- 在LDO的輸入端添加軟啟動電路可以減緩輸入電壓的上升速率,使LDO有足夠的時間來響應電壓變化并穩定輸出電壓。這樣可以有效避免過沖現象的發生。

- 添加欠壓保護電路 :

- 在LDO的輸入端添加欠壓保護電路可以在輸入電壓低于一定閾值時切斷電源供應或降低輸出電壓的幅度,從而避免過沖現象對后端設備造成損害。

- 選擇高性能LDO :

- 選擇具有快速響應時間和高精度穩壓性能的LDO芯片可以在一定程度上減少過沖現象的發生。這些高性能LDO芯片通常具有更先進的內部電路設計和更優化的控制算法。

五、結論

綜上所述,LDO上電輸出過沖是一個需要引起設計者重視的問題。通過深入了解其產生原因和影響機制,并采取有效的抑制措施來降低過沖現象的發生概率和危害程度,可以確保電子設備的穩定可靠運行。在未來的設計中,我們應該更加注重對LDO上電輸出過沖現象的研究和應對策略的制定,以推動電子技術的不斷發展和進步。

-

ldo

+關注

關注

35文章

2286瀏覽量

155705 -

線性穩壓器

+關注

關注

5文章

898瀏覽量

67868 -

電源管理芯片

+關注

關注

21文章

781瀏覽量

53519

發布評論請先 登錄

Buck輸出過沖產生原因及改善措施

opa4348上電電路輸出有6.5ms的過沖,由什么原因引起的?

DAC8552 VDD在上電或斷電過程中,Pin3和Pin4腳有輸出過沖的原因?

揭秘TDK-Lambda可編程電源輸出過沖抑制的隱藏屬性

壓力變送器輸出過大的原因?怎么解決?

PCA9450CHNY LDO1(1.8V) 產生2.6V而不是1.8V的原因?

無刷電機驅動方案公司常用的上電無過沖LDO

高壓低功耗LDO BL9157的典型應用

輸出電壓過沖怎么測試?電源測試系統如何測試電源模塊輸出過沖?

輸出過沖原因及改善措施

評論