在嘗試將鎖相環(PLL)鎖定時,你是否碰到過麻煩?草率的判斷會延長調試過程,調試過程變得更加單調乏味。根據以下驗證通行與建立鎖定的程序,調試過程可以變得非常簡單。第1步:驗證通信第一步是驗證PLL響應編程的能力。如果PLL沒有鎖定,無法讀回,則嘗試發送需要最小量硬件命令工作的軟件命令。一種方法是通過軟件(而非引腳)調節PLL的通電斷電尋找引腳的可預測電流變化或偏置電壓電平變化。許多PLL在其輸入(OSCin)引腳的電平在通電時為Vcc/2,在斷電時為0V。如果PLL集成了壓控振蕩器(VCO),則查看低壓差(LDO)輸出引腳電壓是否對通電和斷電命令做出反應。還可能可以切換輸入/輸出 (I/O)引腳,比如許多LMX系列PLL的MUXout引腳。如果采用上述方法能夠驗證通信,就可以繼續嘗試進行鎖定。如果無法驗證通信,則查找常見的原因,例如以下原因:

-

編程串行

-

鎖存使能(也稱為芯片選擇條(CSB))過高

-

對軟件輸入的低通濾波過多

-

與串行外圍設備接口總線(SPI)存在時序問題

-

電源引腳焊接有誤

第2步:建立鎖定驗證通信后,下一步就是嘗試對PLL進行鎖定。下面是PLL無法鎖定的一些更常見的原因:

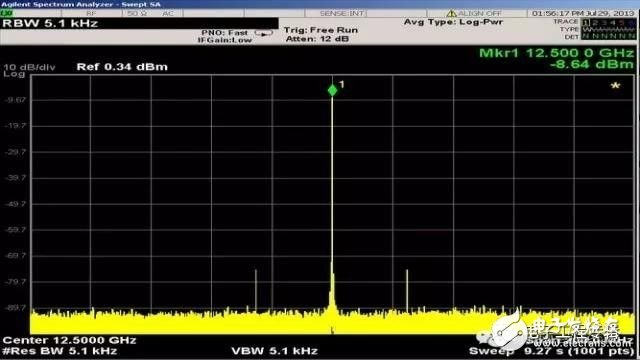

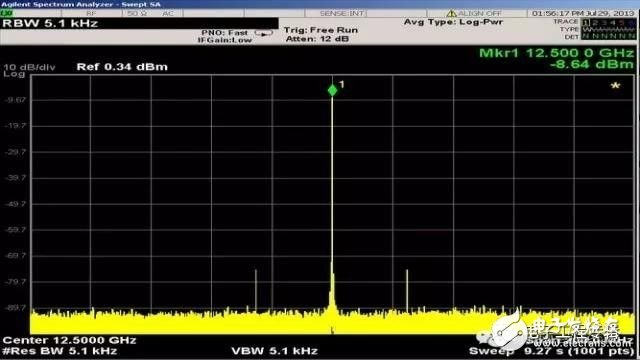

如果配置有誤,鎖定檢測引腳會在實際已經鎖定的情況下顯示出PLL未鎖定。可以通過查看頻譜分析儀輸出或VCO調諧電壓驗證這一情況。

向PLL發送錯誤的信息會很容易導致無法鎖定。一些常見的編程錯誤包括:VCO編程頻率超出范圍、VCO校準設置不正確或寄存器時序有誤。

對于集成VCO的PLL而言,頻率范圍通常分成幾個不同的頻段。錯誤的編程會導致VCO鎖定錯誤的頻段。對特定寄存器的編程通常會啟動VCO校準;因此必須確定在編程此寄存器時,其他軟件和硬件(尤其是基準輸入)狀態正確,以確保校準正常工作。

如果VCO輸入或基準輸入因電源水平較低、壓擺率較低、匹配較差或諧波較高而存在問題,會導致PLL打開鎖定。大多數PLL有方法輸出內部頻率計數器的實際頻率輸出,將其發送到引腳。

可以通過查看調諧電壓或切換鑒相器兩極,根據頻率變化確定連接或短路。

如果降低電荷泵電流導致PLL鎖定通常是不穩定的表現,但是僅憑這項技術不起作用不能排除不穩定這一因素。導致環路濾波器不穩定的產檢原因有忽略考慮VCO輸入電容;使用過度限制環路帶寬的集成濾波器;或者使用與PLL初始設計不同的PLL設置(電荷泵增益、VCO頻率或鑒相器頻率)。

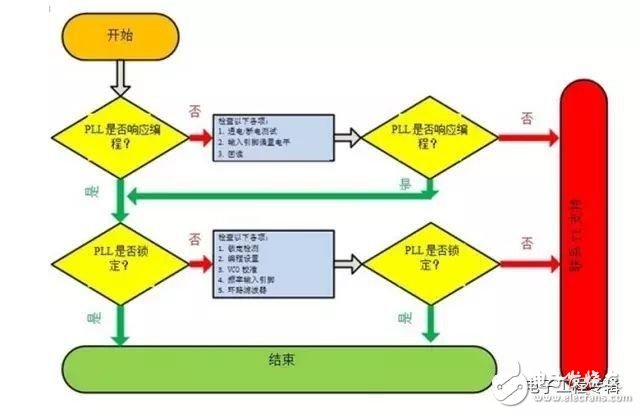

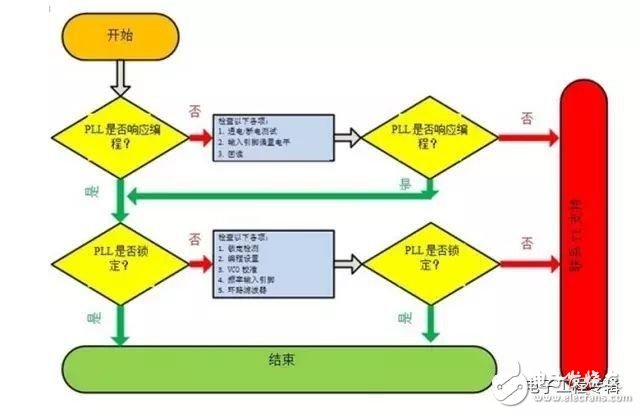

遵循系統的方法,不作出草率的假設能夠使PLL鎖定調試程序變得簡單許多。下圖為指導此程序的流程圖。

圖:PLL調試流程圖

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

原文標題:鎖相環無法鎖定,應該這樣處理…

文章出處:【微信號:eet-china,微信公眾號:電子工程專輯】歡迎添加關注!文章轉載請注明出處。

相關推薦

鎖相環(PLL)是一種反饋控制系統,用于鎖定輸入信號的相位和頻率。它在現代電子系統中扮演著至關重要的角色,從無線通信到數字信號處理,PLL的應用無處不在。然而,由于其復雜性,PLL也可能出現各種故障

![的頭像]() 發表于

發表于 11-06 10:52

?561次閱讀

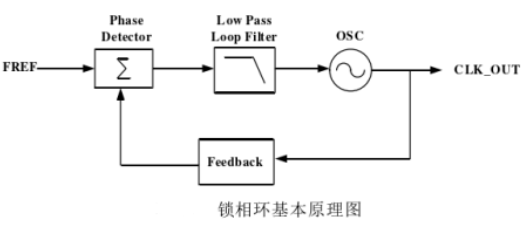

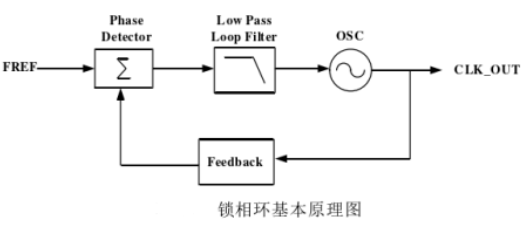

、鎖相環(PLL)的基本原理 鎖相環是一種電子電路,能夠鎖定到輸入信號的相位,并產生一個與輸入信號頻率和相位一致的輸出信號。PLL由三個主要部分組成:相位檢測器(PD)、環路濾波器(LF)和壓控振蕩器(VCO)。 相位檢測器(P

![的頭像]() 發表于

發表于 11-06 10:46

?334次閱讀

鎖相環(Phase-Locked Loop, PLL)和鎖相放大器(Lock-in Amplifier)是兩種在電子學和信號處理領域廣泛應用的技術,它們各自具有獨特的工作原理、組成結構以及應用場景。以下將從定義、組成、工作原理、性能特點及應用領域等方面詳細闡述

![的頭像]() 發表于

發表于 07-30 15:51

?1222次閱讀

鎖相環(Phase Locked Loop, PLL)相位噪聲是評估鎖相環性能的重要指標之一,它描述了輸出信號相位的不穩定性。相位噪聲的存在會直接影響系統的性能,如降低信號的信噪比、增加誤碼率、影響雷達系統的目標分辨能力等。以下將詳細分析

![的頭像]() 發表于

發表于 07-30 15:31

?1346次閱讀

我在配置AD9694的過程中發現AD9694的采樣率對應的線速率只有在6.75Gbps-13.5Gbps之間時,204b接口的鎖相環才能鎖定,現在想配置200M采樣率,但是204B接口的鎖相環無法

發表于 07-03 06:18

我在配置AD9694的過程中遇到了AD9694輸入時鐘低于337.5MHz時,內部的serdes鎖相環無法鎖定的問題;但輸入時鐘高于337.5MHz時,如400M、600M就能鎖定;0x56e寄存器

發表于 06-21 14:27

基本鎖相環通常由鎖相檢測器(Phase Detector)、低通濾波器(Loop Filter)和令牌圈振蕩器(VCO)組成。它是最簡單的鎖相環形式,用于頻率和相位同步。

![的頭像]() 發表于

發表于 01-31 16:00

?1786次閱讀

鎖相環是保證相位一致,還是相位差一致?鎖相環的輸入輸出相位一致嗎? 鎖相環(PLL)是一種回路控制系統,用于保持輸出信號的相位與參考信號的相位之間的恒定關系。簡單來說,鎖相環的目的是保

![的頭像]() 發表于

發表于 01-31 15:45

?1151次閱讀

鎖相環鎖定后一定不存在頻差嗎? 鎖相環是一種常用的控制系統,用于將輸入信號與參考信號之間的相位誤差維持在一個可接受的范圍內。它通過調節輸出信號的相位和頻率來實現這個目標。然而,

![的頭像]() 發表于

發表于 01-31 15:25

?833次閱讀

鎖相環到底鎖相還是鎖頻? 鎖相環(PLL)是一種常用的控制系統,主要用于同步時鐘。它通過將被控信號的相位與穩定的參考信號進行比較,并產生相應的控制信號,使被控信號的相位保持與參考信號同

![的頭像]() 發表于

發表于 01-31 15:25

?1965次閱讀

鎖相環路(PLL)。鎖相環是一種控制系統,它可以將一個信號鎖定到參考頻率上,保持相位一致。它由一個相位檢測器、一個低通濾波器、一個壓控振蕩器和一個分頻器組成。 鎖相環首先將輸入信號與參

![的頭像]() 發表于

發表于 01-31 15:24

?1139次閱讀

鎖頻環為什么鎖定后又發生失鎖現象? 鎖頻環是一種非常重要的電子電路,常見于通信設備、數字信號處理、時鐘恢復和頻率合成等領域。鎖頻環的作用是將輸入信號與輸出信號的頻率

![的頭像]() 發表于

發表于 01-31 11:31

?1189次閱讀

,也稱為追蹤帶。它的主要功能是鎖定輸入信號與VCO(電壓控制振蕩器)輸出信號的相位,使輸出信號與輸入信號保持相位一致。 - 鎖相環捕獲帶:捕獲帶是鎖相環的另一種工作模式,也稱為拉住帶。它的主要功能是在輸入信號發生較大偏差時,將輸

![的頭像]() 發表于

發表于 01-31 11:31

?1405次閱讀

環路的跟蹤狀態是指鎖相環鎖定后的狀態,即環路中的壓控振蕩器(VCO)的輸出信號的相位能夠自動跟蹤輸入信號的相位,從而保持恒定的穩態相位差。

![的頭像]() 發表于

發表于 01-30 14:18

?1123次閱讀

本人在使用ADF4372芯片時,運用RF16輸出口,鎖相環正常鎖定,但是輸出幅度只有-28dbm,這是為什么,請求解答謝謝。沒有在VDDX1加7.4nH電感。

發表于 01-03 07:39

用驗證通行與建立鎖定的程序來進行鎖相環鎖定

用驗證通行與建立鎖定的程序來進行鎖相環鎖定

評論