周立功教授新書《面向AMetal框架與接口的編程(上)》,對AMetal框架進行了詳細介紹,通過閱讀這本書,你可以學到高度復用的軟件設計原則和面向接口編程的開發思想,聚焦自己的“核心域”,改變自己的編程思維,實現企業和個人的共同進步。經周立功教授授權,即日起,致遠電子公眾號將對該書內容進行連載,愿共勉之。

第二章為ADC 信號調理電路設計,本文為 2.1 應用背景和2.2 電路設計。

本章導讀:

對于開發者來說,最難的是模擬電路的設計。不僅需要投入大量的儀器設備,而且還需要理論水平很高且實踐經驗很豐富的指導老師,才有可能設計出符合要求的模擬電路。通過分析用戶設計的模擬電路,發現大多數開發者對模擬電路的設計細節知之甚少。

雖然很多半導體公司提供了琳瑯滿目的設計參考資料,但介紹到某些關鍵之處時還是讓人感到語焉不詳,這就是大部分開發者對模擬電路仍然心有余悸的原因。就拿MCU 供應商來說,其提供的資料更多的是數字電路的設計和基本的軟件資料。幾乎所有的MCU 供應商都不提供具有一定價值的應用電路設計參考,各個廠商提供的資料可以說千篇一律,你想要的沒有。其實這些知識對于開發者來說都屬于非核心域知識,卻要花費很多時間投入其中。

基于此,我們對MCU 內部提供的各種各樣的ADC 所需的外圍電路進行了標準化的設計,期望推動整個行業的設計水平。因為無論任何需求都存在共性和差異性,所以只要掌握正確設計方法,就能夠達到舉一反三的效果。

2.1 應用背景

>>> 2.1.1 標稱精度

LPC824 內部有一個12 位SAR 型ADC,多達12 個輸入通道以及多個內部和外部觸發器輸入,其采樣率高達1.2MS/s。與獨立12 位ADC 芯片相比,手冊標注的關鍵參數非常接近,理論上可以實現比較好的采集精度,詳見表2.1。在實際的應用中,用戶測試結果和標稱值相差很遠,表現出內部ADC 精度差,這是ADC 外部電路設計不合理所造成的。

表2.1 LPC82x 內部ADC 關鍵參數

>>> 2.1.2 外圍電路

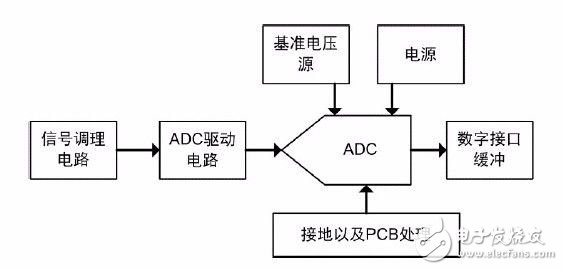

如圖2.1 所示使用LPC82x 內部ADC 的采樣系統,所需外圍支持電路包含基準源、供電電源、驅動電路、信號調理電路等幾部分,從原理上看這幾部分都影響ADC 的性能指標。

圖2.1 內部ADC 所需的外圍支持電路

>>> 2.1.3 干擾源

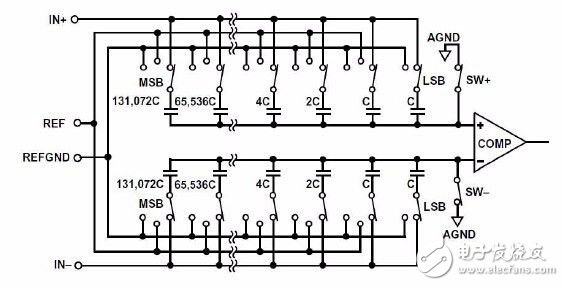

絕大多數MCU 內部集成的ADC 幾乎都是逐次逼近(SAR)型,因為它使用開關電容結構,半導體工藝容易實現。由于SAR 型ADC 有多個有效輸入端口,因此也容易受到干擾。典型SAR 型ADC 內部結構詳見圖2.2,分析它的工作原理有助于理解干擾的引入路徑。

圖2.2 SAR 型ADC 內部結構

它通過兩個階段確定ADC輸出碼,由于采集階段開關SW+和SW-最初是關閉的,所有開關均連接到IN+和IN-模擬輸入,因此各電容用作采樣電容,實現采集輸入端的模擬信號。在轉換階段SW+和SW-是打開的,模擬輸入與內各部電容斷開,電容作用到比較器輸入時,將導致比較器不穩定。AR 算法從MSB 開始,切換REF 與REFGND 之間的權電容陣列的各元件,使比較器重新回到平衡狀態,由此將產生代表模擬輸入的輸出數字代碼。

轉換過程中代表被測輸入信號的總電量,在權電容陣列中的各電容兩端不斷重復分布,每bit 的轉換數據都根據與基準源的比較結果產生,從而決定輸出代碼是0 還是1,基準源上的任何噪聲都會對輸出代碼產生直接影響。如果比較過程中電源端、地回路存在干擾,使得內部比較器的結果變動,同樣也會間接導致ADC 輸出數據位不穩定,詳見圖2.3。

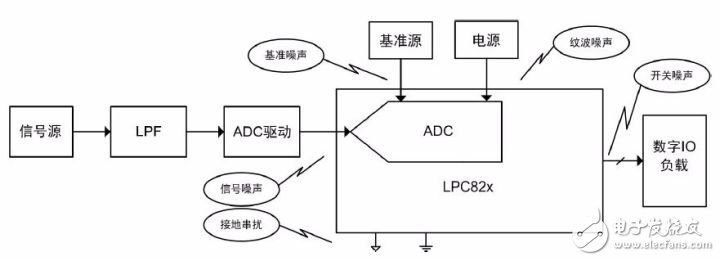

圖2.3 SAR 型ADC 有多個有效輸入端口

SAR 型ADC 這種多次反復比較結構,基準源、電源、地、或數字接口都有可能串入干擾信號,等效于存在多個有效輸入端口,而不僅僅只有一個信號輸入端。防止外部干擾信號,從ADC 信號輸入端以外的引腳耦合進來,才能得到到穩定的數據輸出。

2.2 電路設計

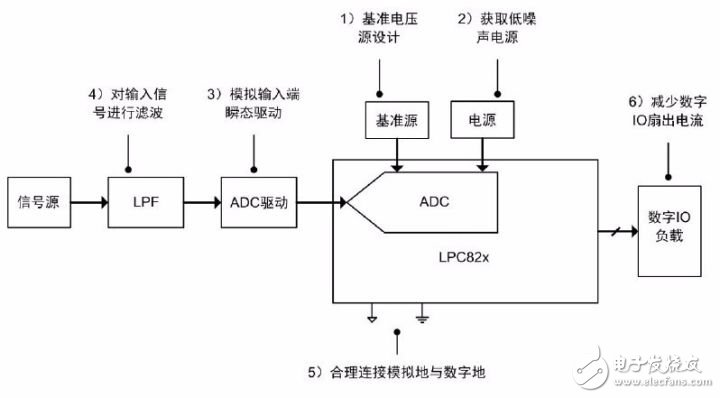

提高內部SAR 型ADC 精度的要點在于逐一排除各有效輸入端口上的干擾,詳見圖2.4。

圖2.4 消除ADC 外圍支持電路干擾的方法

根據對精度的影響程度,電壓基準源電路的設計占80%的工作量,低噪聲模擬電源占5%,輸入端瞬態驅動占5%,其它抗干擾措施占10%。

>>> 2.2.1 基準源

基準電壓直接影響ADC 數字輸出,要求低噪聲、低輸出阻抗、溫度穩定性良好,標準化電路詳見圖2.5。

圖2.5 低噪聲與低輸出阻抗基準電壓源電路

其中,C2、C1 是內部ADC 參考源管腳的儲能電容,R2、R3 用于設定參考源芯片NCP431的輸出電壓,R1 用于設定NCP431 的靜態工作電流,磁珠FB1 與R1 串聯,與C2 形成低通濾波器,濾除基準源供電3.3V 上可能存在的高頻干擾。

1. 低噪聲和低輸出阻抗

基準電壓源芯片使用低成本NCP431,輸出噪聲10uVpp,輸出阻抗0.2Ω。噪聲值用于12 位精度已經足夠低,但動態輸出阻抗0.2Ω 偏大。利用圖2.5 中儲能或去耦電容C2、C1的低高頻阻抗,提供ADC 轉換時基準源管腳上的瞬間高頻電流,能非常好地解決基準源高頻輸出阻抗問題。

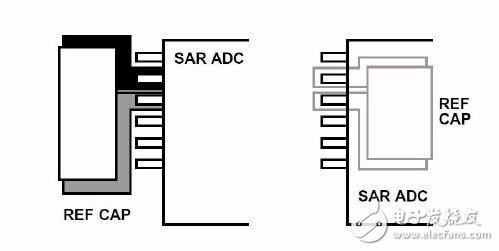

需要注意VREF 管腳上的10uF電容C2 不是旁路電容,而是SAR型ADC 的一部分,這個大電容不適合放在硅片上。在位判斷期間,由于各輸出位會在數十納秒或更快的時間內建立,因此該儲能電容是用來補充開關電容陣列的,從而與內部電容陣列上已有電荷一起平衡比較器。此大容值儲能電容需要滿足ADC 位判斷建立時間要求。為了降低它的高頻ESR,C2 優先選用X5R 材質貼片陶瓷電容,確保靠近基準源管腳VREFP 放置,并且在接近VREFN 模擬地管腳處接地,詳見圖2.6。

圖2.6 VREF 管腳儲能電容與芯片在/不在同一面的放置方法

2. 靜態工作電流

NCP431 是并聯型基準,原理類似穩壓二極管,只能吸收電流,詳見圖2.7。在提供負載電流時,維持基準源兩端電壓不變,使流過限流電阻R1 的總電流不變,調節基準源自身的靜態電流減小,使得負載上的電流增加。需計算R1 取值,保證在最大負載電流情況下,有最夠的剩余靜態電流。

圖2.7 并聯型的靜態工作電流

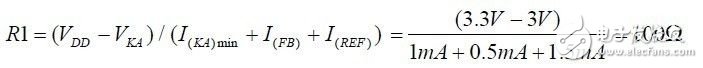

NCP431 手冊中的最小靜態電流I(KA)min 為1mA,NCP431 輸出電壓調節電阻R2、R3 所吸收電流I(FB)為0.5mA,LPC82x 的REF 管腳所吸收平均電流I(REF),約為100uA,留出裕量取1.5mA。總的靜態電流取3mA,算得決定靜態工作電流R1 的阻值:

3. 輸出電壓選擇

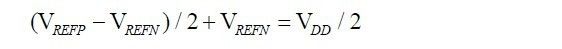

根據LPC82x 手冊,為了獲得最佳性能,VREFP 和VREFN 應當選擇與VDD 和VSS 相同的電壓電平。若VREFP 和VREFN 選擇不同于VDD 和VSS 的值,則應當確保電壓中間值是相同的:

實際測試發現基準電壓設置到3.0V 精度最理想,若再升高至接近LPC82x 的電源電壓3.3V,因為接近電源軌,ADC 的INL 實測值開始下降,因此標準電路中使用R2、R3 將NCP431的輸出電壓調整到此值,計算如下:

4. 溫漂與直流精度

溫漂和初始直流精度是基準源芯片的固有參數,溫漂越低初始精度越高,成本越高,溫漂25ppm 以下的基準幾乎都已經超過LPC82x 芯片自身成本,詳見表2.2。

表2.2 基準電壓源參數與成本

綜合考慮NCP431 是相對合適的選擇,它是ONSemi 對TL431 的改進版本,最大溫漂由原92 ppm/℃改進為50 ppm/℃,初始準確度優于0.5%。以25℃為參考溫度,在-40℃~+85℃范圍內,該溫漂值引入的誤差約為0.3%,基本符合12 位ADC 采集精度的應用。

需要注意標準化電路中R2、R3 影響NCP431 的溫漂,應該選擇低溫漂系數25ppm以下電阻。如果考慮節省成本或者沒有可選電阻,為了不影響基準溫漂,使用如圖2.8 所示的2.5V 輸出電路替代。

圖2.8 不使用外部電阻的NCP431 基準源電路

基準電壓由3V 下降至2.5V 之后,對LPC82x 內部ADC 的INL 會有輕微影響。

>>> 2.2.2 低噪聲模擬電源

為避免從電源端口串入干擾,需要低噪聲的供電電源。利用線性穩壓器的紋波抑制比,可以從通常的數字環境開關電源獲得此低噪聲電源,詳見圖2.9。

圖2.9 低噪聲模擬電源電路

使用FB2、R4、C5 所組成的無源濾波網絡,可以有效改善1117 在高頻段紋波抑制比下降的問題,實現從低頻至高頻的紋波噪聲抑制。其中R3 與C5 形成截止頻率1.59KHz 的低通濾波器,使得3.3V 電源上常見的100kHz 以上開關電源紋波干擾衰減10dB 以上。磁珠FB2 在高頻時呈現高阻抗,結合C5 在高頻時形成更高衰減倍數的低通濾波器,有效濾除3.3V電源上尖峰毛刺噪聲。

線性穩壓器使用SPX1117,紋波抑制比曲線詳見圖2.10,在低頻至10kHz 頻段有接近-60dB 的良好紋波抑制比,100kHz 之后快速下降。

圖2.10 SPX1117 的紋波抑制比

線性穩壓器U2 應該靠近LPC82x 放置,其他數字電路不共用MCU 的3.3V 電源,如果考慮成本需要共用,數字部分電源單獨用LC 濾波電路隔離。

>>> 2.2.3 瞬態驅動

SAR 型ADC 輸入端在采樣期間具有瞬間充電過程,如果不處理信號源阻抗與內部采樣電容的建立時間問題,不管是微處理器中內置的還是外置的ADC,都得不到最好的輸出精度。標準化電路中使用運放加RC 組合電路詳見圖2.11。

圖2.11 內部ADC 輸入端瞬態驅動電路

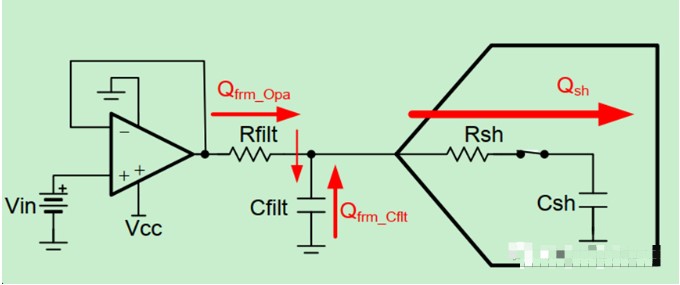

通過典型SAR 型ADC 輸入端等效電路,有助于理解瞬態驅動電路。如圖2.12 所示輸入端等效為一個開關S1 連接一個接到地的電容CSH,在電壓采樣之前,采樣電容CSH 通過開關S2 連到電源、電壓參考或地進行預充電,預充電電壓值由ADC 內部電路決定。電壓采樣開始時,S2 打開S1 閉合。

圖2.12 SAR 型ADC 輸入端等效電路

當S1 閉合時,驅動電路從CSH 注入或吸出電荷,而ADC 需要一定的時間來采樣信號。在這個采樣時間里,ADC 需要從驅動電路汲取足夠的電荷量給CSH,使得系統達到1/2-LSB 的精度范圍之內。

如果信號源阻抗RO 過大,RO、Rs1RS1、CSH 組成的RC 網絡時間常數過大,導致采樣時間內CSH 上的電壓建立時間不足,采集到的電壓值將下降。比較好的解決方法詳見圖2.12,添加運放緩沖降低信號源內阻,無論信號源阻抗RO 高或者低都不會影響精度。

直接使用運放驅動ADC 輸入端時,S1 閉合瞬間的充電電流會干擾運放的輸出電壓,從而導致ADC 輸出結果不準確。為了使設計的電路精度到達更高,應該在運放與ADC 之間添加一個電阻Rin 電容Cin,Cin 是作為一個電荷存儲器,在采樣瞬間為ADC 的輸入端提供足夠的電荷,而Rin 用于避免運放驅動容性負載,使得運放工作更加穩定。

>>> 2.2.4 輸入信號濾波

輸入信號自身可能包含有不期望的干擾信號,在輸入電路上添加濾波器抑制干擾,是必要的硬件抗干擾措施。如果通過采樣數據的后期數據處理濾除干擾,根據采樣定理,必須在硬件上設置抗混疊濾波器,限制輸入信號帶寬至1/2 采樣頻率以下。

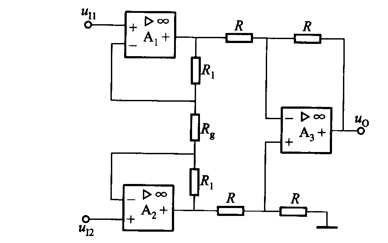

1. 有源濾波器

標準化電路中復用ADC 驅動運放,實現三階有源低通濾波器,詳見圖2.13。

圖2.13 三階低通有源濾波器

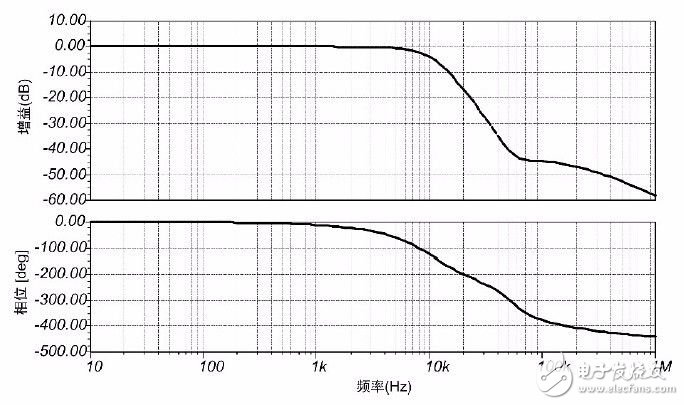

濾波器的低通截止頻率設置為9kHz,類型為三階貝塞爾,具有良好的衰減特性。并且使用圖2.13 中的3 階電路形式,避免了常規單運放實現二階Sallen-Key 型濾波器拓撲,由于運放帶寬不夠,出現的高頻饋通問題。即使用帶寬不高的運放LMV358A,也不會出現高頻信號穿透濾波器,詳見圖2.14。

圖2.14 三階濾波器的頻率響應

2. 電阻噪聲與運放的電源抑制比

一般來說,有源濾波器自身可能產生噪聲,通常稱之為器件噪聲,其分別為電阻的熱噪聲、運放的電壓輸出噪聲。電阻值越大所引入的電阻噪聲越大,1kΩ 電阻的Johnson 噪聲大約是4nV/(Hz)1/2,這個數值以電阻的平方根規律變化。若考慮到電阻噪聲,推薦的阻值是1~10kΩ。電阻噪聲最后可以歸結到的濾波電路中被濾除,但是它和運放輸出噪聲是電路中噪聲產生的源頭,在設計時要予以考慮,適當的采用低阻值電阻和低噪聲運放。

此外需考慮運放的電源抑制比。電源上的噪聲會隨著每個有源器件的電源引腳傳導到信號通路中,作為ADC 驅動放大器的運放,其自身的電源抑制比若不能抑制這些噪聲的話,噪聲就會疊加到運放的輸出中。特別是電路中采用了開關電源供電時,電源上會有高頻尖峰電壓噪聲,而運放的電源抑制比在高頻時通常下降得厲害,對它們沒有抑制作用。以標準電路圖中所用的運放LMV358A 為例,其電源抑制比詳見圖2.15。

圖2.15 LMV358A 電源抑制比

解決這個問題簡單方法是采用RC 低通濾波器對運放電源進行濾波,濾除其電源抑制比較低的高頻成分,如圖2.13 所示的R4、C7。若將運放的電源端視為高阻抗(其工作電流小),算得RC 濾波器的截止頻率約為:1.6kHz,可以對高頻干擾信號起到有效衰減。

3. 運放選型

使用LPC82x 內部ADC 的采集應用,通常對器件成本的要求非常嚴酷,標準化電路設計考慮使用最低成本運放——LM358 系列。

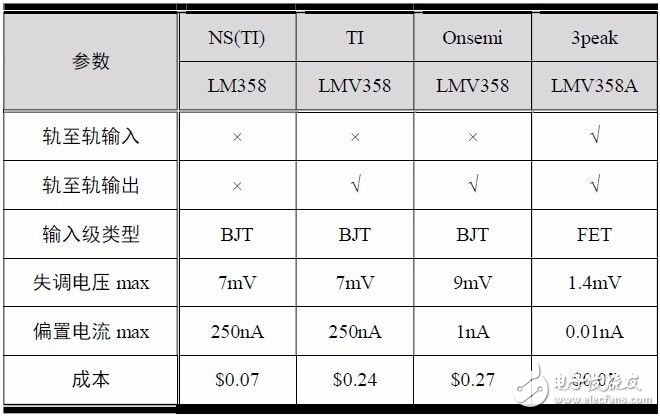

經典運放器件通常存在兩個問題,單電源條件下輸入和輸出信號范圍不能達到電源電壓(輸入輸出不能軌至軌),信號測量范圍窄;輸入失調電壓與偏置電流比較大,直流精度影響大,因此不能使用。但現在已經有不少廠家生產LM358 兼容或改進產品,詳見表2.3。

表2.3 低成本運放參數選型

表中的數據表明,只有3peak 公司的改進型器件LMV358A,同時支持軌至軌輸入與輸出,FET 輸入級并且失調電壓比較低,成本與原LM358 一致,能夠符合應用需求,因此標準化電路最終選用LMV358A。

>>> 2.2.5 模擬地與數字地

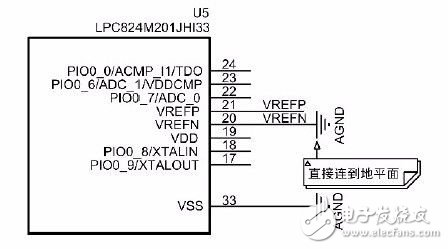

具有內部ADC 的MCU 一般有獨立AGND管腳,以及普通GND 管腳。如何把AGND 連接到GND 往往模糊不清,避免二者相互干擾的最優設計方法是,AGND 和GND 管腳都就近接到地平面,詳見圖2.16。

圖2.16 AGND 與GND 的連接處理

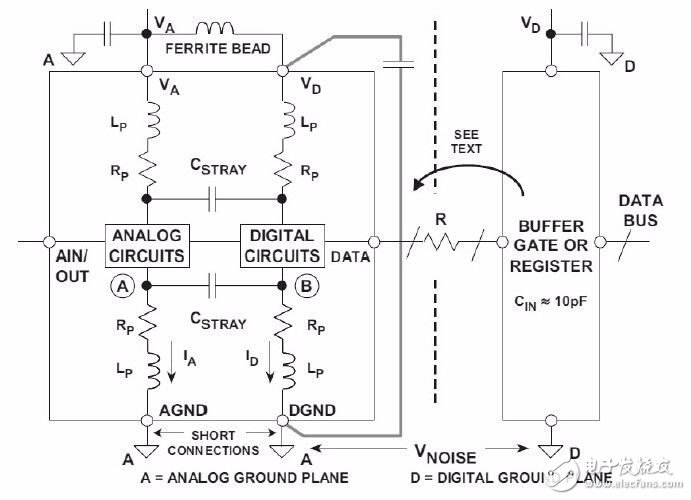

了解混合信號IC 內部的接地管腳結構,有助于理解IC 設置獨立模擬地、數字地管腳的意圖,詳見圖2.17。使接地管腳保持獨立,可以避免將數字信號耦合至模擬電路內。在IC 內部,將硅片焊盤連接到封裝引腳的邦定線難免產生線焊電感LPLP 和電阻RPRP,IC 設計人員對此是無能為力的。如果共用地管腳,快速變化的數字電流在B 點產生電壓,對于模擬電路無法接受,IC 設計人員意圖分開接地管腳,排除此影響。

圖2.17 IC 內部模擬與數字地的連接情況

但是,分開之后B 點電壓還會通過雜散電容CSTRAYCSTRAY 耦合至模擬電路的A 點。IC封裝每個引腳間約有0.2 pF 的寄生電容,是無法避免的。為了防止進一步耦合,AGND 和DGND 應通過最短的引線在外部連在一起,并接到模擬接地層。DGND 連接內的任何額外阻抗將在B 點產生更多數字噪聲;繼而使更多數字噪聲通過雜散電容耦合至模擬電路。

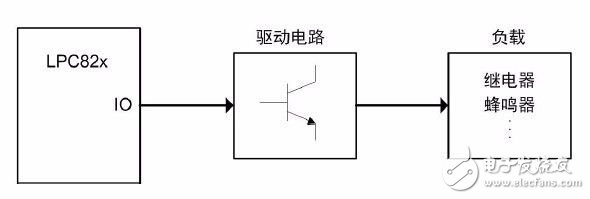

>>> 2.2.6 I/O 扇出電流

由于LPC82x 只有一個電源管腳,即MCU 數字電源與內部ADC 模擬電源共用。雖然這樣設計可以在小封裝中提供盡可能多的I/O 口,但是對模擬部分會帶來干擾問題:MCU工作時在電源上產生數字開關電流,通過共用管腳產生噪聲電壓,干擾內部ADC。下面的優化建議可以很大程度上避免干擾:

-

避免I/O 口直接驅動大電流,使用三極管或邏輯芯片間接驅動,詳見圖2.18;

-

若條件允許,則切換到低功耗模式下執行ADC 采集。

圖2.18 使用驅動電路減小I/O 扇出

-

電路設計

+關注

關注

6673文章

2451瀏覽量

204167 -

adc

+關注

關注

98文章

6495瀏覽量

544468

發布評論請先 登錄

相關推薦

信號調理產品電路設計與寄存器配置

振動信號調理硬件電路設計

測控、信號調理電路、小信號源功率電路設計。

混合信號電路設計技術研究

心電信號調理電路設計

ADC 信號調理電路設計——應用背景和電路設計

ADC 信號調理電路設計——應用背景和電路設計

評論