在現代電子技術飛速發展的今天,芯片作為電子設備的核心組件,其性能與穩定性直接關系到整個系統的運行狀況。然而,隨著芯片集成度的不斷提高,電源噪聲問題日益凸顯。本文將探討為何要重視電源噪聲問題。

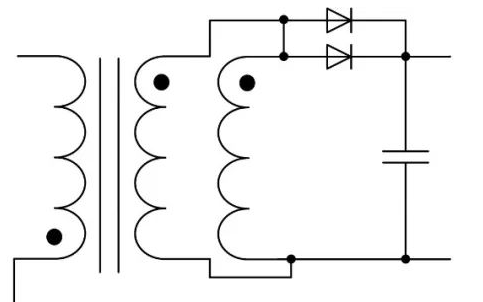

芯片內部構造復雜,晶體管數量龐大。這些晶體管通過精細的組合與布局,形成了門電路、組合邏輯、寄存器、計數器、延遲線、狀態機等多種邏輯功能。隨著技術的不斷進步,芯片的集成度越來越高,內部晶體管的數量也呈現出爆炸式增長。然而,芯片的外部引腳數量卻相對有限,無法為每一個晶體管提供單獨的供電引腳。這種結構特點導致芯片內部的所有晶體管必須共享一個公共的供電節點,從而使得電源噪聲在芯片內部的傳遞成為不可避免的現象。

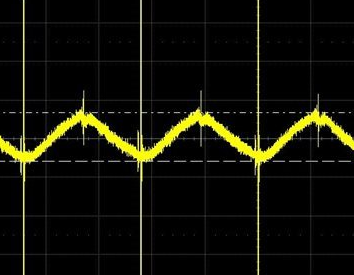

電源噪聲的產生與晶體管狀態的轉換密切相關。在芯片內部,各個晶體管的操作通常由內核時鐘或片內外設時鐘同步控制。然而,由于內部延時的差異,各個晶體管的狀態轉換不可能完全同步進行。當某些晶體管已經完成了狀態轉換時,另一些晶體管可能仍處于轉換過程中。這種不同步的狀態轉換會導致電源噪聲在芯片內部的傳播與積累,進而影響芯片的正常工作。

更為嚴重的是,電源噪聲還可能對芯片的邏輯功能產生直接影響。當電源噪聲傳遞到處于電平轉換不定態區域的門電路時,噪聲信號可能會被放大,并在門電路的輸出端產生矩形脈沖干擾。這種干擾不僅會導致電路的邏輯錯誤,還可能引發一系列連鎖反應,進一步破壞芯片的穩定性和可靠性。此外,電源噪聲還可能通過內部門電路的傳播觸發內部寄存器的狀態轉換,進一步加劇芯片的不穩定狀態。

除了對芯片本身的影響外,電源噪聲還會對其他部分產生負面影響。例如,電源噪聲會影響晶振、PLL、DLL等關鍵部件的抖動特性,降低AD轉換電路的轉換精度等。這些影響不僅會降低系統的整體性能,還可能引發一系列難以預料的問題和故障。

綜上所述,電源噪聲問題對于芯片及系統的性能和穩定性具有重要影響。因此,在電路設計之初就應遵循成熟的設計規則,采取有效措施抑制電源噪聲的產生和傳播。同時,還應加強電源系統的調試與測試工作,確保其在各種工作條件下都能保持穩定可靠的性能。只有這樣,才能為電子設備的正常運行提供有力保障。

-

芯片

+關注

關注

455文章

50732瀏覽量

423241 -

晶體管

+關注

關注

77文章

9684瀏覽量

138091 -

電源噪聲

+關注

關注

3文章

151瀏覽量

17474

發布評論請先 登錄

相關推薦

為什么需要重視電源噪聲問題

為什么需要重視電源噪聲問題

評論