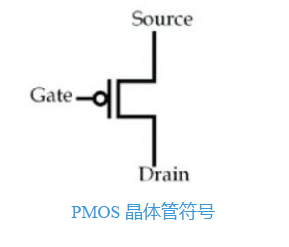

PMOS(P-type Metal-Oxide-Semiconductor)晶體管,即P型金屬氧化物半導(dǎo)體場效應(yīng)晶體管,是電子電路中常用的關(guān)鍵元件之一。其飽和狀態(tài)是PMOS晶體管操作中的一個(gè)重要模式,對理解其工作原理及在電路中的應(yīng)用具有重要意義。以下是對PMOS晶體管飽和狀態(tài)的詳細(xì)概述。

一、PMOS晶體管的基本結(jié)構(gòu)和工作原理

PMOS晶體管由源極(Source)、漏極(Drain)、柵極(Gate)和襯底(Substrate)四個(gè)主要部分組成。其工作原理基于場效應(yīng)原理,即通過改變柵極電壓來控制漏極和源極之間的電流。在PMOS中,襯底通常為P型半導(dǎo)體材料,而源極和漏極則為N型摻雜區(qū)域,形成PN結(jié)結(jié)構(gòu)。

二、PMOS晶體管的飽和狀態(tài)定義

飽和狀態(tài)是PMOS晶體管的一種工作狀態(tài),此時(shí)晶體管處于低電壓、大電流的工作模式。在飽和狀態(tài)下,PMOS晶體管的溝道已經(jīng)完全打開,漏極和源極之間的電流達(dá)到最大值,且該電流值基本不受柵極電壓進(jìn)一步增加的影響。這一狀態(tài)在數(shù)字邏輯電路和模擬電路中均具有重要意義,是實(shí)現(xiàn)信號(hào)放大和開關(guān)功能的關(guān)鍵。

三、PMOS晶體管進(jìn)入飽和狀態(tài)的條件

1. 柵極電壓與閾值電壓的關(guān)系

PMOS晶體管進(jìn)入飽和狀態(tài)的首要條件是柵極電壓(VGS)與源極電壓(VS)之間的差值必須高于晶體管的閾值電壓(Vth)。閾值電壓是PMOS晶體管的一個(gè)重要參數(shù),它決定了晶體管開始導(dǎo)電所需的柵極電壓值。當(dāng)VGS > Vth時(shí),PMOS晶體管的溝道開始形成并允許電流通過;當(dāng)VGS進(jìn)一步增加并滿足飽和條件時(shí),溝道完全打開,晶體管進(jìn)入飽和狀態(tài)。

2. 漏極電壓與柵極電壓的關(guān)系

除了柵極電壓與閾值電壓的關(guān)系外,漏極電壓(VDS)與柵極電壓之間的關(guān)系也對PMOS晶體管的飽和狀態(tài)產(chǎn)生影響。在飽和狀態(tài)下,VDS的值雖然會(huì)影響漏極電流的具體大小,但不再像可變電阻區(qū)那樣顯著影響溝道的導(dǎo)電性。此時(shí),漏極電流主要由柵極電壓和晶體管的物理參數(shù)決定。

3. 溫度效應(yīng)

溫度也是影響PMOS晶體管飽和狀態(tài)的一個(gè)重要因素。隨著溫度的升高,半導(dǎo)體材料的導(dǎo)電性會(huì)發(fā)生變化,進(jìn)而影響晶體管的閾值電壓和電流特性。在高溫條件下,PMOS晶體管的飽和電流可能會(huì)增加,而飽和電壓范圍也可能發(fā)生偏移。因此,在設(shè)計(jì)電路時(shí)需要考慮溫度對PMOS晶體管性能的影響。

四、PMOS晶體管飽和狀態(tài)的特點(diǎn)

1. 低電壓大電流

在飽和狀態(tài)下,PMOS晶體管能夠在較低的柵極電壓下實(shí)現(xiàn)較大的漏極電流輸出。這一特點(diǎn)使得PMOS晶體管在需要大電流驅(qū)動(dòng)的電路中具有廣泛的應(yīng)用價(jià)值。

2. 電流飽和性

在飽和區(qū)域內(nèi),漏極電流基本保持恒定不變或變化很小,即使柵極電壓繼續(xù)增加也不會(huì)引起漏極電流的顯著變化。這種電流飽和性使得PMOS晶體管在作為電流源或放大器時(shí)具有穩(wěn)定的性能表現(xiàn)。

3. 跨導(dǎo)最大

在飽和狀態(tài)下,PMOS晶體管的跨導(dǎo)(即柵極電壓對漏極電流的控制能力)達(dá)到最大值。這使得PMOS晶體管在作為放大元件時(shí)能夠?qū)崿F(xiàn)較高的增益和較好的線性度。

五、PMOS晶體管飽和狀態(tài)的應(yīng)用

1. 數(shù)字邏輯電路

在數(shù)字邏輯電路中,PMOS晶體管常作為開關(guān)元件使用。在飽和狀態(tài)下,PMOS晶體管能夠提供穩(wěn)定的低電阻通路,實(shí)現(xiàn)信號(hào)的快速傳輸和切換。這使得PMOS晶體管在構(gòu)建CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)邏輯門等數(shù)字電路元件時(shí)具有重要作用。

2. 模擬電路

在模擬電路中,PMOS晶體管可用于實(shí)現(xiàn)放大器、比較器和振蕩器等功能。在飽和狀態(tài)下,PMOS晶體管的電流飽和性和跨導(dǎo)最大性使得其能夠作為穩(wěn)定的電流源和放大元件使用。此外,PMOS晶體管還可與其他元件組合形成復(fù)雜的模擬電路系統(tǒng),實(shí)現(xiàn)信號(hào)的放大、濾波和調(diào)制等處理功能。

六、總結(jié)

PMOS晶體管的飽和狀態(tài)是其操作中的一個(gè)重要模式,具有低電壓大電流、電流飽和性和跨導(dǎo)最大等特點(diǎn)。該狀態(tài)在數(shù)字邏輯電路和模擬電路中均具有重要意義,是實(shí)現(xiàn)信號(hào)放大和開關(guān)功能的關(guān)鍵。在設(shè)計(jì)電路時(shí),需要充分考慮PMOS晶體管的飽和條件和應(yīng)用特點(diǎn),以確保電路的穩(wěn)定性和性能表現(xiàn)。同時(shí),隨著電子技術(shù)的不斷發(fā)展,對PMOS晶體管性能的要求也在不斷提高,需要不斷探索新的材料、工藝和電路結(jié)構(gòu)以滿足不同的應(yīng)用需求。

-

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28615瀏覽量

232650 -

晶體管

+關(guān)注

關(guān)注

77文章

9979瀏覽量

140670 -

PMOS

+關(guān)注

關(guān)注

4文章

266瀏覽量

30321

發(fā)布評論請先 登錄

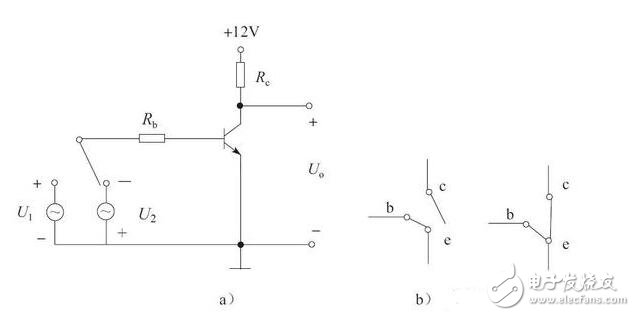

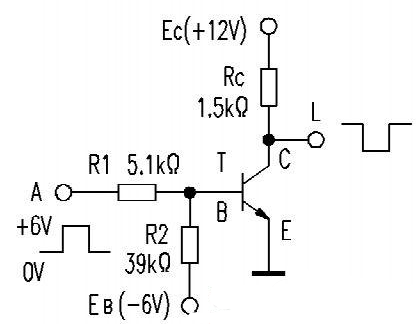

晶體管的飽和狀態(tài)和飽和壓降

三極管飽和狀態(tài)以及深入飽和狀態(tài)的理解

晶體管可以作為開關(guān)使用!

NPN型和PNP型晶體管的工作狀態(tài)解析

談晶體管的飽和狀態(tài)和飽和壓降

關(guān)于三極管處于臨界飽和狀態(tài)的分析

三極管的飽和及深度飽和狀態(tài)

晶體管構(gòu)成的開關(guān)電路圖

PMOS晶體管工作原理 pmos晶體管的各個(gè)工作區(qū)域

晶體管的三種工作狀態(tài)

晶體管的三種工作狀態(tài)介紹

評論