I2C(Inter-Intergrated Circuit)總線是微電子通信控制領域中常用的一種總線標準,具有接線少,控制方式簡單,通信速率高等優點。

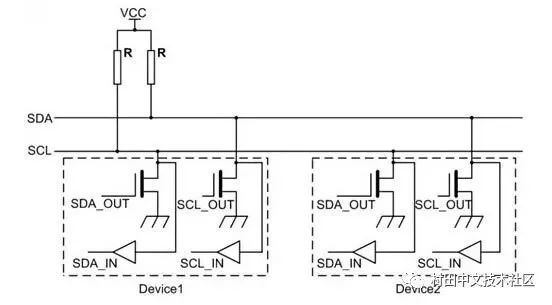

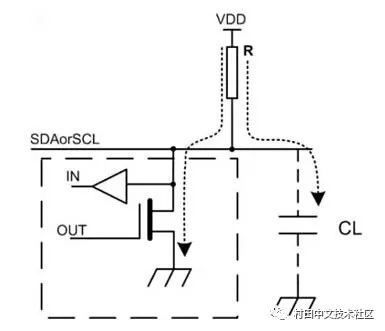

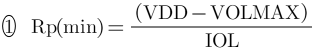

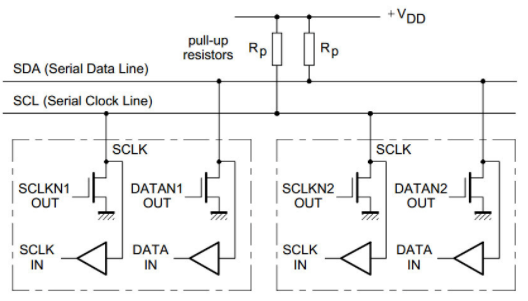

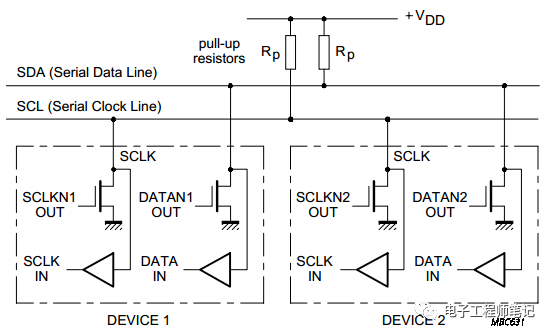

I2C總線的內部結構圖如圖1所示,I2C器件連接到總線輸出級必須是集電極開路或漏極開路形式才能實現線“與”的邏輯功能。輸出端未接上拉電阻的時候只能輸出低電平,所示保證I2C總線正常工作輸出端必須接上拉電阻。

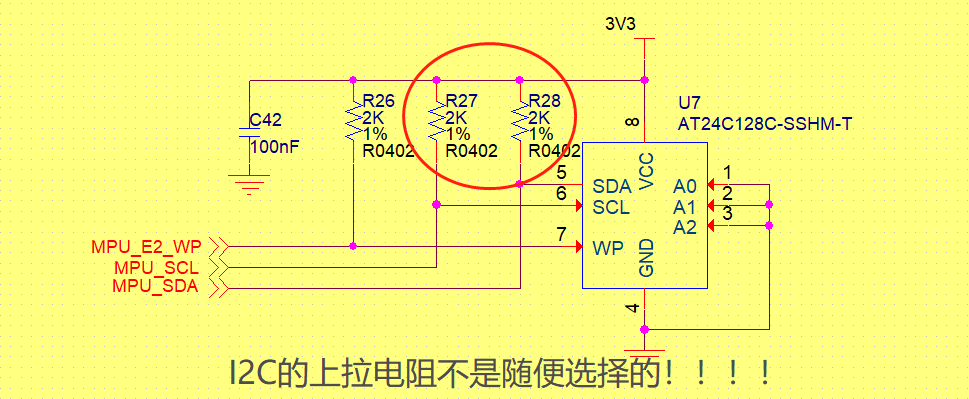

在I2C電路中常見的上拉電阻是1K,1.5K,2.2K,3.3K,4.7K,5.1K,10K等等,但選哪一個阻值更合適?

圖1 I2C總線內部結構

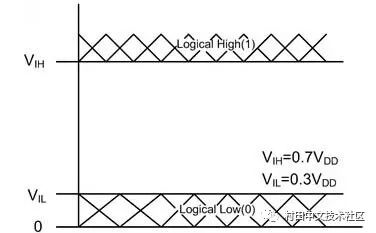

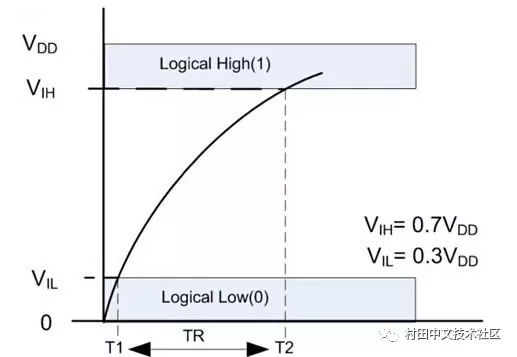

I2C總線上拉電阻阻值如何選?I2C規范將低于VIL或低于0.3VDD的電壓定義為邏輯低電平,同樣將高于VIH或高于0.7VDD的電壓定義為邏輯高電平,如圖2所示。

圖2 指定為邏輯高電平和邏輯低電平的電壓電平

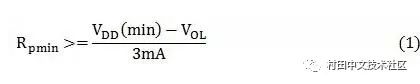

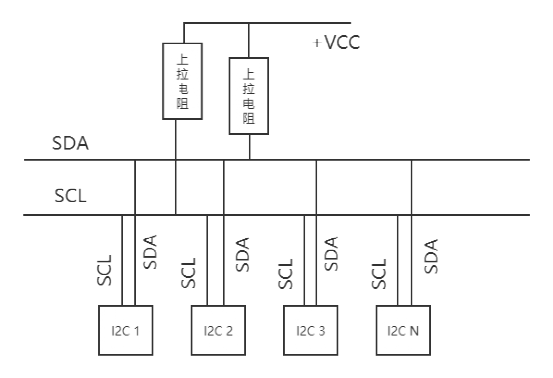

電源電壓限制了可允許總線拉低的最小上拉電阻值,過強的上拉會阻止器件充分拉低拉線的電平,導致無法確保邏輯低電平能被檢測到。在輸出級V_OLmax=0.4V 時指定I_OL為3mA,允許總線電壓拉低的最小上拉電阻公式:

V_DD與Rp的函數關系分別如圖3所示。

圖3 Rp的最小值是電壓的函數

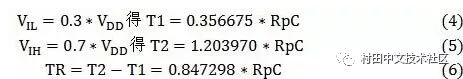

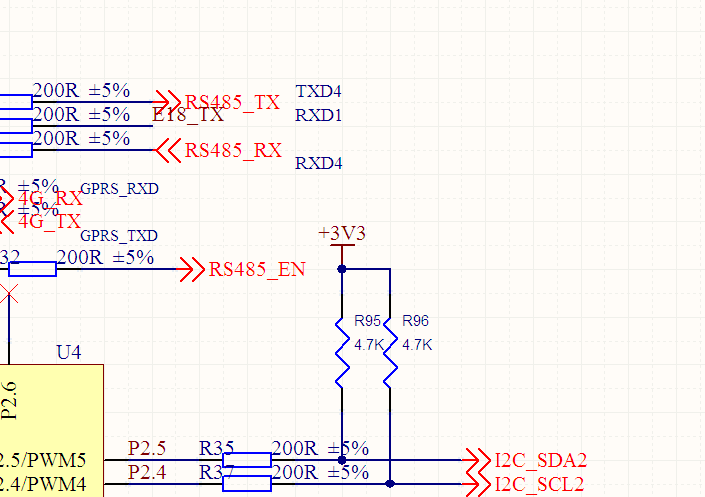

由于端口的輸出的高電平是通過上拉電阻實現,線上的電平從低變到高時,電源通過上拉電阻對線上負載電容CL充電,這需要一定的時間,即上升時間,上拉電阻的最大值由總線容限負載決定,總線負載圖如圖4所示。

圖4 總線負載結構圖

總線電容主要由引腳、連接、PCB走線和導線等因素引起,總線電容與上拉電阻R具有一個RC時間常數,隨著I2C通信速率的增加,該常數變得越發重要。通過電阻對電容進行充電的一般公式:

重新排列,

之后我們可計算電壓上升至VIL的時間T1、上升至VHL的時間T2以及精確計算兩個電平之間的時間TR,如圖5所示。由于VIL與VHL都是有V_DD產生,因此該公式與電源電壓無關,V_DD項已抵消。

圖5 總線電平上升時間

求解,

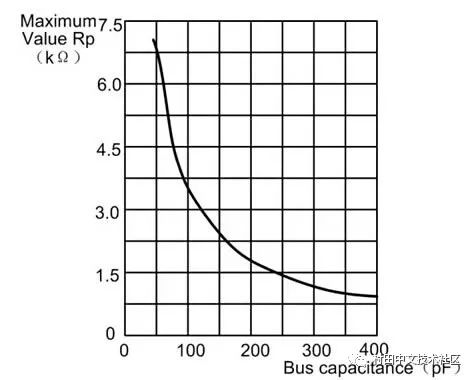

在I2C標準模式下,100Kbps總線的負載最大容限小于等于400pF;快速模式,400Kbps總線的負載最大容限小于等于200pF,快速模式下I2C總線上升時間更快,總線上拉電阻要比標準模式小,設計時以快速模式50Pf~200pF為參考,由上面(6)式得最大Rp值與總線電容的關系如圖6所示。

圖6 符合快速模式I2C總線TRmax要求的Rp最大值是總線電容的函數

由上面的計算可得出上拉電阻RP可以取的范圍是1.53K~7K @VDD = 5V,一般取5.1K ,綜合到3.3V VDD低功耗設計中,通常選用4.7K犧牲速度換取電池使用時間,此阻值也是常規阻值。

關于I2C的上拉電阻,最好的方式是看官方給出的參考設計,如果走線長了或總線上有多從機,就相應把電阻改小一些,如若參考設計沒有就在計算范圍內選用一個常規阻值。實際的時候我們沒有去測量總線電容的問題,只能在選件、走線的時候給予些許關注。

原文標題:I2C總線上拉電阻阻值如何選擇?

文章出處:【微信號:murata-eetrend,微信公眾號:murata-eetrend】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

I2C總線上拉電阻的計算實例

i2c上拉電阻大小_i2c上拉電阻的作用

I2C總線一定要接上拉電阻?上拉電阻阻值怎么確定?

在I2C總線上需要接上拉電阻?您對I2C上拉電阻足夠了解嗎

I2C的開漏輸出和上拉電阻

i2c總線電路的上拉電阻選擇技巧

i2c總線電路的上拉電阻選擇技巧

評論