2.湖北省電網智能控制與裝備工程技術研究中心,湖北 武漢430068)

摘 要: PC104總線是專為嵌入式控制系統定義的一種工業控制線,其應用廣泛,但是內部結構復雜,出現故障不易檢測。設計了一種基于FPGA的PC104總線故障自動監控平臺,對PC104總線信號進行實時監控和故障檢測。該平臺利用FPGA程序采集和處理總線信號,并傳至上位機處理顯示。系統中利用FPGA程序實現其功能模塊,包括捕獲POST上電自檢指令和BIOS自檢端口代碼、監測總線電壓水平、監控時鐘和復位等關鍵信號的質量、控制PC104的自動復位和BIOS設置模式等功能。給出上位機監控結果和FPGA實時檢測得到的時序圖,反映了該FPGA程序在本系統中滿足PC104總線檢測的技術要求。

關鍵詞: 總線監測;POST上電自檢;自檢端口監測;時鐘測量

中圖分類號: TN407;TP206

文獻標識碼: A

DOI:10.16157/j.issn.0258-7998.170644

中文引用格式: 周治虎,張凡,武明虎,等. PC104故障監控平臺FPGA程序設計[J].電子技術應用,2017,43(9):57-60.

英文引用格式: Zhou Zhihu,Zhang Fan,Wu Minghu,et al. FPGA program design of PC104 fault monitoring platform[J].Application of Electronic Technique,2017,43(9):57-60.

0 引言

PC104作為一種專用嵌入式控制主板[1],具有功耗低、效率高、體積小、可擴展等優點,在航空航天[2]、軍用武器裝備[3]、工業控制[4]等領域應用廣泛。PC104主板的結構復雜緊湊,一旦發生故障,僅靠常規的監控手段很難判斷具體的故障原因。PC104總線需要監測的信號高達70多個,總線運行頻率也高達14 MHz左右,無法利用單片機實現監測功能[5-6]。因此,本項目采用了基于FPGA的設計方案,利用FPGA的多I/O端口特性和高速并行處理能力[7]對PC104總線進行實時監測。

1 PC104監控系統設計方案

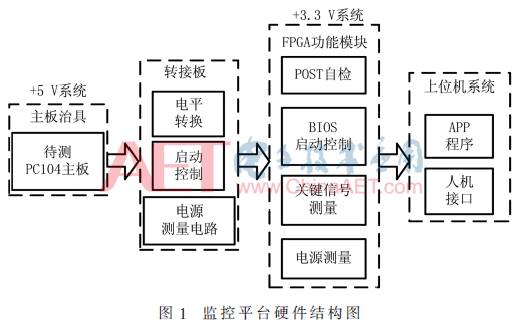

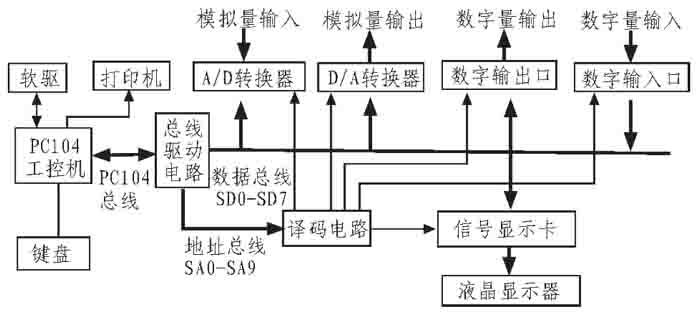

基于FPGA的PC104故障監控平臺(以下簡稱監控平臺)主要由待測PC104主板、電平信號轉換模塊、FPGA功能模塊(DE0開發板)[9]、上位機系統4個部分組成。監控平臺硬件結構如圖1。

監控平臺中的上位機系統板使用常用Windows XP系統,并自動運行監控APP程序。通過串口和FPGA功能模塊通信,利用約定好的通信協議讀取FPGA功能模塊返回的信息,將返回的這些信息處理成可供參考的數據,最后在上位機APP程序的界面中顯示。

PC104主板功能強大,擴展功能端口很多。監控平臺為判斷其具體的故障信息,需要對其總線信號進行實時監測。為了保證監控平臺方便高效的運行,在待測下方引入主板治具方便主板的插拔,這不僅提高了監控效率和準確性,同時可以保護PC104主板總線接口不被損壞。

由于PC104主板工作在+5 V供電環境下,而采用的FPGA的工作電壓是+3.3 V,監控平臺加入了基于74AL-VC164245的電平信號轉換模塊。74ALVC164245是TI公司生產制造的一種+5 V和+3.3 V之間雙向轉換的電平轉換芯片,可以很好地實現FPGA和PC104主板之間的電平匹配。轉接板上還包括PC104主板電源測試模塊,并將PC104主板上的鍵盤接口、鼠標接口和兩個串口接口做了擴展。不僅實現了不同電平之間信號的實時傳輸,同時增加了監控平臺的空間利用率。

2 FPGA功能模塊設計

FPGA功能模塊是PC104主板故障檢測平臺的核心,也是本文介紹的重點。FPGA擁有可編程輸入輸出單元(IOB)、可配置邏輯塊(CLB)、數字時鐘管理模塊(DCM)、嵌入式塊RAM(BRAM)、豐富的布線資源等功能,能很好地滿足檢測平臺的相關需求。不僅可以實時采集PC104總線信號,而且可以通過輸出TTL電平信號控制總線上相關引腳來控制PC104主板的運行狀態。采用FPGA功能模塊作為檢測平臺的核心,在很大程度上提高了檢測平臺的可靠性和高效性。

2.1 BIOS啟動監測和POST上電自檢

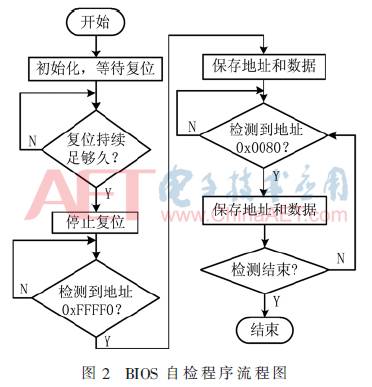

PC104主板的片外總線接口包括其地址信號線、鎖存地址信號線和數據信號線,其中包括20根地址信號線和16根數據信號線。監控平臺實現該功能基本原理是通過FPGA的信號采集端口監控PC104主板啟動時所有地址信號線和數據信號線的狀態來判斷各信號線的工作狀態是否正常。實現總線信號監控功能的具體FPGA程序設計流程圖如圖2。

2.1.1 BIOS啟動檢測

PC104主板的啟動過程包括加電、自舉、核心測試、POST自檢4項。監控平臺上電后開始測試,給PC104主板加電后向其發出復位命令,主板進入初始化過程及復位時長滿足后,釋放復位信號。FPGA的地址線監控端口開始讀取地址信號線的數據,如果讀到的地址線數據為0xFFFF0H,則開始執行監控PC104主板啟動碼的程序,并保存總線上的地址和數據。

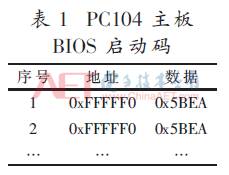

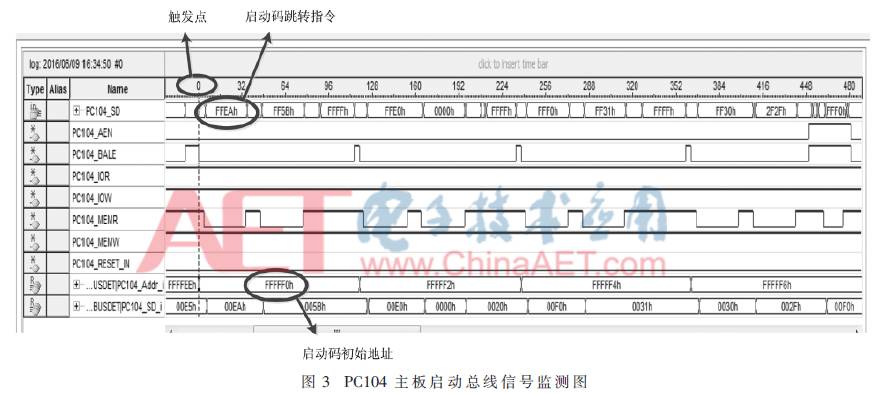

從PC104主板用戶手冊可知,其在啟動時,首先運行的通常都是一條“EA”跳轉指令,跳轉到實際BIOS ROM的開始地址。這個初始化搜索地址0xFFFF0H和隨后的CPU重定向的過程一般稱為自舉或引導,也可簡稱為BOOT。當PC104每次啟動時,FPGA采集總線上的地址和數據線信號理想情況下是會經過跳轉指令“EA”跳轉到某一固定地址單元,開始執行程序。分別監測兩塊正常運行主板的BIOS啟動碼實際被測數據,如表1所示。

從表中數據可以看到,主板正常啟動時,從0xFFFFF0地址開始執行程序,執行的第一條指令是0x5BEA,依此可以判斷該主板的數據和地址總線沒有故障。監測結果符合測試要求。

2.1.2 POST上電自檢

PC104主板初始化分為冷啟動(初次加電啟動)和熱啟動(通過FPGA發送復位命令重啟)。若是冷啟動,就會執行POST上電自檢;反之,將會跳過POST上電自檢。遇到錯誤時,單字節的POST碼會被寫入80H的I/O端口中,系統的初始化也將終止。如果自檢通過,則會向80H的I/O端口中返回0xFF。主板的自檢過程是判斷PC104主板是否正常的標準,所以POST自檢是判斷主板故障信息最重要的模塊之一。當FPGA監控到PC104主板啟動后,開始定時反復讀取80H的I/O端口中的信號。當讀取到0xFF時,保存該信號并返回給上位機系統,提示自檢通過;反之則返回故障指令并提示自檢未通過。通過對比3塊不同PC104主板的POST監控結果,并參考主板實際運行狀態可知符合測試要求。當測試過程中,如果主板剛啟動POST自檢代碼就監控到0xFF,同時起始代碼不再變化,那也可能是主板并沒有運行,BIOS自檢并沒有正常開始,應該重啟PC104主板,重新測試。POST上電自檢結果如表2所示。

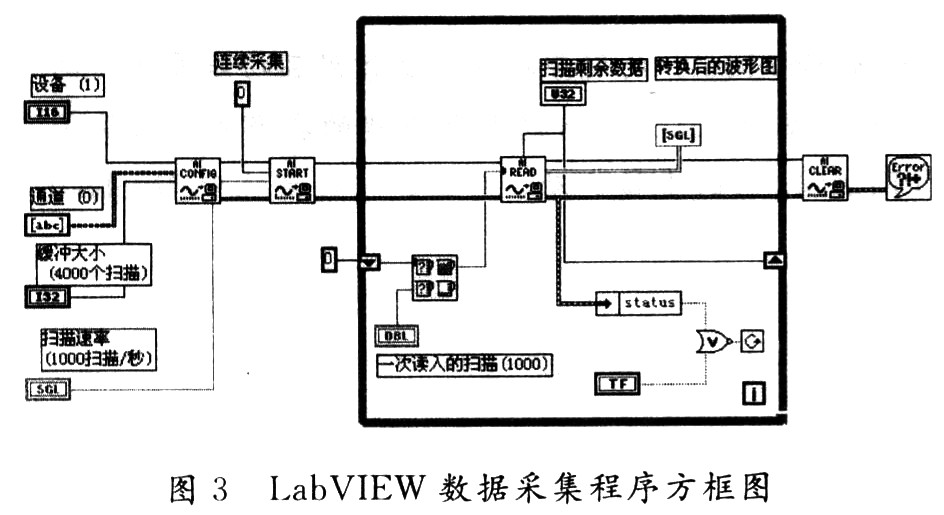

利用FPGA實時采集PC104主板在啟動過程中總線檢測的結果,如圖3所示。從圖中可以很直觀地看出PC104主板在啟動過程中所包括的初始化過程和POST自檢結果,符合其總線測試要求。

2.2 PC104復位與BIOS模式控制

監控平臺在運行過程中,會要求對于同一塊PC104主板進行反復測試。由于PC104主板的高集成度,并沒有復位按鈕,所以需要控制主板上的復位控制(Reset Switch)引腳進行復位控制。當上位機系統發出復位指令后,就需要FPGA給PC104主板的復位控制引腳發送一個延時復位命令,并監測啟動計時器。當復位時間到達后,釋放復位信號。

系統擴展模塊利用盛博科技生產的符合PC104總線標準的軟盤驅動控制器驅動裝有測試程序的硬盤,通過測試程序可以監控PC104主板的串口和鍵盤等接口的故障信息。為了設置PC014主板的啟動方式以及顯示器狀態和分辨率等基本硬件信息,需要在啟動時對其是否進入BIOS進行控制。通過FPGA的I/O口控制由繼電器和三極管組成的基本控制電路來控制主板的串行口連接器的DTR和RI引腳是否短接來控制其啟動過程中是否進入BIOS設置。

2.3 PC104關鍵信號測量

PC104主板總線控制信號線中有4個關鍵信號,包括3個時鐘信號和一個復位脈沖信號。

2.3.1 PC104總線時鐘頻率測量

FPGA常用測量頻率的方法有直接測頻法和等精度測頻法,其中直接測頻法又分為直接計數測頻法和測周期測頻法。直接測頻法的測頻精度與被測信號有關,被測信號頻率越高,測頻精度越高;實現簡單,對硬件資源要求不高。等精度測頻法的測頻精度與被測信號無關,僅與系統時鐘信號有關,系統時鐘信號頻率越高,精度越高;相比直接測頻法,等精度測頻法實現較復雜,需要FPGA系統的晶振頻率達到等精度測頻的測頻精度要求。

待測的時鐘信號分別是:REFRESH#存儲器刷新信號線由刷新控制器驅動,以表明將執行一個刷新周期;BCLK是由平臺電路驅動的系統總線時鐘信號線,正常運行狀態下頻率為6 MHz~8 MHz(±500 ppm),周期的占空比為45%~55%;OSC振蕩器信號線是由平臺電路驅動的時鐘信號,其頻率為14.318 18 MHz(±500 ppm),周期的占空比為45%~55%。其中OSC不與任何其他總線信號線同步。最小的待測頻率是6 MHz,可以選用直接計數測頻法,測量精度分別可達10-6和10-7級,滿足該頻率測量1%誤差的技術要求。直接計數測頻法實現過程簡單,計算量小,提高了監控平臺的運行速度。

2.3.2 PC104總線復位脈寬測量

脈寬測試是測量PC104主板復位過程中復位脈沖的脈寬,復位信號線由平臺電路驅動為有效狀態。任何接收到復位信號的總線資源必須立即使所有輸出驅動器處于三態,并進入適當的復位狀態。

FPGA監測脈寬通常采用脈沖計數法,即在待測信號的高電平或低電平用一個高頻時鐘脈沖進行計數,然后根據脈沖的個數計算待測信號寬度。待測信號相對于計數時鐘通常是獨立的,其上升、下降沿不可能正好落在時鐘的邊沿上,因此該法的最大測量誤差為一個時鐘周期。監控平臺FPGA采用50 MHz的高頻時鐘,脈寬測量精度可達2×10-8,滿足PC104主板監測復位脈寬測量的技術要求。

2.4 電源測量模塊

電壓監控模塊是基于ADI公司生產的AD7417設計的,AD7417為十位、四通道模數轉換器,片內帶有溫度傳感器。AD7417在降低功耗方面有非凡的性能,其自動掉電功能可以使芯片在輸出速率較低時啟動掉電模式來降低功耗。

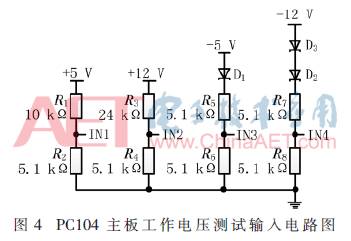

PC104主板工作電壓是+5 V,有些模塊的工作電壓是+12 V。AD7417擁有四路AD轉換通道,可以對于總線的±5 V、±12 V分別進行監測。利用FPGA的I/O口和AD7417的SDA、SCL構成雙線I2C串行總線接口,通過FPGA控制AD7417芯片分別采集PC104總線上的各路電源電壓,同時將采集到的結果進行AD轉換后上傳到FPGA處理。

電壓測試模塊輸入電路原理圖如圖4所示。總線正電壓采用電阻串聯分壓的方式得到可被AD7417識別的模擬電壓值;總線負電壓經過8.2 V的反向穩壓二極管后得到正電壓,再分壓為可識別電壓值。下面以+5 V測試輸入端口為例,介紹實際電壓值計算方法。

已知AD7417的參考電壓是內部參考電壓2.5 V,假設實際被測電壓為V1,AD7417輸入端口IN1被測電壓為V2,FPGA采集到的數值為x,則:

3 結論

本項目設計的FPGA監測程序不僅可以有效地記錄PC104的總線運行代碼,還能實時提取有效啟動代碼和故障監控碼,測量總線關鍵信號的頻率和脈寬。FPGA程序與上位機實時通信,可根據上位機的指令,實現信息上傳、復位控制及BIOS模式控制等功能。該設計經過多次測試,可以有效地檢測到故障PC104主板,并提供具體的故障信息。從檢測結果可以看出,基于FPGA設計的檢測程序在速度和功能上均能滿足PC104主板系統的檢測技術要求。本設計的系統操作方便,擴展性強,實用性好。目前應用該FPGA程序的PC104監控平臺達到技術要求,并通過驗收。

參考文獻

[1] 劉廣林.基于PC/104和ARM的工業控制平臺設計及應用[D].武漢:華中科技大學,2010.

[2] 楊勇智,黃勝倫,馮和軍,等.基于PC/104總線的某型飛機武器控制系統的ATS[J].空軍工程大學學報(自然科學版),2003,4(3):36-39.

[3] 張仲華,高曉莊,王大鵬.基于PC104的雷達主控單元檢測維修平臺[J].現代電子技術,2015,38(3):48-50.

[4] 陳芳.基于PC/104的ARINC 429通訊總線的設計與實現[D].南京:南京航空航天大學,2005.

[5] 陳正捷,何健.基于CPLD和PC104總線規范的嵌入式計算機主板檢測卡設計[J].測控技術,2006,2(25):331-336.

[6] 陳巖申,張波,管少輝,等.基于OMAPLl38和FPGA構架的PCI04主板檢測系統[J].計算機測量與控制,2015,23(5):1512-1514.

[7] 楊海鋼,孫嘉斌,王慰.FPGA器件設計技術發展綜述[J].電子與信息學報,2010,32(3):714-727.

[8] 張婉明,李琦,李金海,等.基于ARM與FPGA的便攜式GNSS信號采集回放系統設計[J].電子技術應用,2016,42(10):58-61.

[9] Altera Corporation,Terasic Technologies.DE0 user manual[EB/OL].(2011)[2017]http://DE0.terasic.com.

原文標題:【論文精選】PC104故障監控平臺FPGA程序設計

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

arm vs pc104

CPLD控制PC104總線時序問題

很想知道現在用PC104的人還多嗎?

使用VHDL語言和FPGA的DSP HPI口與PC104總線接口設計

怎么設計基于PC104總線的實時信號采集處理系統?

單片機溫度采集器與PC104分站的串行通信

基于PC104的陀螺儀動態測試系統設計

基于DSP與PC104高速通信接口設計

基于PC104總線的車載深度模擬器設計

基于PC104總線的故障診斷裝置的設計

PC104數據采集與檢測電路實現改進投彈裝備故障檢測方法

一文帶您熟悉pc104故障監控平臺

一文帶您熟悉pc104故障監控平臺

評論