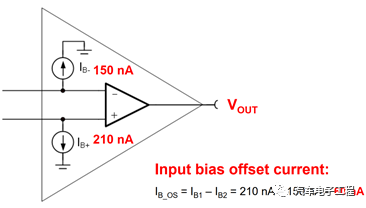

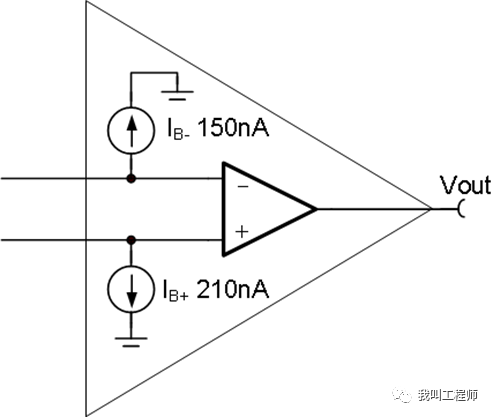

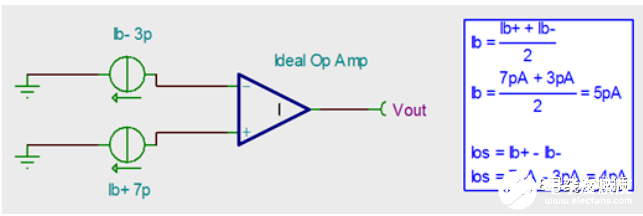

第一節要說明的是運放的輸入偏置電流Ib和輸入失調電流Ios .眾說周知,理想運放是沒有輸入偏置電流Ib和輸入失調電流Ios .的。但每一顆實際運放都會有輸入偏置電流Ib和輸入失調電流Ios .我們可以用下圖中的模型來說明它們的定義。

輸入偏置電流Ib是由于運放兩個輸入極都有漏電流(我們暫且稱之為漏電流)的存在。我們可以理解為,理想運放的各個輸入端都串聯進了一個電流源,這兩個電流源的電流值一般為不相同。也就是說,實際的運入,會有電流流入或流出運放的輸入端的(與理想運放的虛斷不太一樣)。那么輸入偏置電流就定義這兩個電流的平均值,這個很好理解。輸入失調電流呢,就定義為兩個電流的差。

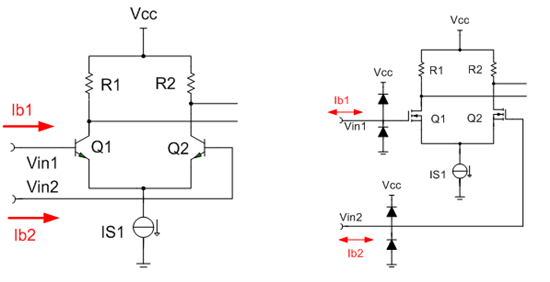

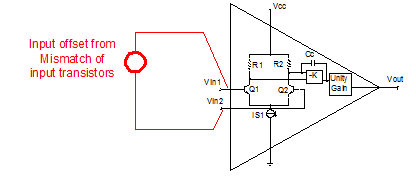

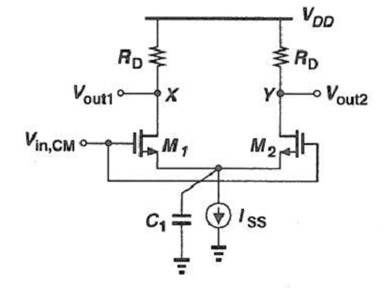

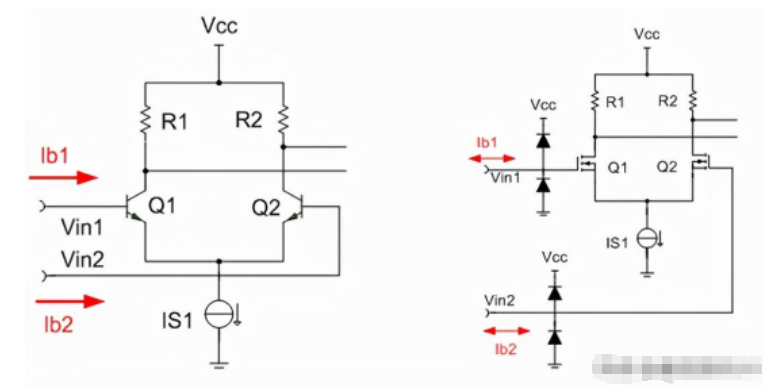

說完定義,下面我們要深究一下這個電流的來源。那我們就要看一下運入的輸入級了,運放的輸入級一般采用差分輸入(電壓反饋運放)。采用的管子,要么是三級管bipolar,要么是場效應管FET。如下圖所示,對于bipolar,要使其工作在線性區,就要給基極提供偏置電壓,或者說要有比較大的基極電流,也就是常說的,三極管是電流控制器件。那么其偏置 電流就來源于輸入級的三極管的基極電流,由于工藝上很難做到兩個管子的完全匹配,所以這兩個管子Q1和Q2的基極電流總是有這么點差別,也就是輸入的失調電流。Bipolar輸入的運放這兩個值還是很可觀的,也就是說是比較大的,進行電路設計時,不得不考慮的。而對于FET輸入的運放,由于其是電壓控制電流器件,可以說它的柵極電流是很小很小的,一般會在fA級,但不幸的是,它的每個輸入引腳都有一對ESD保護二極管。這兩個二極管都是有漏電流的,這個漏電流一般會比FET的柵極電流大的多,這也成為了FET輸入運放的偏置電流的來源。當然,這兩對ESD保護二極管也不可能完全一致,因此也就有了不同的漏電流,漏電流之差也就構成了輸入失調電流的主要成份。

下面列表中上表是bipolar的LM741的輸入偏置電流和輸入失調電流,這個電流流到外面電阻,即使是K歐級的,也會產生幾十uV的失調電壓,再經放大,很容易就會使輸出的電壓誤差到mV級。下表則是CMOSFET的OPA369的輸入偏置電流和輸入失調電流,這兩個值要小的多了,比較好的COMS運放輸入偏置電流和輸入失調電流的典型值可以做到小于1pA的目標。

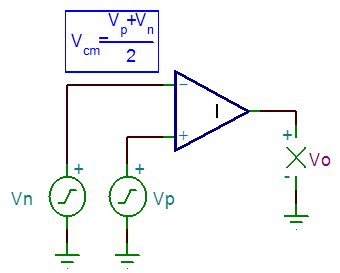

這里還要強調的是,ESD的反向漏電流是與其反相電壓有關的。因此當Vin=(Vcc-Vss)/2 時,加在兩個ESD保護二極管的電壓相當,他們的反向電流可以認為是近似相等的,此時理想情況是無電流流入或流出的,實際情況是電流達到最小值。因此這時有最小的偏置電流,當運放輸入端電壓Vin不等于(Vcc-Vss)/2,勢必造成一個二極管的反向電壓高,另一個低,此時兩個二極管的反向漏電流就不等了,這個差電流就會構成了輸入偏置電流的主要成份。這個現場稱為領節效應。因此要使FET輸入偏置電流最小,就要把共模電壓設置在(Vcc-Vss)/2處。

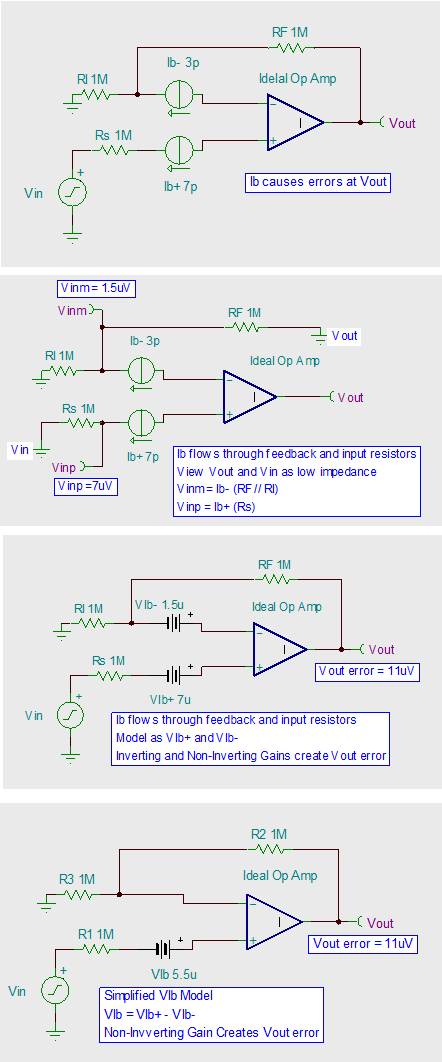

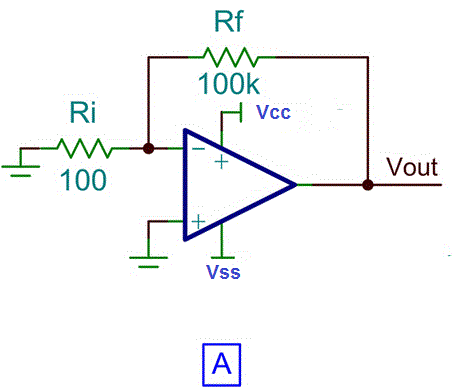

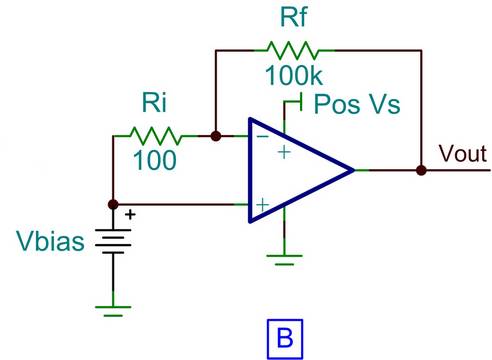

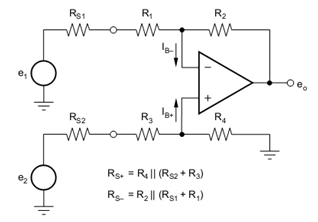

上面分析了定義和來源。下面就要說說這兩個參數對電路的影響了,輸入偏置電流會流過外面的電阻網絡,從而轉化成運放的失調電壓,再經運放話后就到了運入的輸出端,造成了運放的輸入誤差。這也就說明了,在反向放大電路中,為什么要在運放的同相輸入端連一個電阻再接地的原因。并且這個電阻要等于反向輸入端的電阻和反饋電阻并聯后的值。這就是為了使兩個輸入端偏置電流流過電阻時,形成的電壓值相等,從而使它們引入的失調電壓為0。這樣說,太抽象了,還是看下面一組圖容易理解一些。

再有一點,對于微小電流檢測的電路,一般為跨阻放大電路,如光電二極管的探測電路,一般有用光信號都比較微弱轉化的光電源信號更微弱,常常為nA級甚于pA級。這個電路的本意是想讓光電流向反饋電阻流動從而在放大電路輸出端產生出電壓。如果選用的運放的輸入偏置電流過大,剛這個微弱的光電流會有一部分流入到運放的輸入端,而達不到預設的I/V線性轉化。

還需要注意的一點時,許多運放的輸入失調電流會隨著溫度的變化而變化,如下圖所示OPAl350的輸入失調電流會在高于25度時快速的升高。在100度時的輸入偏置電流是25度時的幾百倍。如果設計的系統是在很寬的溫度范圍內工作,這一因素不得不考慮。

以上啰啰嗦嗦的講了運放的輸入偏置電流和失調電流,希望對大家有用。下一節中將詳細剖析其它參數。

2—如何測量輸入偏置電流Ib,失調電流Ios上一節講了運放輸入偏置電流和輸入失調電流。這一節給出輸入偏置電流測量方式。 總體來說主要有兩種測試方法, 一種是讓輸入偏置電流流入一個大的電阻,從而形成一個失調電壓,然后放大失調電壓并進行測量,這樣就可以反算出輸入偏置;另一種方法是讓輸入偏置電流流入一個電容,用電容對這個電流進行積分,這樣只要測和電容上的電壓變化速率,就可以計算出運放的偏置電流。

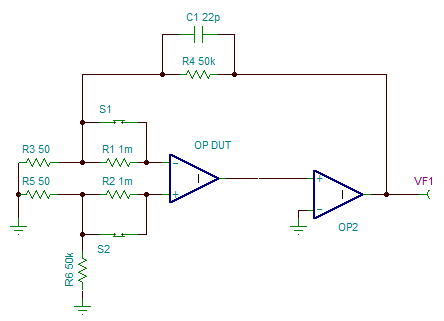

先介紹第一種方法,具體電路如下圖所示,C1是超前補償電容以防止電路的振蕩,根據實際電路選擇。OP2是測試輔助運放,需選低偏置電壓和低偏置電流的運放。測試步驟和原理下面一步一步進行推算。

(1)首先測試運放的失調電壓。關閉S1和S2,測試出OP2運放的輸出電壓記下Vout 。則輸入失調電壓為:

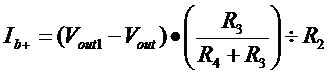

(2)打開S2,待測運放的Ib+流入R2,會形成一個附加的失調電壓Vos1,測試出OP2運放的輸出電壓記下Vout1。則運放同向輸入失調電壓為:

(2)關閉S2,打開S1,待測運放的Ib-流入R1,會形成一個附加的失調電壓Vos2,測試出OP2運放的輸出電壓記下Vout2。則運放反向輸入失調電壓為:

(4)運放輸入偏置電流為

Ib=[(Ib+)+(Ib-)]/2

運放輸入失調電流為

Ios=(Ib+)-(Ib-)

這種測試方法有幾個缺點,一個是使用了很大的電阻R1和R2,一般會是M歐級,這兩個電阻引入了很大的電壓噪聲。受到電阻R1和R2的阻值的限制,難以測得FET輸入運放的偏置電流。

第二種方法測試方法,是讓運放的輸入偏置電流流入電容,具體測試如下圖。從圖中的公式很容易理解測試的原理,這個測試的關鍵,是選取漏電流極小的電容。

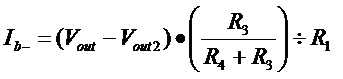

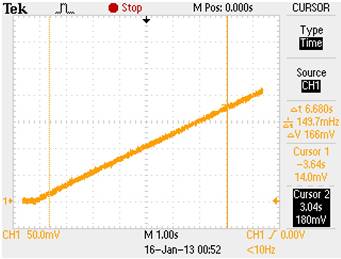

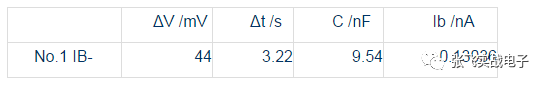

(1)打開S1,IB+流入電容C,用示波器觀察Vo的變化,結果如下圖,按上圖的方法就可以計算出IB+。

(2)關閉S1打開S2,IB-流入電容C,用示波器觀察Vo的變化,結果如下圖,可以計算出IB-。

(3)再根據定義就可以計算出運放的輸入偏置電流和失調電流。

這種測試方法可以測得fA級的失調電流。測試時需要選用低漏電流的電容,推薦使用極低漏電流的特氟龍電容,聚丙烯(PP)電容或聚苯乙烯電容。

再分享一個經驗,就是貼片電容在焊接過程中,由于引腳可能殘留焊錫膏等雜質,會使FET運放的漏電流大大的增加。曾經測試一個偏置電流為小于10pA級的運放,由于沒有對引腳 進行清洗,結果測得結果出現了很大的誤差,或者叫差錯,達了nA的水平了。

3—輸入失調電壓Vos及溫漂在運放的應用中,不可避免的會碰到運放的輸入失調電壓Vos問題,尤其對直流信號進行放大時,由于輸入失調電壓Vos的存在,放大電路的輸出端總會疊加我們不期望的誤差。舉個簡單,老套,而經典的例子,由于輸入失調電壓的存在,會讓我們的電子秤在沒經調校時,還沒放東西,就會有重量顯示。我們總不希望,買到的重量與實際重有差異吧,買蘋果差點還沒什么,要是買白金戒指時,差一克可是不少的money哦。下面介紹一下運放的失調電壓,以及它的計算。最后再介紹一些低輸入失調電壓運放。不足之處,多多拍磚。

理想情況下,當運放兩個輸入端的輸入電壓相同時,運放的輸出電壓應為0V,但實際情況確是,即使兩輸入端的電壓相同,放大電路也會有一個小的電壓輸出。如下圖,這就是由運放的輸入失調電壓引起的。

當然嚴格的定義應為,為了使運放的輸出電壓等于0,必需在運放兩個輸入端加一個小的電壓。這個需要加的小電壓即為輸入失調電壓Vos。注意,是為了使出電壓為0,而加的輸入電壓,而不是輸入相同時,輸出失調電壓除以增益(微小區別)。

運放的輸入失調電壓來源于運放差分輸入級兩個管子的不匹配。如下圖。受工藝水平的限制,這個不匹配是不可避免的。差分輸入級的不匹配是個壞孩子,它還會引起很多其他的問題,以后介紹。

曾經請教過資深的運放設計工程師,據他講,兩個管子的匹配度在一定范圍內是與管子的面積的平方根成正比,也就是說匹配度提高為原來的兩倍。面積要增加四倍,當到達一個水平時,即使再增加面積也不會提高匹配度了。提高面積是要增加IC的成本的哦。所在有一個常被使用的辦法,就是在運放生產出來后,進行測試,然后再Trim(可以理解為調校了)。這樣就能使運放的精度大在提高。當然,測試和Trim都是需要成本的哦。所以精密運放的價格都比較貴。這段只當閑聊,呵呵。

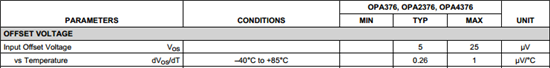

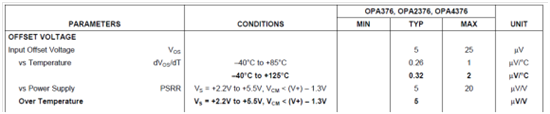

我們關注輸入失調電壓,是因為他會給放大電路帶來誤差。下面就要分析它帶來的誤差。在計算之前,我們再認識一個讓我們不太爽的參數,失調電壓的溫漂,也就是說,上面提到的輸入失調電壓會隨著溫度的變化而變化。而我們的實際電路的應用環境溫度總是變化的,這又給我們帶來了棘手的問題。下表就是在OPA376datasheet上截取下來的參數。它溫漂最大值為1uV/℃(-40℃to 85℃)。一大批運放的Vos是符合正態分布的,因此datasheet一般還會給出offset分布的直方圖。

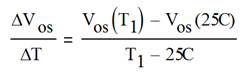

當溫度變化時,輸入失調電壓溫漂的定義為:

剛忘記了另一個重要的參數,就是運放輸入失調電壓的長期漂移,一般會給出類似uV/1000hours或uV/moth等。有些datasheet會給出這一參數。

下面舉例計算一下OPA376,在85℃時的最大失調電壓,主要是兩部分,一部分是25度時的輸入失調電壓,另一部分是溫度變化引起的失調電壓漂移。

具體步聚如下圖。從結果來看似1uV/℃溫漂,在乘上溫度變化時,就成為了誤差的主導。因此,如果設計的電路在寬的溫度范圍下應用,需在特別關注溫漂。

Vos(85℃)= 25uV+60uV=85uV.

如果放大電路的Gain改為100,則最大輸出失調電壓就為8.5mV。這是最差的情況。

關于輸入失調電壓的測試在"運放參數的詳細解釋和分析-part2,如何測量輸入偏置電流Ib,失調電流Ios"中有介紹,感興趣的話,可以去看看。還有簡單的測試方法,如下圖:

Vos = Vout/1001

需要提醒的是,使用簡易方法測試單電源運放的輸入失調電壓時,需要將輸入端短路并提供一個低噪聲的穩定電壓偏置。如下圖。

下面列一些低溫漂運放,它們的最大漂移只有0.05uV/℃。輸入失調電壓Vio最大值只有5uV。

4—運放噪聲快速計算本文不是研究運放的噪聲理論,TI的資深應用經理Art Kay已經寫過一系列的文章來分析運放的噪聲,相信大多數模擬電路工程師都讀過。國內還有工程師把它翻譯成中文。

今天主要從自上而下的角度分析一下運放電路的噪聲組成,計算時幾個主意要點和繁索的地方、最主要的是提供給大家一個方便的計算小工具,很好用,讓噪聲計算變的簡單。

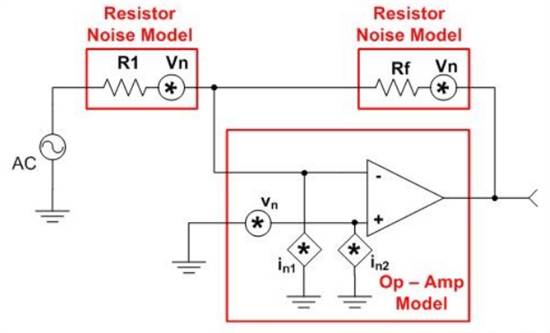

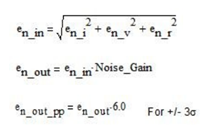

運放構成的反向放大電路中,噪聲主要來源于三個方面

(1)運放的輸入噪聲電壓en(在datasheet中有數據和曲線)

(2)運放的輸入電流噪聲in(在datasheet中同樣可以找到數據和曲線)。這需要流過電阻后轉化為電壓噪聲。

(3)設置放大倍數的電阻R1和Rf的熱噪聲,也就是可以通過經典公式算出來的。Noise =√(4kTKRΔf)。這是不可避免的。很多情況下會成為主要噪聲來源。

運放噪聲的計算就是將這三個值一一求出來,由于這些噪聲是不相關的。它們的矢量和即為運放的總輸入噪聲。再乘上噪聲增益就可以得到輸出端噪聲,公式如下。看似簡單實則很麻煩。

我們將計算得來和輸入總噪聲加到理想運放的正輸入端,就得到了運放的噪聲模型。注意,是正輸入端哦,因此不管同向放大電路,還是反向放大電路對噪聲的增益均為G=1+Rf/R1。我們可以簡單理解為噪聲是疊加到運放輸入端的一個信號。如下圖

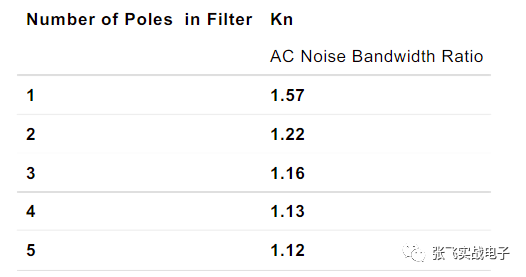

上面說了一個重要問題,運放的噪聲增益。還要一個重要問題,運放的噪聲帶寬,datasheet中給出的運放噪聲參數一般為譜密度值如1.1nV√Hz。也就是說,需要對它在噪聲帶寬中進行積分才可以得到噪聲的RMS電壓值。噪聲帶寬不同于信號的-3dB帶寬。確切的說是Brickwall 濾波器的帶寬。簡單說,就是把實際的濾波器響應曲線,在保證包含面積不變時轉化成理像低通濾波器時的帶寬。好在我們可以查表得到,N階濾波器的-3dB帶寬與Brickwall 濾波器的帶寬換算系數。如下表

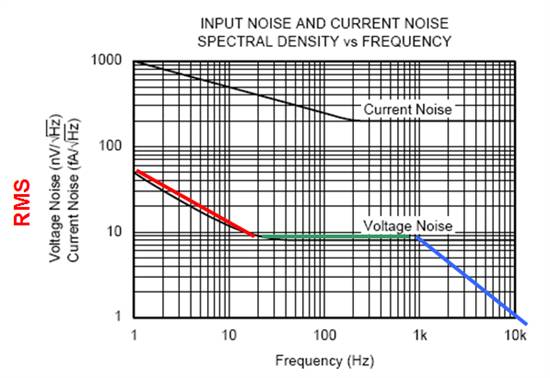

看上去好麻煩,不要急,還有更麻煩的事,就是運放的輸入電壓噪聲和輸入電流噪聲,是與頻率有關的,在極低頻率時(0.1Hz-10Hz)主要是1/f噪聲,以后主要是白噪聲,如下圖,

需要對其分段積分。

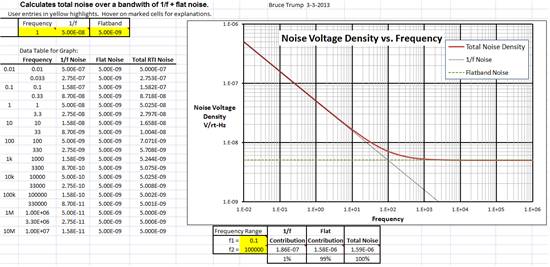

如下圖是噪聲電壓的計算,只要輸入1/f噪聲在特定頻率的值,和平坦噪聲的值,就可以計算出不同頻率下的噪聲密度。輸入頻帶的起止頻率,就可以分析出這下頻帶內各個噪聲的貢需率。

下圖是計算同向放大電路的噪聲密度的方法(以OPA627為例),只需輸入信號源電阻,運放電壓噪聲,運放電流噪聲,電阻值和溫度,就可以計算出來輸出電路的噪聲密度,這大大提高了計算效率。計算結果同樣給出了各個噪聲源的貢需率,方便我們進行噪聲優化設計。

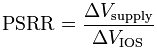

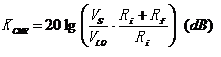

這一小節談談運放的電源抑制比。在理想運放中,運放的特性不會隨電源電壓的變化而變化。當然,分析理想運放時,我們使用的電源,也會被假設成理想電源。但實際情況并非如此,實際的運放,電源電壓發生變化時,總會引起運放參數的變化。這就引出運放的一個重要參數,運放的電源抑制比PSRR。維基百科中給出了PSRR的詳細定義,就是當運放的電源電壓發生變化時,會引起運放的輸入失調電壓的變化,(又是失調電壓),這兩個變化的比就是運放的PSRR。如下式

通常用dB表示。PSRR = 20log(⊿Vcc/⊿Vios)。有些數據手冊中,也會通過失調電壓對電源變化的比來表示。單位一般用uV/V。如下圖,是OPA365的datasheet中的表示,這個也不難理解。我們不用為找不到上式定義的比率dB值,而感動傷心。這兩種表示方法,都可以讓我們清楚的理解到運放對電源電壓變化的抑制能力。

PSSR為有限值的原因,也是來源于運放差分輸入管的不完全匹配。下面著重討論它的影響。如下圖是對OPA376運放的一個計算實例。當電源電壓變化500mV時,就會引起輸入失調電壓10uV的變化,如果放大倍數為2,剛輸出端變會產生20uV的變化。一些電路放大的倍數更大,則輸出失調電壓變更大。這足以使一個輸送給16bitsADC的信號產生誤差。(16位ADC的一個LSB對應的變化為15ppm of FSR)。

上面一節討論的是直流DC電源抑制比。實際的應用電路中,運放的電源電壓可能是不變的。

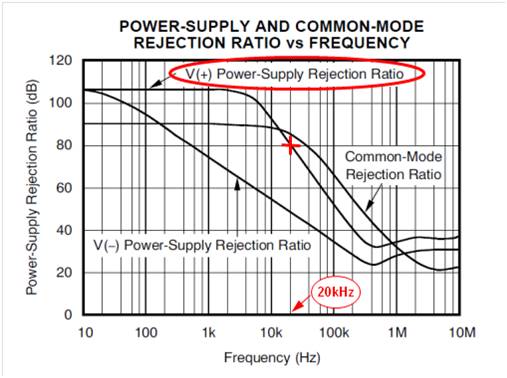

下面就來分析另一個關鍵的參數,運放交流電源抑制比AC-PSRR。這個參數相對在實際的應用電路中顯得更有價值,卻時常被我們忽略。運放的datasheet參數表格中往往給出的是直流PSRR。而AC-PSRR往往以圖表的形式給出,我們常常忽略了圖表中的信息。然而,被我們忽略的常常是關鍵。下圖是OPA376的datasheet中的PSRR圖表,從圖表中我們可以看出兩點信息:(1)PSRR是隨電源交流頻率的上升而下降的,(2)正負電源的AC-PSRR不同。

以上兩點會在應用電路中引起令人不快的問題,下圖是說明了一個在電源上出現的峰峰值為100mV,頻率為20kHz的紋波,會使放大電路的輸出端增加一個20uV,20kHz的噪聲信號。

通常,運放的應用電路中使用線性電源對運放供電,對運放的電源進行濾波。但在一些手持式設備為了提高效率,降低功耗,不得不使用開關電源對運放供電,開關電源的頻率往往超過100kHz,甚至到MHz的水平。在這個頻率點上,運放的PSR能力下降的非常快。如OPA376在100kHz時,PSRR只有50dB了。與高于100dB的DC-PSRR相去甚遠。另一個問題在單電源的手批設備中,開關電容的“buck-boost”常被用來將正電源轉化為負電源。看到上圖中運放對負向電源的AC-PSRR后,會讓我們出點冷汗了。 運放的PSRR就要是指電源電壓變化引起輸入失調電壓的變化。因此可以參照測量失調電壓的方法測量PSRR。把電源電壓變化一個⊿Vcc,然后測量計算⊿Vios,就可以計算出PSRR。

通常,運放的應用電路中使用線性電源對運放供電,對運放的電源進行濾波。但在一些手持式設備為了提高效率,降低功耗,不得不使用開關電源對運放供電,開關電源的頻率往往超過100kHz,甚至到MHz的水平。在這個頻率點上,運放的PSR能力下降的非常快。如OPA376在100kHz時,PSRR只有50dB了。與高于100dB的DC-PSRR相去甚遠。另一個問題在單電源的手批設備中,開關電容的“buck-boost”常被用來將正電源轉化為負電源。看到上圖中運放對負向電源的AC-PSRR后,會讓我們出點冷汗了。 運放的PSRR就要是指電源電壓變化引起輸入失調電壓的變化。因此可以參照測量失調電壓的方法測量PSRR。把電源電壓變化一個⊿Vcc,然后測量計算⊿Vios,就可以計算出PSRR。

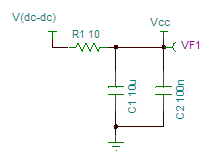

上面提到運放使用開關電源供電時,由于PSRR隨頻率的上升而下降。使得運放在輸出端有很大的紋波噪聲。下面提供一個簡單的辦法,只適合于低功耗的運放。在DC-DC輸出的電源與運放的電原之間加一個小電阻(如下圖),如果運放的功耗小于5mA。則這個10歐電阻產生的壓降小于50mV。

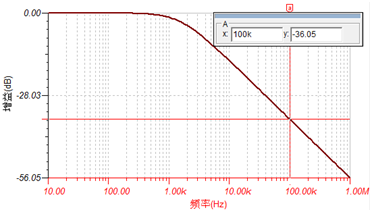

下面看一下這個電路的效果如下圖,在100kHz時頻響為-36dB這相當于給運放增加了36dB的PSRR。這個功耗損失換取這個效果還是很值得的。

另一個有效的方法是,使串心電容給電源濾波,串心電容是一種三端電容,但與普通的三端電容相比,由于它直接安裝在金屬面板上,因此它的接地電感更小,幾乎沒有引線電感的影響,另外,它的輸入輸出端被金屬板隔離,消除了高頻耦合,這兩個特點決定了穿心電容具有接近理想電容的濾波效果。關于串心電容,感興趣的可以查閱相關資料。

7—共模抑制比CMRR運放的共模擬制比,是常被大家關注的一個運放參數,尤其是在差分放大器和儀表放大器中。但這一小節只討論運放的共模抑制比,以及CMRR帶來給運放的誤差。關于差分放大器和儀表放大器,以后另文討論。

在開始討論運放的共模抑制比,我們先了解一下運放的共模輸入電壓,運放的共模輸入電壓是指運放的兩個輸入引腳電壓的平均值,注意是“平均值”,這一點很重要,如下圖所示。對于雙極性輸入級的運放,運放的共模輸入電壓,一般達不到電源軌。而有些rail to rail輸入運放的共模電壓是可以達到電源軌的。

在理想運放中,運放的差模放大倍數為無窮大,共模放大倍數為0。理想總是美好的,現實總是殘酷的。因此實際運放確不是這樣的,實際運放的差模放大倍數也不會是無窮大,共模放大倍數也不會是零。我們就這樣定義運放的共模抑制比(CMRR),差模增益與共模增益的比,如下式

還有一個參數非常常見,就是CMR,它其實是CMRR的對數表示,如下式:

不過這兩個參數經常被混用。我們只要了解他們都是在表示,運放對共模信號的抑制能力就可以了。

運放只所以會對共模信號能夠進行放大,當然這是我們不期望的,但也是不可避免的。主要來源于下面幾個原因:

(1) 運放差入輸入級的不匹配。這又可分為以下的原因引起的不匹配:

1) 源極或漏極電阻的不匹配,

2) 信號源電阻

3) 柵極-漏極之間的結電容

4) 正向跨導的不匹配

5) 柵極漏電流

(2) 拖尾電流源的輸出阻抗

(3) 拖尾電流源的寄生電容會隨頻率的變化而變化

下面我們就挑幾個上面的原因看一下它們的影響:

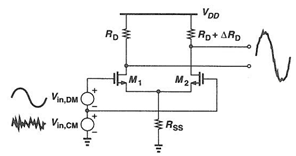

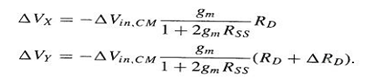

(1) 電阻的不匹配,如下圖所示,由于電阻的不匹配,一個共模電壓的變化ΔVin,會在X,Y點轉化為一個差模電壓。

計算如下,這個由失配阻ΔRd引入的差模信號,就會轉化為差分級輸出信號的噪聲。

(2) 輸入晶體管的不匹配,管子的不匹配,會引起兩管子的電流的微小差別,并且兩個的跨導是不一樣的。

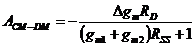

由于輸入級管子的不匹配,會將共模信號轉化為一個差模的誤差,可以用下面的公式表示,它表示失配跨導引起的CMRR。

(3) 再介紹一個原因,就是拖尾恒流源的寄生電容會隨頻率變化而變化。這會引起這個恒流源電流的變化,差分輸入端射極或源極電阻用恒流源代替的目的是保持電流恒定和高阻抗。但它的電流如果隨頻率發生變化,勢必降低差分輸入端的共模抑制能力。

上一小節簡單介紹了,共模抑制比的定義,以及引起它的原因。下面就介紹一下,它的影響。本系列貼子的目的是說清楚運放參數的定義,分析引起這個問題的原因,介紹明白這個參數對電路的影響,最后盡力介紹一些經驗方法來盡可能的減少和避免這些影響。

簡單來說,CMRR是運放的一個直流精度參數,它的好壞,會引起運放的放大電路的輸出誤差的好壞。

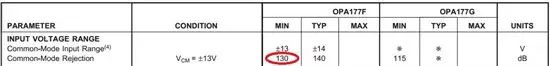

下表是OPA177的datasheet中標出的共模抑制比CMRR,注意表中標定的值是指,在輸入共模電壓范圍內的直流共模抑制比。它的最小值為130dB,是非常高的值。

由于CMRR是有限值,當運放輸入端有共模電壓Vcm時,它會引入一個輸入失調電壓,我們稱之為Vos_CMRR。如下圖所示

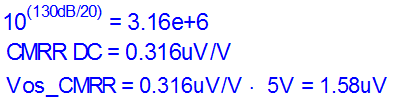

當共模電壓為5V時,這個失調電壓為1.58uV。計算過程如下,直流共模抑制比轉化為比率為:

對于上圖中的G=2的電路,則輸出端誤差為3.16uV。對于基準源為2.5V,雙極性輸入的24位ADC來說,為相當于引起了11個LSB的直流誤差了,直接影響到最后四位的精度了。

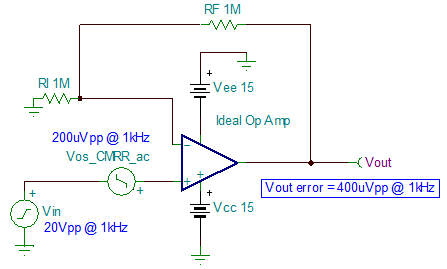

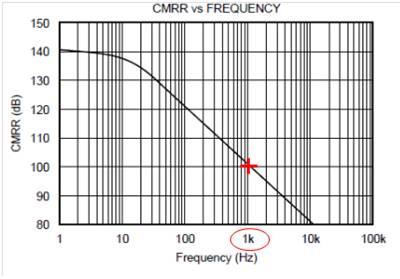

下面介紹另一個不好的影響,運放的CMRR是隨頻率的增加而降低。Datasheet中通常會給出一個曲線圖來表示這一變化。如下圖,這一點是一個非常令人不爽的特性。

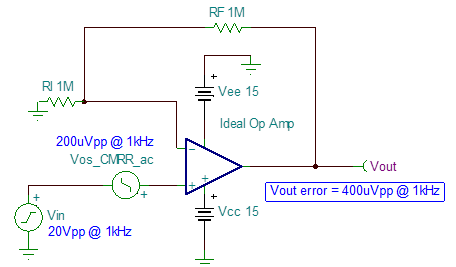

我們可以計算一下這一特性的影響,如下圖所示,當共模信號為一個20Vpp@1KHz的正弦信號時,它引入的輸入失電壓將是Vos_CMRR_AC=200uV@1kHz。對于Gain=2的放大電路,它的輸入誤差信號將為 400uV@1kHz。

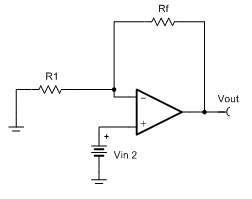

有一點需要引起注意,對于反向比例放大電路,如下圖,它的同向端是接入到地的,由于“虛短”。此放運放的共模信號將為0,并且不隨信號的變化而改變。因此共模信號引起的誤差很小。

而對于同向比例放大電路,如下圖,它的同向端是接是接的信號,由于“虛短”。此放運放的共模電壓就是信號的電壓。如果信號本身是一個頻率很高的信號,幅值也很大。那么由這個信號引 入的Vos_CMRR_AC執必會非常大。此時應選用在信號頻率上 CMRR依然很高的運放。經過上面的分析,即使這樣,Vos_CMRR_AC的影響可能也會是非常嚴重的。

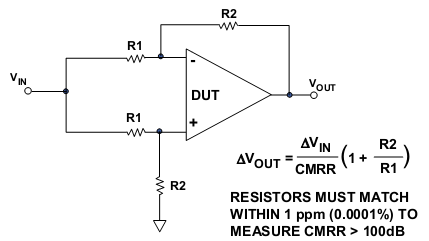

最后簡單介紹一下運放的CMRR測試,通常人們會想到有下圖的方法來測試CMRR,這種方法看似簡單,但存在一個很大的問題,就是它需要的電阻匹配度非常高,為發測CMRR>100dB的運放,需要1ppm以下的電阻。這幾乎不實用。

簡單易行的方式是下圖的方式。它對電阻的匹配度要求要低的多。

設信號源輸出電壓為VS,測得輔助運放輸出電壓為VL0,則有

上節中詳細分析了運放的主要直流參數。我們分析它們的原因就是,它們會給我們的電路引入直流誤差。本貼的主要目的是把影響運放直流誤差的原因都找出來,并且說明了它是怎樣影響的。以便工程師在設計精密放大電路時多加注意。

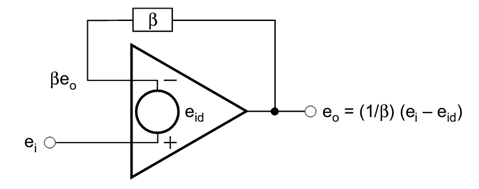

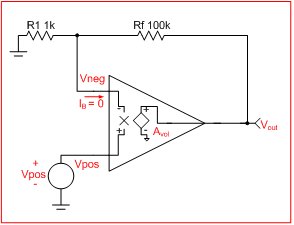

首先讓我們看一下,同放放大電路的理論模型,如下圖

這個電路在運放的應用電路中,再長見不過了。它的輸出為eo. 等于閉環增益(1/β)乘以輸入信號,這里的。輸入信號我們要多加注意了,它是由電路的輸入信號ei減于運放引入的誤差eid構成的。式中β是反饋系數,對于像下圖這樣的典型同向放大電路,它的值就是R1/(R1+R2)。這在模電課本中都有詳細敘述,不過多啰嗦。本文更要關注的是eid。

對于eid,我們的第一反應可能會是輸入失調電壓offset,再進一步的反應是輸入偏置電流流過電阻網引起的誤差電壓。可事實,遠不只這兩個因素,它倆還有七大姑八大姨的都來湊熱鬧。那我們就展示出它的真面目:

上式等號右邊的項夠多吧。真沒讓我們失望,這么多參數,參于到制造直流誤差的行列中。當然這些參數,也就是在part1-part8中提到的參數。

10— 放大電路直流誤差(DC error)的影響因素讓我們再來認真看一下上一小節中提到的公式:

下面我們一項一項的來看看他們吧。

(1) Vos, 輸入失調電壓,大家都熟,不多廢話。它更壞的一點是它不是一個老實待著的值,它會隨著溫度變化漂移呢。

(2) Ib+, 同向端輸入偏置電流,它流過同向端等效阻抗,形成一個誤差電壓。

(3) Ib-, 反向端輸入偏置電流,它流過反向端等效阻抗,形成一個誤差電壓。

有人可能注意了,輸入端阻抗怎么計算呢。下面的圖一看就明白了。簡而言之吧,輸入電阻(信號源電阻加輸入端電阻)與反饋電阻的并聯。千萬別忘了信號源電阻哦,因為我們時常選用高阻抗的傳感器做信號源。

(4) en, 等效輸入噪聲。這個值,我的理解可不只是datasheet中給定的en如1.1nV√Hz。它是集成了電壓噪聲,電流噪聲和電阻噪聲三都的貢獻的。是所有噪聲等效到輸入端的值。具體請參照Art Kay的文章和本系列博文的part4。

(5) eo/A, 這個表達式,可能很多人從來沒有關注過,有這一項的原因是,運放的開環增益A不為0。這也就是因為輸入貼值的不同,而引起的等效輸入誤差的不同了,舉個例子吧,如果輸出值是5V。開環增益是100dB,不低了吧。它的折算到輸入端的誤差就有50uV啊。不是小數目了。

(6) eicm/CMRR, 這個不用多說,輸入端的同模電壓除以共模抑制比。又有一點不好的地方,運放的CMRR可是隨共模信號頻率的增加而下降的。好多運放的CMRR在共模信號到10KHz以上時,就比直流下降了幾十個dB呢

(7) ΔVs/PSRR,電源電壓的變引入的誤差。同樣的,交流PSRR在隨頻率的增高,而下降。

看了這些,可能還會以為,這點小誤差是毛毛雨了,至多到mV級,甚至在uV級,不要忘了,它還要乘上一個增益Gain呢。假如輸入誤差是100uV。增益為100倍,則輸出的誤差信號,就是10mV。

Input_errorx Gain=Output Error

如果還覺得沒什么,那再講一個經驗值吧,一個滿量程為5V的16位ADC的一個LSB約為75uV。只要75uV的誤差就會引起ADC的一位的變化。假如放大電路的輸出誤差信號是1mV的話,這個信號給ADC,直接引起的誤差就是13個LSB以上。

這個Output error,真是魚龍混雜。有直流成份,這個可通過ADC采樣后校正去除掉。有噪聲信號,還有交流的成份。最不期望的,它還會隨溫度漂移呢。

我們在設計電路中,可以通過上面的分析,找出引起直流誤差的主要因素,然后努力減小之。

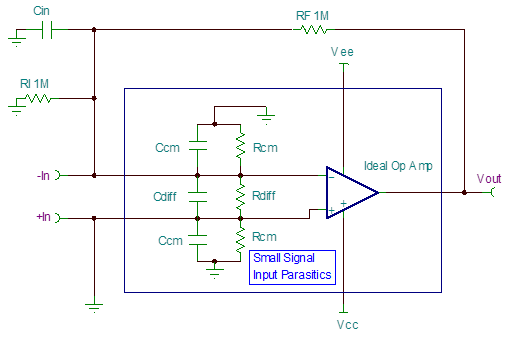

11—輸入阻抗和輸入電容下圖形象的說明了運放的輸入端阻抗的特性。主要有兩個參數,輸入阻抗和輸入電容。對于電壓反饋型運入,輸入阻抗主要由輸入級的決定,一般BJT輸入級的運放。的共模輸入阻抗會大于40MΩ。差模輸入阻抗大于200GΩ。對于JFET和CMOS輸入級的運放,輸入阻抗要大的多。這個阻抗通常表現為電阻性。作為常識被我們所熟知。

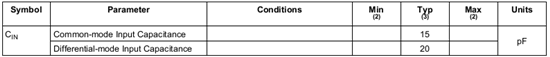

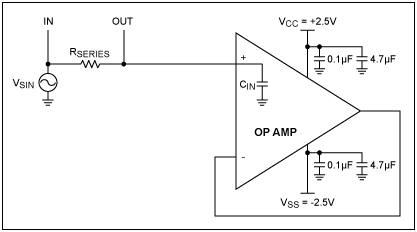

更值得我們多加關注的是運放的輸入電容。這個參數通常在datasheet的表格中所列出,但常被忽視。運放的輸入電容,通常分為共模輸入電容Ccm和差模輸入電容Cdiff。如下面是OPA376的datasheet中列出的輸入電容。

對于有EMI抑制特性的運放,如LMV832,它的輸入電容會被設計的正大的些。下面是帶EMI抑制功能的LMV832的輸入電容值。

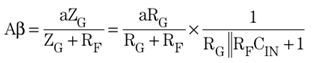

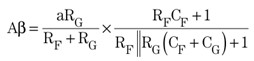

運放的輸入共模電容Ccm 和差模電容 Cdiff會形成運放的輸入電容 Cin。在許多應用中,運算放大器的輸入電容都不會造成問題。但在某些應用中會引起放大電路的不穩定。尤其是反向輸入端的電容,是放大電路不穩定的幾大罪魁禍首之一。如下圖所示是運放在有輸入電容的影響下的模型。

這個反向輸入端的電容會在運放的環路增益中引入一個極點。正是這個極點的存在,在某些條件下,可能會引起放大電路的不穩定。

運放輸入電容引入的極點如下式。即使這個極點0-dB交截越頻率之內,而是非常靠近0-dB交越頻率,它也有可能引起問題。在這個極點的頻率點上,相位會有45度的相位延遲,它很可能減少放大電路的相位裕度。如放大電路的0-dB交截越頻率是2MHz。在2MHz處的相位裕度是89°。 如果這個極點的頻率點也在2MHz處,它將使相位裕度減少45°。而變為φ = 89° – 45° = 44°。 44度的相位裕度就顯得的不夠了。

通常放大電路的輸入電容不只由運放的輸入電容組成,還包括布線引起的雜散電容和引腳電容。應盡量避免運算放大器反相輸入端存在外部雜散電容,尤其是在高速應用中。反相輸入周圍區域應去除接地層,從而最大程度地減小PC板雜散電容,此外,該引腳的所有連接都應盡量短。

在一些應用,常會加入反饋電容來增加放大電路的穩定,加入反饋電容后的電路的環路增益為,可見反饋補償電容給環路增益中引入了一個零點。

通常情況下我們可以在運放的datasheet中得到運放的輸入電容Ccm和Cdif。這些值通常是典型值。有某些情況下,可能需要實測一下運放的輸入電容,下面提供一種實用的測試方法。

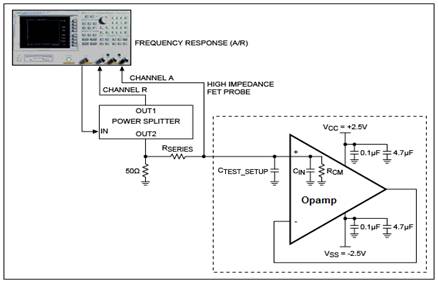

下圖是測試的原理圖,基本測試原理是把運放接成跟隨器,然后在同向輸入端串聯一個電阻(阻值一般在100K-1M之間),這個電阻與運放的輸入電容會形成一個RC電路,我們測試出這個電路的-3dB頻點,已知串聯電阻。就可以計算出運放的輸入電容。這里需要注意的是,電阻也是有等效并聯電容的。如一個典型的1/4W電容的等效并聯電容約為0.3pF。我們可以通過串聯電阻的方法來減小電阻的等效并聯電容。

下面的圖片是實際測試的Setup。使用到的儀器有網絡分析儀,高阻抗FET探頭。和功耗分離器。為什么不用示波器呢?這是有原因的。

由于運放的輸入電容通常是小于10pF的。示波器的探筆的電容通常是在10pF左右。如果用示波器探筆去測量運放的輸入電容根本就無法測準。因此需要選用電容小于1pF的,高阻抗FET探頭如Tektronix? P6245。

下面簡要介紹一下測試方法:

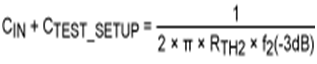

(1)首先要測試未安裝運放時PCB的雜散電容,網絡分析儀的測試結果讀出-3d頻點f1。并計算出雜散電容:

(2)在電路中安裝上運放,然后用網絡分析儀測試出-3dB頻點f2。并計算出運放輸入電容與雜散電容的和:

(3)如果我們選取的串聯電阻遠小于運放的共模電阻,則可以看作Rth1=Rth2。則此時上式可以寫為:

這樣,求差,就可以計算出運放的輸入電容了。

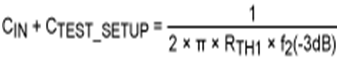

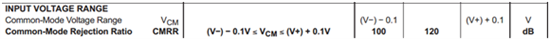

13—軌至軌輸入(rail to rail input)隨著單電源運放的廣泛的運用,運放的軌至軌輸入(rail to rail input)成為一個時髦的詞。現在大部分低電壓單電源供電的運放都是軌至軌輸入的。

先說兩句廢話,解釋一下軌至軌,這里的軌指的是電源軌,運放的兩個電源供電電壓如+/-15V。這兩個電源電壓就像兩條平行的距離為30V的“軌道”一樣限制了運放的輸入輸出信號。運放的軌至軌輸入是指運放的輸入端信號電壓能夠達到電源的兩個軌,并保持不失真,如上例輸入信號電壓可達到+/-15V。運放的輸入電壓范圍可在運放的datasheet中找到。就是共模電壓范圍Vcm(Common-Mode Voltage Range)。如下表即為OPA365的輸入電壓范圍,可見它是典型的軌至軌輸入運放。

一般的BJT和JFET是非軌至軌輸入的運放。如下表所示為OPA827共模輸入電壓范圍為(V-)+3V至(V+)-3V,典型的非軌至軌運放。

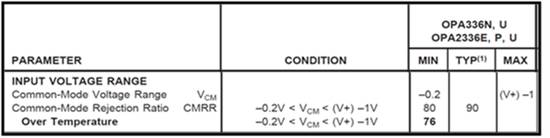

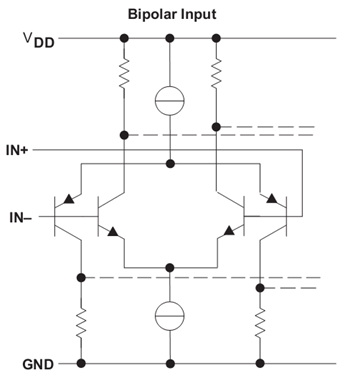

單電源(我們暫且稱之為“單電源”)運放的輸入級通常有三種結構,第一種是采用PMOS做差分輸入級。這樣的運入輸入級電壓可以低于負電源軌0.2甚至0.3V,但達不到正電源軌,如OPA336。下表是datasheet中標出的OPA336輸入電壓范圍。

它的輸入級原理框圖如下圖,典型的PMOS差分輸入級。

既然PMOS差分輸入級輸入電壓不能達到正電源軌,那NMOS呢,對頭,NMOS差分輸入級的輸入電壓可以達到正電源軌,但是達不到負電源軌,一般會在負電源軌的1.2V之上。

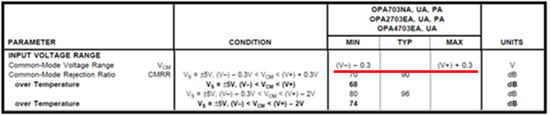

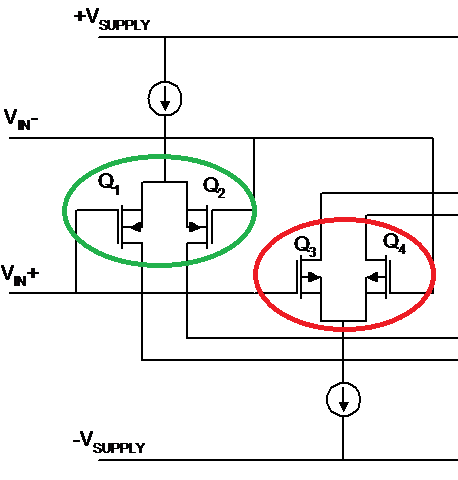

此時有人想到了,把PMOS和NMOS差分輸入級并聯起來。在接近電源負電壓軌時使PMOS差分輸入級工作,在接近電源正電源軌時使NMOS差分輸入級工作。這樣不就可以實現運放的軌至軌輸入了嘛。太巧妙了。的確早先的軌至軌輸入運放就是這樣設計的。并且現在也在大量使用這種技術。如下圖是OPA703的輸入級,就是典型的PMOS與NMOS相并聯的運放輸入級。當輸入共模電壓在(Vss-)-0.3V

下表是OPA703的datasheet中給出的共模電壓輸入范圍(V-)-0.3V至(V+)+0.3V.

Bipolar輸入級運入同樣也有這樣的結構,如下圖是典型PNP與NPN型三級管并聯形成的差分輸入級。

13中講到了常用的軌至軌運放是采用NMOS與PMOS差分輸入級相并聯的方法。這一方法巧妙的解決了輸入信號達不到兩個電源軌的問題。在當今軌至軌輸入的運放中得到廣泛的應用。

但是這種并聯差分輸入級的運放有一個先天的問題就是輸入失調電壓交越問題。如下圖所示,為并聯差分輸入結構的運放的輸入前級。

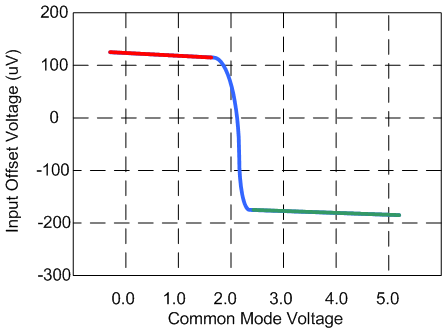

下圖是這種運放的輸入失調電壓可以看出。隨著共模電壓的升高PMOS在2V(用于舉例的值)左右將關閉,而NMOS即將打開,就在這個節骨眼上。運放的輸入失調電壓變生了跳變。這個可以理解,兩組不同結構的輸入級的輸入失調電壓是不同的,在交接棒時,這個失調電壓也完成了交接棒。對于直流信號這個問題會引起誤差突變,對于正弦交流信號,這個問題會引起信號的失真。在交越點引入一個小小的臺階。

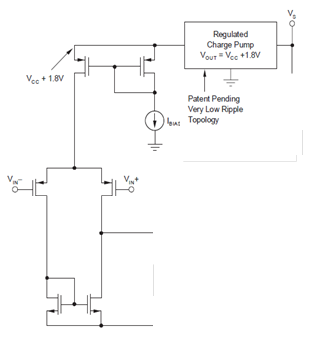

為了解決這個問題,設計了兩種領先的差分輸入級。第一種結構如下圖。PMOS差分輸入級能達到負電源軌,而達不到正電源軌,總是差這么1V左右夠不著。我們把輸入級的電源在內部提高1.8V。水漲船高,這樣的輸入級就能達到運放的正電源軌。由于只有一組差分輸入級,并不會存在輸入失調電壓交越的問題。

這一技術在TI的單電源運放OPAl365上得到應用。如下圖。

到這并沒有結束,另一種技術在TI的單電源軌至軌運放中得到應用。這就是自調零技術。下圖使用了自調零技術(MOSFET Zero Drift)前后。輸入失調電壓跳變就非常小了。

這一技術在TI的OPA333運放中得到應用,下表是OPA333的Vcm輸入電壓范圍。

理想運放的開環增益Aol是無窮大的。這是我們在模電課本上學到的運放的一條基本知識。但現實總是殘酷的,殘酷到所有的運放的開環增益都不是無窮大,它是一個有限值。這個有限制會引起它的一個問題。本文要討論的另一個問題是增益帶寬積,其實更想多說的一點是增益帶寬的那條曲線。

在不具負反饋情況下(開環路狀況下),運算放大器的放大倍數稱為開環增益,簡稱AOL。這句話簡單的定義了運放的開環增益。實際的運放的開環增益,有高有低,并且會隨溫度變化,這是我們不想看到的。

先說說開環增益帶來的不良影響。開環增益為有限值的壞處不只是說明運放都不是理想的。它會帶來一個常被人們忽略的問題——誤差。

下圖是OPAl369的datasheet中給出的關于開環增益的參數,首先映入眼簾(小學作文常用詞)的是開環增最典型值為134dB,最小值為114dB。這說明一點,同一型號的一大批運放,它們各自的開環增益是有一定分布的。

第二項映入眼簾的是運放的開環增益會隨溫度變化而變化。當然是變壞了。在整個運放的使用范圍里最小值可能達到90dB.

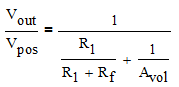

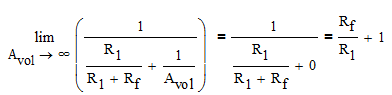

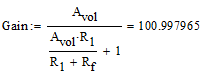

下面我們計算一個Aol對放大電路的影響。如下圖是常見的同相比例放大電路。

如果考慮進Aol,則它的電壓增益為

當假設Avol為無窮大時,則上述放大電路的增益化簡為

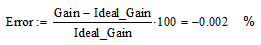

誤差為:

這個結果還不錯差,相當于20ppm的誤差。

如果在寬溫度范圍下應用,最壞情況呢,當Avol在over temperature時為最小值90dB時,增益誤差為下面的計算結果。

Oah, 麥噶敦。千分之三的誤差,對于16位ADC,這相當于200 codes。真是不小的值啊。

因此對于Aol我們可以得出這樣的結論,

(1) 不能輕視它,它確實影響了運放的直流誤差,在以前的part中提到過。

(2) 它是隨溫度變化的,并且在最壞情況下,它帶的誤差可真不小。

(3) 低開環增益的運放不適合高精度的放大。

如bruce 的博客中寫到Aol和offset是表姐妹。把有限開環增益看作是隨輸出電壓變化而變化的失調電壓,可為估計誤差提供一種直觀的方法。如果DC開環增益為100dB,則其相當于1/10^(100dB/20) = 10uV/V。因此,輸出擺動1伏,輸入電壓必須改變10uV。可把它看作是隨DC輸出電壓變化的失調電壓。輸出擺動9伏,其變化為90uV。或許,這種變化對于你的電路來說不足為道,也可能會有影響。

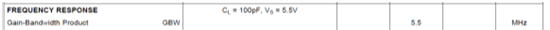

16—增益帶寬積(GBW)對于運放的增益帶寬積,大家再熟悉不過了,這也是我在大學初學運放時,記憶深刻的唯數不多的幾個參數之一。

還是想寫篇貼子對這個參數深刨根一下,(趙大叔小品“往祖墳上刨”)。對于單極點響應,開環增益以6 dB/倍頻程下降。這就是說,如果我們將頻率增加一倍,增益會下降兩倍。相反,如果使頻率減半,則開環增益會增加一倍,結果產生所謂的增益帶寬積。下表就是運放OPA376的datasheet中給出的增益帶寬積典型值5.5MHz。

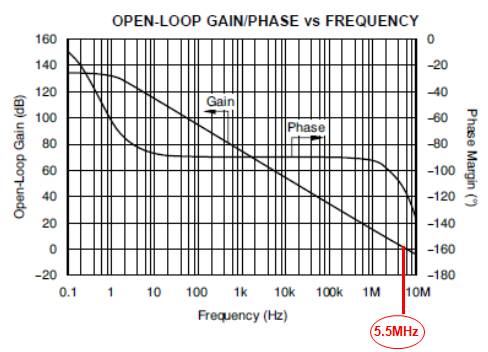

比這個表格中的參數更有用的是運放的開環增益曲線,如下圖是OPA376的datasheet中給出的開環增益曲線.

在一些資料中也常看到運放的單位增益帶寬,它是指運放增益為1時的-3dB帶寬(上圖把它標出來了),它與運放的增益帶寬積從數值上是相等的,雖然名稱不同。下面我們往深處刨一下圖中的曲線,先觀察增益曲線,它在1Hz左右有一個拐點,從這個拐點之后,運放的開環增益開始以-6dB/2倍頻程(或-20dB/十倍頻程)下降。正是由于這個拐點的存在,才使得運放有了增益帶寬。這與理想運放中的開環增益是無窮大是不一樣的。

增益帶寬積的值可是有隱含條件的,就是這個值是在小信號下的帶寬,這個常說的小信號是多小呢,印象中是100mVpp吧。但我們的運放常用來放大大信號,輸出都在幾伏左右。工程師常見的問題就是計算出來的帶寬夠啊,怎么在實際電路中就不夠了呢,原因就在這。因此大信號帶寬還要關注一個參數壓擺率SR。將在以后的貼子中介紹。

小結,增益帶寬積是表示小信號的增益帶寬。大信號另當別論。

17—從開環增益曲線談到運放穩定性

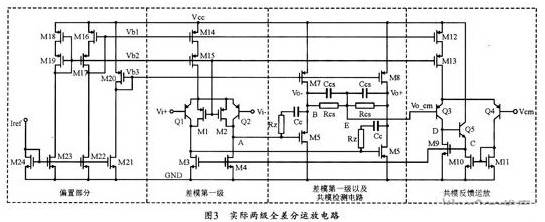

接part16還是先從開環增益曲線談起,開環境曲線為什么在低頻時為什么會有一個拐點呢?這個拐點就是運放的主極點。運放內部的電路中也會有多個極點或零點。這個點就是運放內部(三級也好,兩級也罷)電路的主極點。如果是三級結構的運放,這個極點一般是由第二級的密勒電容來設定的,下圖就是單極點運放的原理圖。

圖中Cc就是設定主極點的電容。下圖是一個兩級他全差分運放的內部電路原理圖,在圖中找找Cc。它就在M5管子上,并且根據密勒效應放大。

為什么要引用Cc來設置運放的主極點呢,而不把運放設計成開環增益是恒定值如130dB,那不更接近于理想運放嘛。最主要原因就是,引放這個主極點補償,可以保證運放的穩定。并且為了穩定,設計工程師會盡量把主極點壓低。最早的鼻祖級運放如uA709就是沒有內部補償的,所以需要外部補償,否則極易產生震蕩。

當然這個極點會引入90度的相移,我們再看一上圖中的相位曲線,在10MHz附近又有一個45度的相移呢。這只能用一個條件來解釋,就是在這附近還有一個極點,只不過這個極點已經在單位增益帶之外了,因此不會引起振蕩。但它也會引入一個問題,使運放的相位裕度變低。再看圖,我們發現在5.5MHz時,相移好像不只是90度,好像是110度左右。這就使得運放的相位裕度變為70度左右了。

再深刨幾句,分析運放的穩定性時總會分析運放的環路增益Aβ,總會聽到這樣的話當Aβ=-1時運放總產生震蕩。也就是環路中相移達到180度。其中A就是開環增益,而β是放大電路的反饋系數,下圖簡單的說明了運放的反饋網絡和β。

從根本上講,就是環路中有兩個極點。不幸的是運放中A中已經有了一個極點,引入了90度 (甚至以上的)相移了。再引入一個90度的相移,就不是困難的了。當然這不是我們想看到的。

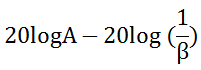

環路增益Aβ可以寫成,A除以在反饋系數的倒數,1/β其實也就是電路的閉環增益:

上式還是不好分析,再把上式寫成對數形式,這對我們就太有用了。

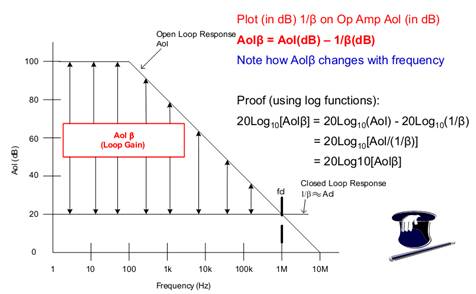

這個式子在波特圖上表示是什么呢,見下圖

咦,眼熟!!對,這張圖來源于資深工程師Tim Green寫的關于運放穩定性的系列文章中的。圖中畫雙箭頭線的區域就是放大電路的環路增益。上面講到環路增益中有兩個極點就會產生振蕩。這在上面的波特圖中的表現是什么呢,就是運放的開環增益A與反饋系數的倒數1/β在波特圖中相交時的合并速度大于等于40dB/十倍頻程(上圖中,只有運放的主極點,因此合并速度為20dB/十倍頻程)。

是什么原因引起了環路增益中產生了兩個極點了,從Aβ中可以看出A已有一個極點了。無非是A再加一個極點,或者β再引入一個極點,就足以讓電路不穩定了。這里作為拋磚引玉。

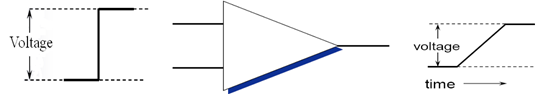

18—壓擺率(SR)我始終覺得運放的壓擺率(SR)是與運放的增益帶寬積GBW同等重要的一個參數。但它卻常常被人們所忽略。說它重要的原因是運入的增益帶寬積GBW是在小信號條件下測試的。而運放處理的信號往往是幅值非常大的信號,這更需要關注運放的壓擺率。

壓擺率可以理解為,當輸入運放一個階躍信號時,運放輸出信號的最大變化速度,如下圖所示

它的數學表達式為:

因此在運放的數據手冊中查到的壓擺率的單位是V/us.下表就是運放datasheet中標出的運放的壓擺率。

我在實驗室里測過OPA333對階躍信號響應的波形如下圖所示。希望能讓大家看的更直觀:

討論完定義和現象,我們來看一下壓擺率SR的來源。先看一下運放的內部結構:

這個圖有點眼熟,是的,運放的SR主要限制在內部第二級的Cc電容上。這個電容同時也決定著運放的帶寬。那運放的壓擺率,主要是由于對第二級的密勒電容充電過程的快慢所決定的。再深究一下,這個電容的大小會影響到運放的壓擺率,同時充電電流的大小也會影響到充電的快慢。這也就解釋了,為什么一般超低功耗的運放壓擺率都不會太高。好比水流流速小,池子又大。只能花更長的時間充滿池子。

下表是一些常用到TI運放的壓擺率和靜態電流:

上面簡單說了一個影響壓擺率SR的因素。下面該說SR對放大電路的影響了。它的直接影響,就是使輸出信號的上升時間或下降時間過慢,從而引起失真。下圖是測試的OPA333增益G=10時波形。由于OPA333的增益帶寬積為350kHz,理論上增益為10的時候的帶寬為35kHz。但下圖是24kHz時測試的結果。顯然輸出波形已經失真,原因就是壓擺率不夠了。帶寬也變成了27kHz左右。

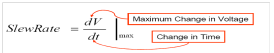

因此這里要引入一個重參數,重要程度堪比增益帶寬積。那就是運放的全功率帶寬。雖然只是一個數學推導。

對于一個輸出為正弦波的信號,輸出電壓可表示為:

Vout = Vp * sin(2*pi*f*t)

這個輸出電壓對時間求導可得:

上式的max是指在求導后的余弦信號在t=0時得到最大值。這個很好理解,也就是說原正弦信號在t=0時壓擺率最大。

可以看出dV/dt表示的壓擺率,跟信號的頻序有關,還與信號的輸出幅值有關。上式中,如果Vp是運放的輸出滿幅值。則上式可表示為

此時FPBW就是運放的滿功率帶寬了。記住它吧,它簡值太重要了。例如如果想在100Khz以內得到正弦波的10Vo-p振幅,按照公式需要轉換速率的是6.3v/us以上的OP。可以看出,滿功率帶寬由壓擺率和輸出信號的幅值決定的。也就是壓擺率一定的情況下,輸出信號的幅值越大,全功率帶寬越小。這也解釋了上面OPA333的測試結果。

這里還要說一個得要的公式,就是運放的上升時間與帶寬的關系。如下式,面熟,這個公式在很多地方都見過。也太重要了,記住它吧。

今天我們深一點分析這個公式的由來。其實它是由一階系統的響應計算而來的。對于一階RC的頻率響應為

一階系統的階躍響應為下式。

Vo=0.1Vm時 t=0.1RC。(-ln0.9 =0.1)當Vo=0.9Vm時,t=2.3RC (-ln0.1=2.3)。則RC階躍 響應的時間為Tr=2.2RC.

而對于一個一階RC的帶寬又可以表示為:BW=1/(2*pi*RC)。上升時間里也有RC,這兩個RC是同一個嘍。這句是廢話。那Tr=2.2/(2*pi* BW)=0.35/BW。

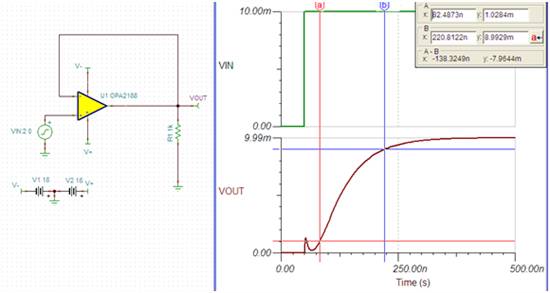

下面我們對這個結論用TINA進行一下仿真。運放為OPA2188,增益帶寬積為2MHz。運放設置為增益為1的同向放大電路。輸入信號為10mV的階躍信號。輸出信號的上升時間為220.8ns-82.5nS=138.3nS.

下面看一下計算結果:計算結果為175nS。約20%的誤差。但也有很好的參考價值了。

20—建立時間(Settling Time)

相信關注運放建立時間的人不是特別多,但是運放的建立時間,對于其后的ADC至關重要。如一個16bits的ADC,它的一個LSB對應的電壓范圍是其滿量程的15ppm, (百萬分之十五) 。如果驅動ADC的運放還沒有達到最終的值就被ADC采樣了。這必然會引起ADC的采樣誤差。

放大器的建立時間是當運輸入為階躍信號時,運放的輸出響應進入并保持在規定誤差帶所需的時間。這個誤差常見的值為0.1%, 0.05%,0.01%。一個杯具的時,誤差大小與建立時間不是線性關系。如誤差0.01%的建立時間可能是誤差0.1%的建立時間的30倍以上。神奇吧。下圖是運放的建立時間的示例說明圖,建立時間,就是從階躍信號開始到信號誤差達到目標值的這段時間。如圖上可以看出,運放運階躍信號的響應會是一個含有過沖和振鈴的二階響應。這個響應看上去很熟悉,像控制系統的二階響應。所以以下的分析與控制系統有相似性。

運放的建立時間,主要有兩段組成,第一段是運放的輸出電壓從起始值到達目標值附近,這一過程是一個非線性過程。這一段的時長是由給運放的補償電容充電的電流所決定的。關于這個補償電壓,在運放的壓擺率中提到過。因此也可以理解為第一段時間與運放的壓擺率有關,(壓擺率的決定因素也是運放補償電容充電的快慢)。第二段時間是指輸出已經接近最終目標值了,進入這一階段后,運放處在準線性區。這一階段的特性,主要受運放的零-極點對(doublets)影響。在高速運放中,運放的slew rate非常高,因此第一段時間非常短,因此建立時間主要由第二段時間所決定。

關于第二段時間,感興趣的可以參閱B.Yeshwant Kamath的經典論文

Relationship Between Frequency Response and Settling Time of Operational Amplifiers

關于建立時間的測量方法,可能需要比較精密的電路,和參數良好的儀器。網上也有經典的文章介紹。感興趣的可以找一下。

Measuring op amp settling time by using sample-and-hold technique

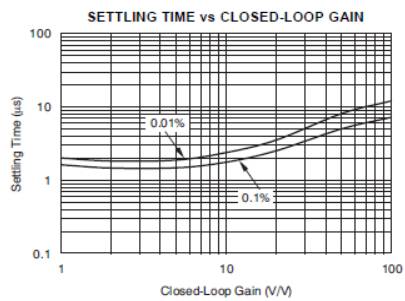

從運放的指標上講,運放的建立時間會受到大信號參數-壓擺率(SR)的影響和小信號參數-閉環增益的影響。下圖是一款運放的建立時間與閉環增益的關系。

通過圖表可以看出,隨著閉環增益增加,建立時間也隨著增加。這是由于高增益時,運放的閉環帶寬會降低,因此調整輸出誤差的環路增益(AolB)也會減小。最終造成放大電路建立時間的增加。

最后再羅嗦一句,對于數據采樣保持電路來說,建立時間是非常重要的。尤其對于ADC的輸入需要通過multiplexer在不同信號間切換的。一定要注意讓信號建立起來后,再進行采樣。否則會引起不可預知的誤差。

21—總諧波失真(THD)這一個part,準備寫寫關于運放的總諧波失真。其實不只是總諧波失真,還有諧波失真,總諧波失真和噪聲(THD+N),都是評價運放在諧波失真方面的重要參數。

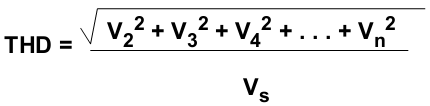

運放的總諧波失真(THD)是當運放的輸入信號為純的正弦波時(這里說純的正弦波是指無諧波的正弦波),運放的輸入信號中的各次諧波(2次,3次,至n次)的均方根值,與輸出號基波的RMS值之比。定義如下式:

其實際測試時,一般只測試前五次諧波(2次到6次)。這是因為諧波的幅值隨著諧波階次的增高而快速降低。六次以上的諧波已經占總諧的比率非常小,相對來說只是毛毛雨啦。因此只測前五次諧波已經充分反應全部的諧波成份了。(當然在有些廠商的ADC中它們會測量到2-9次諧波,這樣的結果會更精確)

運放的總諧波失真加噪聲很好理解,就是上式分母中再加上噪聲RMS值,定義如下式。式中的Vnoise是指可測量帶寬內的噪聲的RMS值。

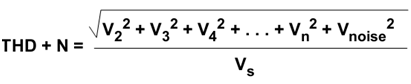

好多廠家的數據手冊中,標示的THD其實代表著THD+N,這是因為大部分測試系統并沒有區分與信號相關的諧波和其它噪聲信號。下表是datasheet中標出的THD+N值:

這里進行一個小小的說明,一般在音頻系統中,THD(或THD+N)一般用百分比表示,如上表中的值,在通信系統中THD+N一般用dB表示。

THD的測量方法,一般是將輸入信號的基波頻率,用窄帶陷波器濾除出去,然后測試其余的信號成分(包括諧波和噪聲)。常用的測量音頻THD的儀器為Audio Precision。

下面再說一個運放的datasheet中常出現的圖表,運放的THD+N是與放大電路的閉環增益相關的。增益越高TND+N越低。這是因為在閉環增益提高時,放大電路的環路增益會隨之降低。使得運放對非線性誤差的糾正能力一降。這就引出了運入出現諧波失真的根本原因,是由于內部器件或多或少的存在非線性效應。

Datasheet中的表格中標出的總諧波失真和噪聲的值是在增益為1的放大電路中測試的。因此它是一個非常好的值,當我們設計的電路放大倍數增大時,看到TND+N惡化現在不用覺得奇怪了。

另外一點時,現在許多的運放都是軌至軌(rail to rail)輸入輸出的,一般都標稱能信號離運放的電源軌只有10mV左右甚至更低。但這會有一個問題,當信號的在接近電源軌時,受非線性效應的響應,信號的TND+N還是會惡化的。因此如果想保持良好的TND+N。盡量不在使運入的輸出信號太接近于電源軌。

22—軌至軌(rail to rail)輸出最近比較忙,把這個主題中斷了,現在利用周末的時間,把這個主題繼續下去。希望本月能把運放基本參數這一主題結貼。并開始新的主題。

今天用一個貼子寫兩個關于運放輸出特性的小主題,一個是Rail-Rail 輸出,另一個是輸入短路電流。

先說軌至軌輸出(rail to rail output)。現在在低電壓運放的中,很多都是軌至軌輸出。運放的軌至軌輸出是由MOS作輸出級設計實現的。早期的運算放大器輸出級是帶有NPN電流源或下拉電阻的NPN射極跟隨器。這種使用BJT的互補共射極輸出級無法完全擺動到電源軌,只能擺動到電源軌的晶體管飽和電壓CESAT范圍內。對于較小的負載電流(小于100 μA ),飽和電壓可能低至5至10 mV;但是,對于較高負載電流,飽和電壓可能增加至數百毫伏

軌至軌輸出的本意是指,運放的輸出電壓可以達到電源軌。但實際是它是十分接近電源軌。只說這么一個定義是沒有多大意義的。下面要說一下這里關于軌至軌輸出的一些需要注意的問題。

先看下圖,是OPA376的datasheet上的數據。看到在不同負載下的輸出離電源軌的電壓值是不同的。

這是由于采用CMOS FET構建的輸出級(如下圖)可以提供近乎真正軌到軌的性能,但只是在空載條件下。如果運算放大器輸出必須流出或吸入相當大的電流,則輸出電壓擺幅會降低,降幅為FET 內部導通電阻上的I×R 壓降。一般而言,精密放大器的導通電阻在100 Ω 左右,但高電流驅動CMOS 放大器的導通電阻可能小于10 Ω。這就是引起輸入不能完全達到電源軌的根本原因。

另一方面,運放的輸出信號到軌的電壓值,隨溫度而變化。這同樣可以在OPA376的datasheet中的表格中看到,并且在全溫范圍內,一般會出現在高溫的情況,輸出信號到軌的電壓值會變大。這是由于MOS導通電阻,具有正溫度系數,溫度越高,導通電阻越大。這也就是造成了全溫范圍內壓差VSAT= VS– VOUT會變大。

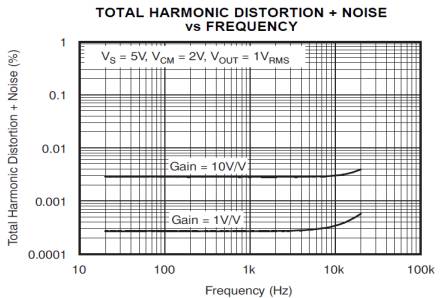

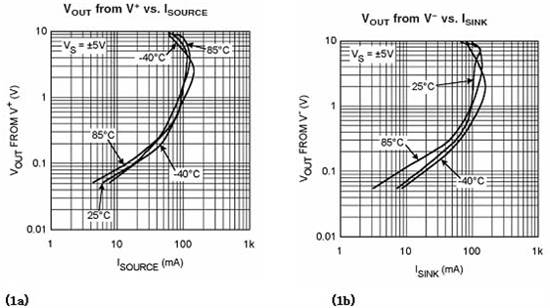

下面引出一張圖表,這張圖表在運放的datasheet中非常常見,但也經常被忽略,它反應了一個重要結論:隨著溫度的上升,和輸出電流的上升,運放輸出信號與電源軌的壓差VSAT= VS– VOUT也隨之增大。原因正如上面所解釋的。當然還有一個問題,當輸出電壓越接近電源軌時,信號的失真會變的差一點。因此沒有真正能達到電源軌輸出的運放。根據上面的原因,離電源軌遠一點,更容易達到高的信號質量。

運放的輸出短路電流是用來表明運放輸出級輸入或灌入電流的能力,這一指標表明了運放的驅動能力。一般的運放最大輸出短路電流在幾十個mA的水平,看上去不算很小。但在一些情況下也會引起問題,因此本貼花點時間來寫一下這個問題。

下圖是OPA376的輸出短路電流,看得出源電流和灌電流是不同的,一個是30mA,另一個是50mA.

運放的輸出短路電流在反映一個重要的性能,就是驅動負載的能力,尤其是當輸出信號幅值比較大時,負載電阻較小時,如一個輸入20Vpp的正弦波信號,加在一個100ohm上時,則加在負載上的電流有有效值為7.07V/100ohm=70.7mA。

另一種的確定電流驅動能力的方法,是使用輸出電流和輸出電壓圖。圖1顯示LMH6642的輸出電流和輸出電壓圖。對于大多數器件,通常會對源電流(圖2a)和阱電流(圖2b)這兩種情況分別給出一張圖。

圖2:LMH6642的輸出特征

圖2:LMH6642的輸出特征

運用這種圖,就能夠估算出對于給定的輸出擺幅運放所能提供的電流。這些圖由芯片廠商,用來顯示放大器的輸出電流能力與輸出電壓之間的關系。

請注意,在圖2中,描述了"來自V+的Vout"與輸出源電流的關系,以及"來自V-的Vout"與輸出阱電流的關系。用這種方法來表示數據的原因之一是,和輸出電壓相對于地的表示方法相比,它能被更容易地應用于單電源或雙電源操作。另一個原因是由于電壓余量比總的電源電壓對于輸出電流的影響要大得多,因此對于任意的電源電壓,即使在數據手冊上找不到精確對應的條件,這種數據手冊方法也能使設計者通過一組最接近的曲線來進行粗略的計算。

圖中能夠用來預測一個給定負載上的電壓擺幅。如果坐標軸是線性的,設計者只需要在圖中的特征曲線上加上一條負載曲線,通過這兩條曲線的交點就能確定電壓擺幅。

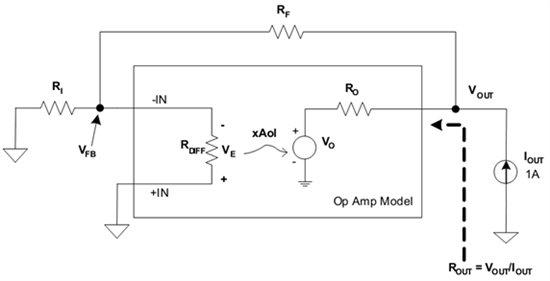

24—輸出阻抗Ro和Rout本文的標題有此讓人迷惑,運放的輸出阻抗怎么會有兩個呢,它們有啥區別呢。下面先來說一下他們的定義,從定義中可以看出它們的區別。Ro定義為運放的開環輸出阻抗。Rout定義為運放的閉環輸出阻抗。定義看上去很明確但理解起來還是不夠直觀。看下面的圖,Ro是由運放內部輸出級決定的,不隨閉環增益的變化而變化。可以理解為運放的本征參數。

而Rout則不同,它是運放構成環閉放大電路后,從輸出端看進去的阻抗,需要在輸出端進行測量才能得到。當然它會隨著閉環增益變化而變化。

講完定義,下面講一下它們倆的關系,公式很簡單:

具體推導過程,在Tim Green的經典應用文檔集“運算放大器的穩定性”第三篇,有詳細的推導過程,這里不見重復了。(此處省略兩百字,呵呵)。

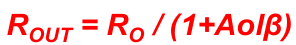

下面著重分析一下,Ro對放大電路的影響,通過分析,我們可以看到Ro的危害,并在進行放大電路設計時,關注到所選用的運放的Ro值。

由于Ro的存在,并且不像理解運放中的為零,運放在驅動容性負載時,就會出問題了。主要問題是Ro和負載電容相互作用給放電大路的環路增益引入一個極點,下面就是上面電路中Ro和負載電容引入的極點的計算結果。這個極點的拐點頻率為5.545KHz。好低哦。

fpo1 = 1/(2?П?RO?CL)

fpo1 = 1/(2?П?28.7??1μF)

fpo1 = 5.545kHz

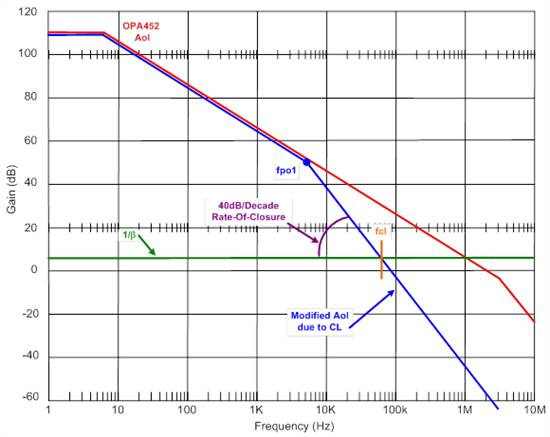

引入這個極點又會發生什么呢?它會使放大電路不穩定,看下面的圖,它將環路增益畫成了波特圖進行分析,關于這一分析方法在Tim Green的經典應用文檔集“運算放大器的穩定性”中有詳細介紹。

可見引入的這一新的極點Fpo1使得運放的開環益在Fpo1以后以40dB/dec的速度滾降。它反饋系數倒數的直線時在相交點fcl時閉合速度為40dB/dec。這足以使放大電路不穩定了。(注:放大電路穩定性的判據為開環增益Aol曲線與反饋系數的倒數曲線在相交點fcl處的閉合速度為20dB/dec則放大電路穩定)

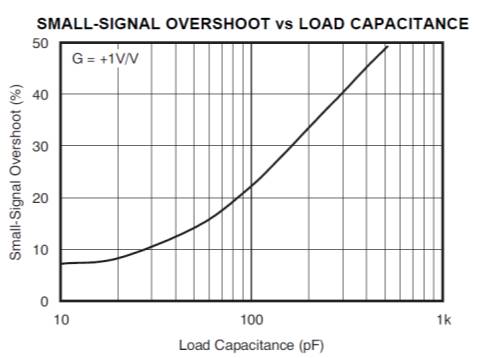

即使放大電路沒有發生震蕩,它也會使得放大電路對方波響應時有一個過沖。如下圖,是在不同負載電路下小信號過沖的曲線。從曲線中可以看出,500pF的負載電路可以使放大電路過沖達50%。這個曲線很重要哦,在很多運放的datasheet中會給出。

關于運放datasheet中未給出Ro的值時,請參照Tim Green的應用文檔集“運算放大器的穩定性”第三篇。文章有詳細換算過程,節省時間,就不附上了。

25—運放的熱阻又忙了一段時間,今天終于抽出點時間把運放參數的詳細解釋系列博客寫完了。最后一小節還是寫點,非常重要而極易被人忽略的問題——運放的熱阻。

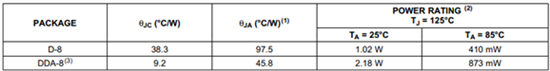

在運放的datasheet中經常見到如下表所示的參數:來自THS3091的datasheet.

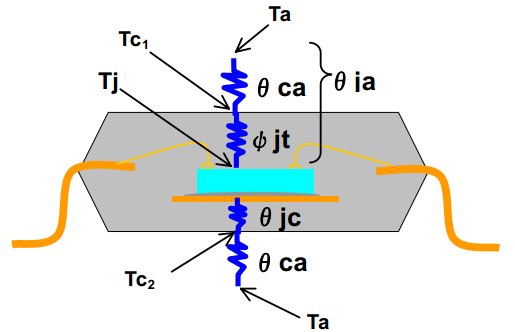

經常看到兩個參數,但又常被人忽略。下面先解釋什么叫熱阻。半導體封裝的熱阻是指器件在消耗了1[W]功率時以產生的元件和封裝表面或者周圍的溫度差。這聽起來有點難理解,看下面的圖,和公式。

TJ= PD( RθJA) + TA

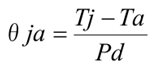

公式看上去有些難理解,一點一點解釋。TA是指芯片的環境溫度。Tj是指芯片的結溫,也是指芯片內部Die的溫度。這兩者之間的溫度差只與芯片的功耗和熱阻有關,那通過上面的公式,可以計算出熱阻的定義公式:

上面的定義可以知道熱阻的單位,是 溫度/功耗。 這也就是上面第一個表格中看到的熱阻單位。

上面說完了熱阻的定義,下面就說說常見到的兩個熱阻參數。第一個是θJC,這個是表示,芯片內部結溫junction和芯片封裝外殼case之間的熱阻, 這個值一般相對比較小。別一個是θJA,這個是表示芯片結溫junction與芯片ambient的環境之間的熱阻,這個熱阻一般要比θJC大一些。這是由于芯片的外殼向周圍環境散熱要難一些。因此我們在實驗室的室溫環境下,去摸高功耗的芯片外殼還是很熱。

關于運放的熱阻聽了上面的一大堆理論后,看下面的圖,畫的非常清淅,θCA也有清淅的示意。

上面講了很多理論,最后說一點熱設計的注意事項。當芯片的工作電流非常大時,芯片的封裝熱阻比較大時,就要注意散熱設計了。如THS3091用+/-15V供電工作在高頻時,輸出信號幅度又大時,電流可以達到50mA之上。此時芯片的功耗為1.5W以上。采用無散熱pad的芯片時,溫升會非常高。芯片的datasheet上的熱阻是在JEDEC標準定義的板子上測試的。一般實際的電路板散熱可能沒有那么好,

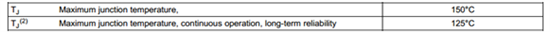

芯片datasheet上一般給出最高結溫為150°C。但長時間工作的芯片,結溫不能超過125°C。下面是THS 3091的datasheet中給出的最大結溫參數。

本系列至此完。

原文標題:運放參數的詳細解釋和分析-合集(1-25)

文章出處:【微信號:fcsde-sh,微信公眾號:fcsde-sh】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

快速了解運放的輸入偏置電流Ib和輸入失調電流Ib_os參數

運放的靜態參數輸入偏置電流Ib和輸入失調電流及溫度漂移

輸入偏置電流和輸入失調電流(運放參數的詳細解釋和分析)

運放參數的詳細解釋和分析:輸入偏置電流和輸入失調電流

運放的輸入失調電壓電流怎么計算

偏置電流ib失調電流ios這些運放概念全懂了沒?

偏置電流ib失調電流ios這些運放概念全懂了沒?

評論