AMD Versal AI Core 系列和 Versal AI Edge 系列旨在憑借 AI 引擎機器學習 ( ML ) 架構來提供突破性的 AI 推斷加速。這些器件的設計應用范圍廣泛,包括用于云端動態(tài)工作負載以及超高帶寬網絡,同時還可提供高級安全性功能。AI 和數據科學家以及軟硬件開發(fā)者均可充分利用高計算密度的優(yōu)勢來加速提升任何應用的性能。AI 引擎機器學習擁有先進的張量計算能力,非常適合用于高度優(yōu)化的 AI 和 ML 應用。

AI 引擎機器學習器件包含二維陣列,由帶有單指令流多數據流 ( SIMD ) 矢量單元的超長指令字 ( VLIW ) 處理器構成,專為計算密集型應用而高度優(yōu)化,特別適用于機器學習 ( ML ) 等 AI 技術。

AI 引擎機器學習陣列支持三種級別并行度:

| 指令級并行度 ( ILP ):通過 VLIW 架構,允許在單個時鐘周期內執(zhí)行多次運算。 | |

| SIMD:通過矢量寄存器,允許并行執(zhí)行多項計算。 | |

| 多核:通過 AI 引擎機器學習陣列,支持并行執(zhí)行多個 AI 引擎機器學習核。 |

指令級并行度包括 1 次標量操作、1 次移動、2 次矢量讀取(加載)、1 次矢量寫入(存儲)和 1 條可執(zhí)行的矢量指令,總計每個時鐘周期達 6 路 VLIW 指令。數據級并行度是通過矢量級操作來實現的,其中每個時鐘周期可執(zhí)行多組數據操作。

每個 AI 引擎機器學習都包含矢量處理器和標量處理器、專用程序存儲器、本地 64 KB 數據存儲器、支持訪問其本身和三個相鄰 AI 引擎機器學習內的本地存儲器。它還可訪問 DMA 引擎和 AXI4 互連開關,以通過串流來與其他 AI 引擎機器學習進行通信或者與可編程邏輯 ( PL ) 或 DMA 進行通信。請參閱《Versal 自適應 SoC AIE ML 架構手冊》 ( AM020 ) 以獲取有關 AI 引擎機器學習陣列和接口的具體詳細信息。

雖然對于 AI 引擎機器學習而言,大部分標準 C 語言代碼均可編譯,但代碼可能需要重構才能充分利用硬件所提供的并行度。AI 引擎機器學習的優(yōu)勢在于,它能夠在每個時鐘周期內使用 2 個矢量執(zhí)行乘積累加 ( MAC ) 運算、為下一項運算加載 2 個矢量、存儲來自上一項運算的單個矢量,并遞增一個指針或執(zhí)行另一次標量運算。稱為本征函數的專用函數允許您以 AI 引擎機器學習矢量處理器和標量處理器為目標,并提供多個常用矢量函數和標量函數的實現,使您能夠專注于處理目標算法。AI 引擎機器學習不僅包含其矢量單元,還包含一個標量單元用于所有標準 C 語言代碼程序。

AI 引擎機器學習程序使用以 C++ 編寫的數據流計算圖(自適應數據流計算圖)規(guī)格。此規(guī)范可使用 AI 引擎編譯器進行編譯并執(zhí)行。自適應數據流 ( ADF ) 計算圖應用由多個節(jié)點和邊緣組成,其中節(jié)點表示計算內核函數,邊緣則表示數據連接。應用中的內核可編譯為在 AI 引擎機器學習上運行,這些內核構成了 ADF 計算圖規(guī)范的基礎構建塊。ADF 計算圖屬于 Kahn 進程網絡,其中包含并行運行的 AI 引擎內核。AI 引擎內核在數據串流和緩沖器上執(zhí)行運算。這些內核會耗用輸入數據塊并生成輸出數據塊。內核還可包含靜態(tài)數據或運行時參數 ( RTP ) 實參,包括異步實參或同步實參。

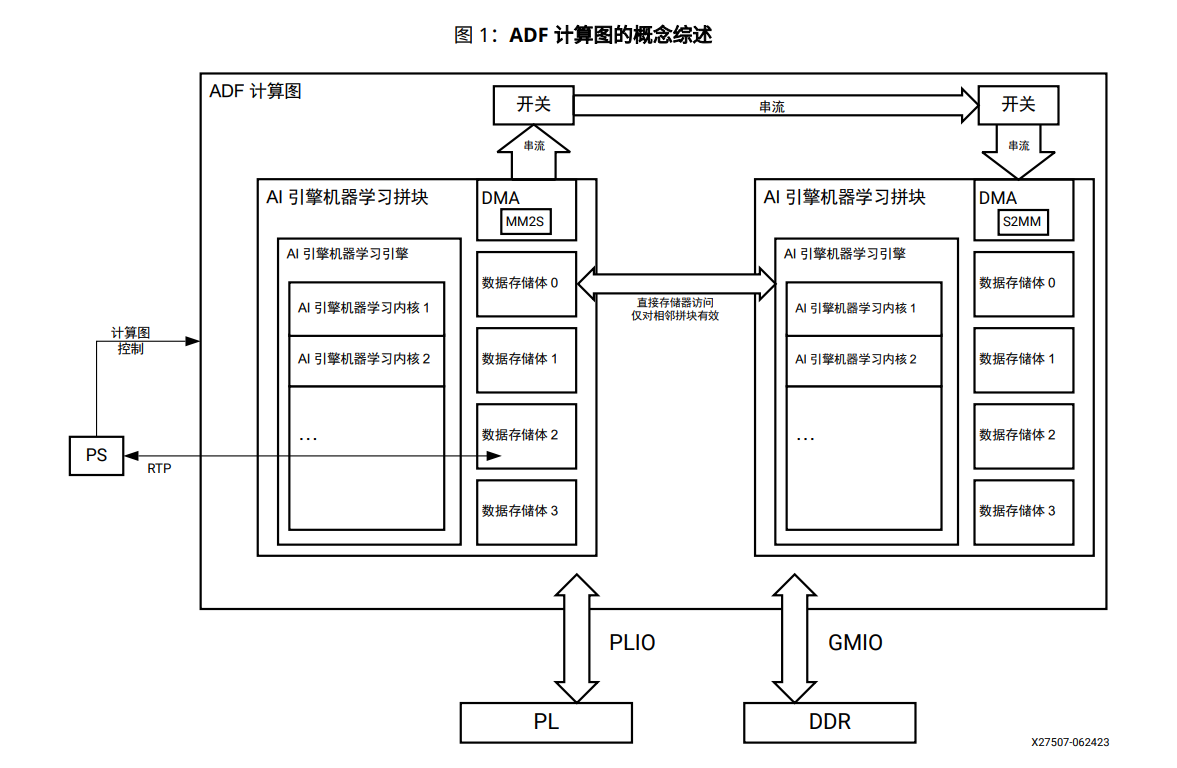

下圖顯示

ADF 計算圖的概念視圖及其與處理器系統 ( PS )、可編程邏輯 ( PL ) 和 DDR 存儲器的對接接口。它包括:

AI 引擎機器學習:每個 AI 引擎機器學習都是一個 VLIW 處理器,其中包含一個標量單元、一個矢量單元、兩個加載單元和一個存儲單元。

AI 引擎內核:內核是以 AI 引擎機器學習中運行的 C/C++ 編寫的。

ADF 計算圖:ADF 計算圖是具有單個或多個 AI 引擎內核(以數據串流和/或緩沖器連接)的 Kahn 進程網絡。它憑借如下特定構造來與 PL、全局存儲器和 PS 進行交互,此類構造有:PLIO(計算圖中的端口屬性,用于建立往來可編程邏輯的串流連接)、GMIO(計算圖中的端口屬性,用于建立往來全局存儲器的外部存儲器映射連接)和 RTP。

如需了解有關 AI 引擎機器學習存儲器拼塊訪問的信息,請參閱 AI 引擎機器學習存儲器拼塊訪問。如需了解有關 AI 引擎機器學習外部存儲器訪問的信息,請參閱 AI 引擎機器學習外部存儲器訪問。

本文檔第 2 章到第 5 章聚焦 AI 引擎內核編程,不僅涉及單內核編程,還涵蓋了多方面的內容,如內核之間的數據通信,這些內容都是將應用分區(qū)為多個內核以達成所需的吞吐量所必不可少的概念。

本文檔第 6 到 14 章焦點包括 AI 引擎計算圖編程構造、內核之間的數據通信類型、通過主機應用來控制 AI 引擎計算圖以及高級計算圖編程構造。

-

處理器

+關注

關注

68文章

19900瀏覽量

235456 -

AI

+關注

關注

88文章

35210瀏覽量

280346 -

機器學習

+關注

關注

66文章

8505瀏覽量

134678

原文標題:AI 引擎機器學習內核與計算圖編程指南

文章出處:【微信號:賽靈思,微信公眾號:Xilinx賽靈思官微】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

信而泰×DeepSeek:AI推理引擎驅動網絡智能診斷邁向 “自愈”時代

Firefly支持AI引擎Tengine,性能提升,輕松搭建AI計算框架

【AI學習】AI概論:(Part-A)與AI智慧交流

AI概論: <TensorFlow + Excel>可操作教案(Part-C:AI(機器)是如何學習呢?)

最值得學習的機器學習編程語言

AI+機器學習:推動AI應用產業(yè)化,加快機器學習步伐

賽靈思AI引擎簡介

火山引擎機器學習平臺與NVIDIA加深合作

AI引擎架構和陣列編程要求

Versal ACAP AI引擎編程環(huán)境用戶指南

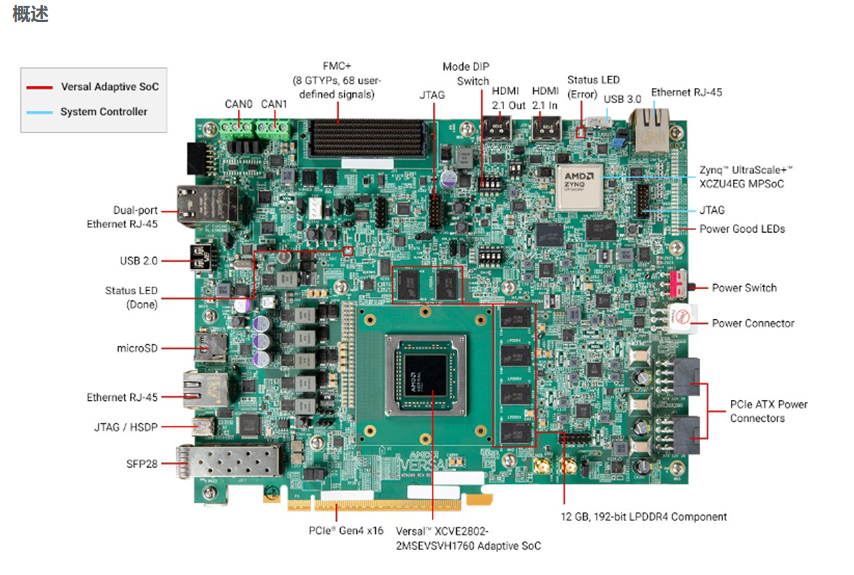

面向AI與機器學習應用的開發(fā)平臺 AMD/Xilinx Versal? AI Edge VEK280

評論