簡介

本文參考設(shè)計基于 AMD ZYNQ7000 Device, 使用 VDMA 做原始圖像采集系統(tǒng),在 Petalinux 下做服務(wù)器,通過 Socket 發(fā)送圖像至 Windows 或者 Linux 上位機(jī)。

作為驗證,可以連接 CMOS,或者使用 AXI TPG 生成仿真的圖像數(shù)據(jù)。

教程中所有涉及的設(shè)計及代碼均在 Windows 和 Linux 平臺下作了驗證。

系統(tǒng)設(shè)計

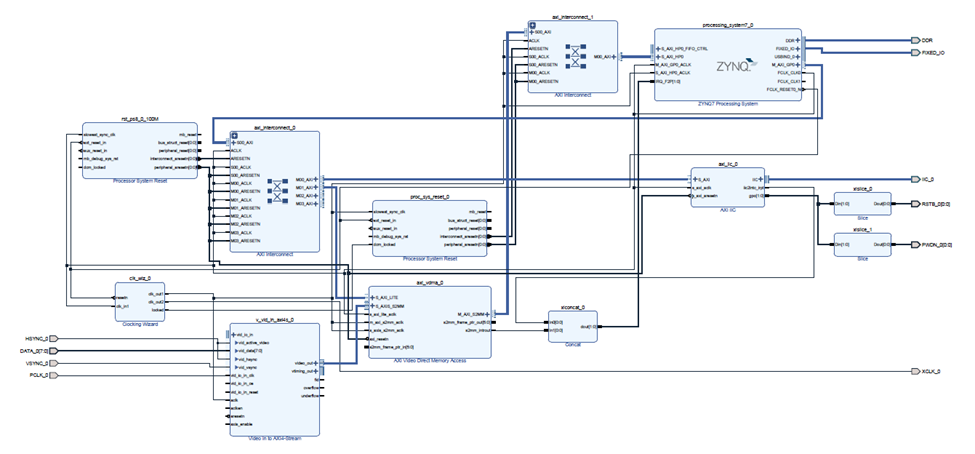

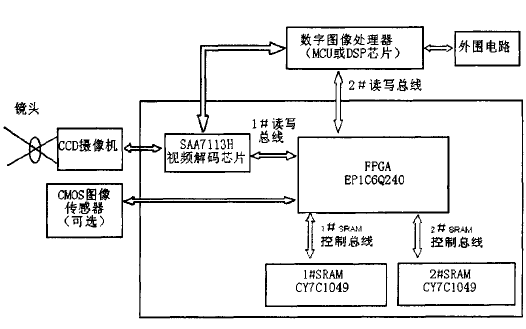

1. 系統(tǒng)設(shè)計框圖參考如下:

a. 通過 Video In to AXI4-Stream 將 CMOS 輸出的 VSYNC,HSYNC 以及數(shù)據(jù)信號轉(zhuǎn)換成視頻流。注意 CMOS 的輸入時鐘 PCLK 與 AXI4-Stream 工作在不同的頻率。

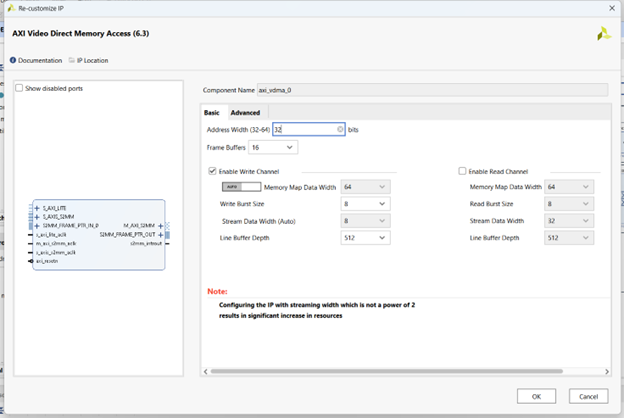

b. 緊跟其后面實(shí)例化了一個 AXI VDMA,用于接收輸出的視頻流。AXI VDMA 通過其 M_AXI_S2MM 端口連接至 AMD ZYNQ7000 Device 的 HP0 端口,以訪問 PS 側(cè)的 DDR 控制器,用作 VDMA 的 Frame Buffer。

由于圖像在傳輸過程中可以會出現(xiàn)當(dāng)前的 Frame Buffer 被 VDMA 再次寫入的情況,所以我們將 Frame Buffer 數(shù)量調(diào)至16,以減小 圖像被污染的概率。如果想完全解決這個問題,需要配置 VDMA 的 GenLock 使用,我們會在之后的設(shè)計的講解。

c. 系統(tǒng)還實(shí)例化了一個 AXI IIC 控制器,用于初始化 CMOS 的寄存器,使其能夠正確的工作在期望的頻率。也可選用 PS 側(cè)的 IIC 控制器。

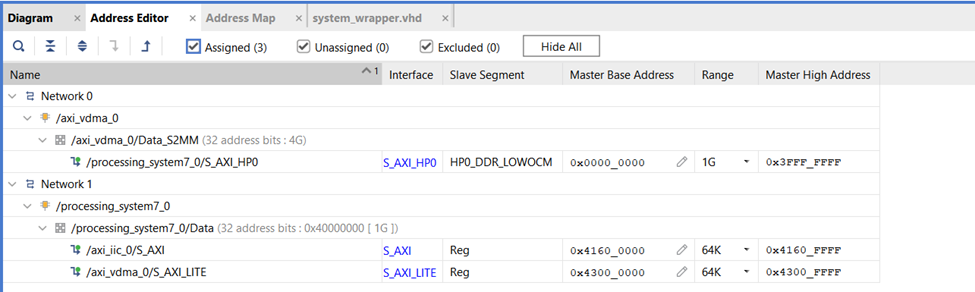

2. BD 中需要分配各個 IP 地址如下,可以用 AMD Vivado Design Suite的自動地址分配工具完成。

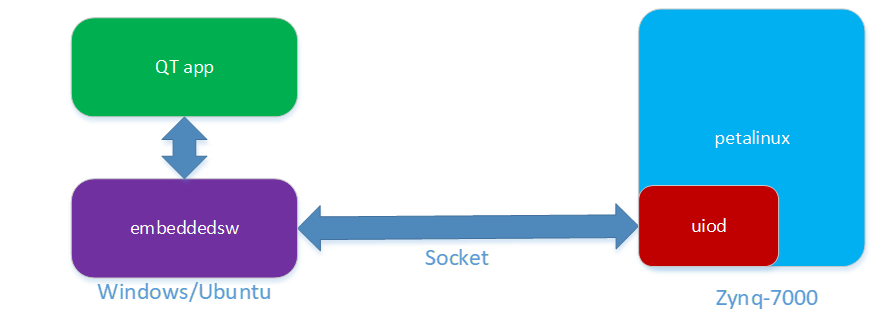

軟件架構(gòu)

系統(tǒng)框圖

開發(fā)板上運(yùn)行 Petalinux,用作視頻的服務(wù)器。在 Windows/Ubuntu 上位機(jī)位移植 Embeddedsw,并通過 Socket 配置 CMOS 和接收圖像。最后把圖像通過 QT 顯示。

環(huán)境需求

硬件環(huán)境

AMD ZYNQ7000 Device

OV5640 或者 AXI TPG仿真

Windows10/11 或者 Ubuntu20.04 主機(jī)

軟件環(huán)境

AMD Vivado Design Suite 2022.2

Petalinux 2022.2

CMake > 2.15

OpenCV3.3.1

QT5.15.2

Windows + Visual Studio 或者 Linux + GCC

代碼結(jié)構(gòu)

硬件

HW 文件夾里面里面包含 AMD Vivado Design Suite工程,直接用 AMD VivadoDesign Suite2022.2 打開。

打開后綜合實(shí)現(xiàn),并生成 Bitfile。

固件

此參考設(shè)計用 Petalinux 制作系統(tǒng)啟動鏡像,完整的 Petalinux 工程位于 FW 目錄下。

執(zhí)行 petalinux-build 可以編譯。

執(zhí)行 petalinux-package –boot –u-boot –force –fpga XXX.bit 生成 BOOT.BIN文件

軟件

axi vdma 和 axi iic 的驅(qū)動軟件移植自 embeddedsw,主要的改動包括修改 xil_io.c 和 xil_mem.c 文件,用 Socket 的驅(qū)動替換默認(rèn)的 Xil_In32 和 Xil_Out32 的實(shí)現(xiàn),以及內(nèi)存讀寫的功能。

軟件支持 Windows 和 Linux 的主機(jī),采用 Cmake 環(huán)境。如果在 Windows 下,可以選擇 Visual Studio 作為編譯工具。編譯過程如下:

1.cd sw

2.mkdir build

3.cmake .. && make

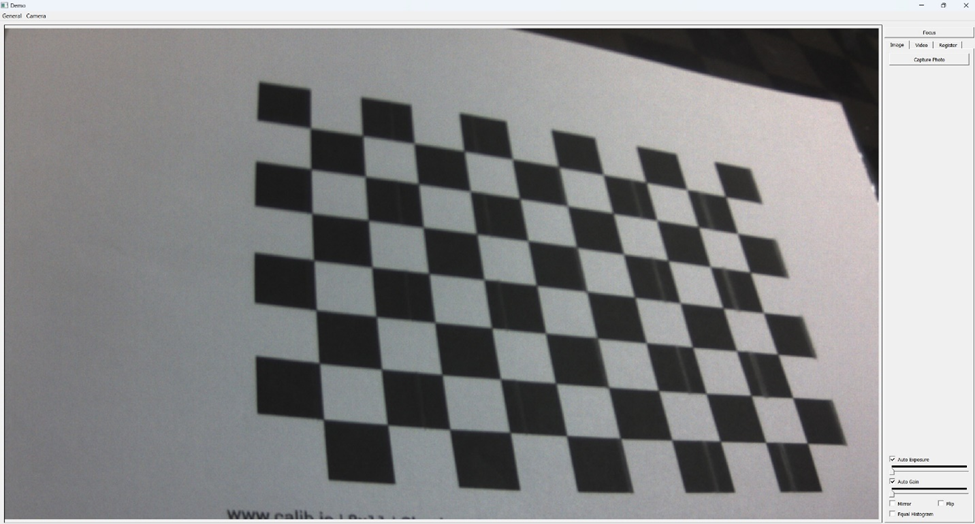

測試結(jié)果

在 Petalinux 下生成的 BOOT.BIN 文件放成 SD 卡,啟動開發(fā)板。

運(yùn)行 QT應(yīng)用程序,可以看到圖像可以被正確的采集。

-

amd

+關(guān)注

關(guān)注

25文章

5546瀏覽量

135690 -

Xilinx

+關(guān)注

關(guān)注

73文章

2179瀏覽量

124045 -

服務(wù)器

+關(guān)注

關(guān)注

12文章

9626瀏覽量

87091 -

圖像采集系統(tǒng)

+關(guān)注

關(guān)注

0文章

28瀏覽量

12596 -

vdma

+關(guān)注

關(guān)注

0文章

6瀏覽量

2851

原文標(biāo)題:開發(fā)者分享|基于 VDMA 的遠(yuǎn)程圖像采集系統(tǒng)參考設(shè)計

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發(fā)者社區(qū)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

基于嵌入式微控制器LPC2214的遠(yuǎn)程圖像監(jiān)控系統(tǒng)

基于GPRS遠(yuǎn)程數(shù)據(jù)采集系統(tǒng)設(shè)計

遠(yuǎn)程系統(tǒng)采集圖像沒法保存到電腦,請問怎么回事?

如何設(shè)計遠(yuǎn)程圖像無線監(jiān)控系統(tǒng)?

嵌入式系統(tǒng)采集圖像數(shù)據(jù)的遠(yuǎn)程測量有什么優(yōu)點(diǎn)?

基于ARM技術(shù)的遠(yuǎn)程圖像監(jiān)控系統(tǒng)設(shè)計

基于CMOS圖像傳感器的USB接口圖像采集系統(tǒng)設(shè)計

基于FPGA的遠(yuǎn)程圖像采集系統(tǒng)設(shè)計

基于FPGA的遠(yuǎn)程圖像與溫度采集監(jiān)控系統(tǒng)

傳感器驅(qū)動下遠(yuǎn)程圖像采集系統(tǒng)設(shè)計_陳德裕

基于STM32F407的圖像遠(yuǎn)程采集終端

如何使用FPGA實(shí)現(xiàn)圖像采集系統(tǒng)的詳細(xì)設(shè)計資料免費(fèi)下載

如何使用FPGA實(shí)現(xiàn)高速圖像采集系統(tǒng)的設(shè)計

評論