本系列所有演示實驗均出自由東南大學湯勇明教授、張圣清教授與Xilinx大學計劃經理陸佳華先生所編著的教材《搭建你的數字積木·數字電路與邏輯設計(Verilog HDL&Vivado版)》。此教材為教育部Xilinx公司產學合作專業綜合改革重點支持項目,并作為Xilinx公司大學計劃指定教材。

本書系統論述了數字電路與邏輯設計的理論、方法與實踐技術。全書基于Verilog HDL與Vivado開發環境,共18章,詳盡介紹了如下內容: 邏輯設計與Vivado基礎、布爾代數與Verilog HDL基礎、組合邏輯電路設計基礎、時序邏輯電路設計基礎、有限狀態機設計基礎、邏輯設計工程技術基礎、Vivado數字積木流程、串行通信接口控制器、RAM接口控制器、字符點陣顯示模塊接口控制器、VGA接口控制器、數字圖像采集、數字邏輯系統設計案例、單周期CPU設計案例、數字信號處理設計案例(FIR)、數字圖像處理設計案例、大學生FPGA設計案例以及Xilinx資源導讀。

為便于教師和廣大讀者學習與動手實踐,本書配套提供了教學課件、教學視頻及程序代碼等教學資源。本書適合作為普通高等院校電子信息類、電氣信息類、自動化類專業的本科生教材,也可作為相關專業研究生參考教材,并適合作為電子與電氣工程技術領域的科研工程技術人員的參考用書。

實驗步驟實驗內容:本實驗通過verilog代碼的編寫,在EGO1開發板上實現OLED的驅動和內容顯示。

實驗原理:本實驗的驅動芯片為SSD1603 OLED驅動控制器,引腳功能如下圖所示:

|

名 稱 |

功 能 |

|

VCC |

|

|

D0 |

SCL,SPI的時鐘 |

|

D1 |

SDA,SPI的數據 |

|

D/C |

數據/指令標志 |

|

RST |

復位 |

芯片可以使用SPI模式或者8080并行模式傳輸數據,這里使用四線SPI模式。其中D/C引腳用來表示傳輸的是的數據還是指令,D/C為高電平時,表示傳輸的是數據,D/C為低電平時,表示傳輸的是指令。

SSD1603數據和指令傳輸時序圖如下所示:

功能實現:通過本實驗,可以將OLED屏幕點亮并顯示所需內容。

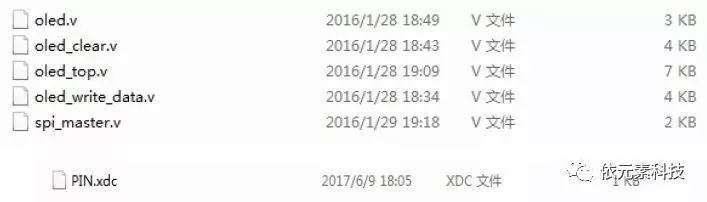

代碼說明:本實驗有5個verilog文件,其中oled_top.v為頂層文件,其余為底層文件,PIN.xdc為本實驗的管腳約束文件。

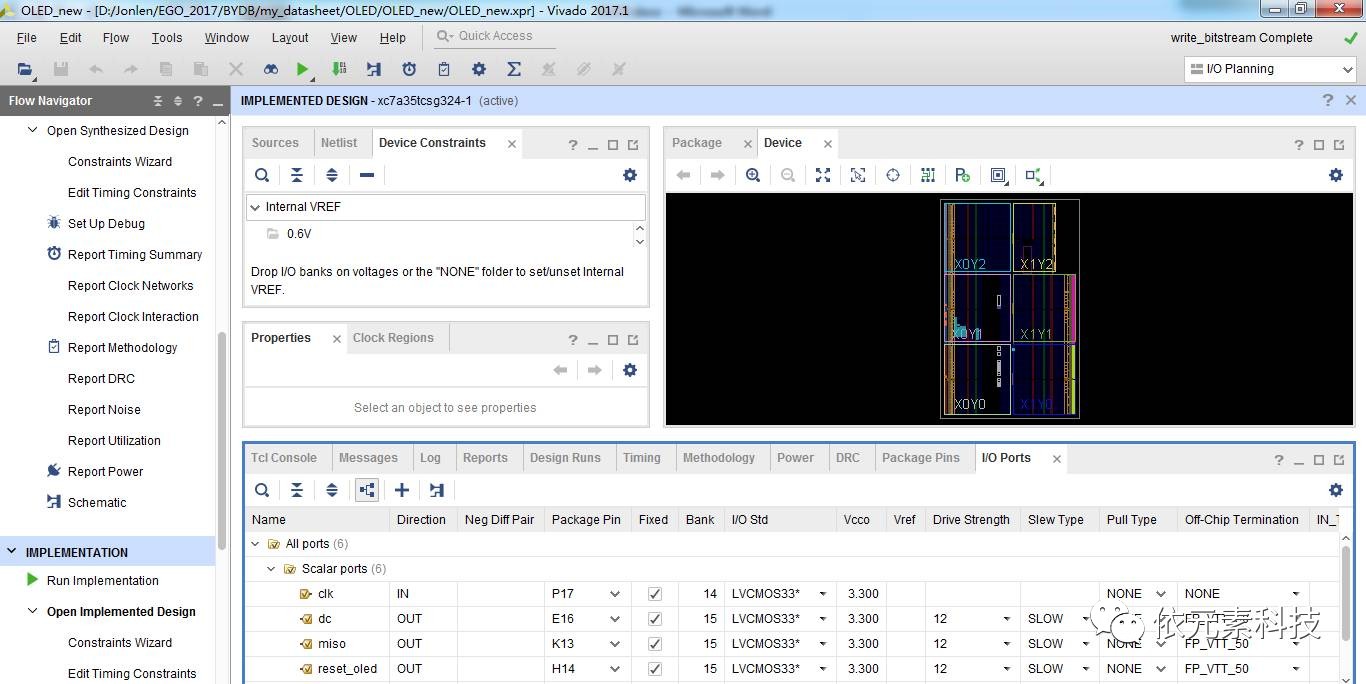

本實驗使用Vivado 2017.1 進行開發,開發界面如下。如果您未安裝vivado,安裝流程請點擊這里。

實驗RTL視圖:

代碼綜合結果:

代碼實現結果:

具體vivado步驟請參看之前的微信文章,文章鏈接請點擊這里。

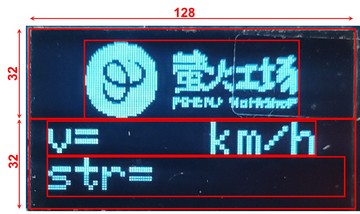

驗效果圖 :

-

OLED

+關注

關注

119文章

6198瀏覽量

224104 -

Verilog

+關注

關注

28文章

1351瀏覽量

110077 -

OLED驅動

+關注

關注

1文章

13瀏覽量

10221

原文標題:【玩轉EGO1系列教程一】:在EGO1開發板上實現OLED控制器

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

通過編寫verilog代碼實現OLED驅動和內容顯示的解決方案

通過編寫verilog代碼實現OLED驅動和內容顯示的解決方案

評論