為什么需要接口?

(1)解決主機CPU和外圍設備之間的時序配合和通信聯絡問題

主機的CPU是高速處理器件,比如8086-1的主頻為10MHz,1個時鐘周期僅為100ns,一個最基本的總線周期為400ns。而外圍設備的工作速度比CPU的速度慢得多。如常規外圍設備中的電傳打字機傳送信息的速度是毫秒級;工業控制設備中的爐溫控制采樣周期是秒級。為保證CPU的工作效率并適應各種外圍設備的速度配合要求,應在CPU和外圍設備間增設一個I/O接口電路,滿足兩個不同速度系統的異步通信聯絡。

I/O接口電路為完成時序配合和通信聯絡功能,通常都設有數據鎖存器、緩沖器、狀態寄存器以及中斷控制電路等。通過接口電路,CPU通常采用查詢或中斷控制方式為慢速外圍設備提供服務,就可保證CPU和外圍設備間異步而協調的工作,既滿足了外圍設備的要求,又提高了CPU的利用率。

(2)解決CPU和外圍設備之間的數據格式轉換和匹配問題

CPU是按并行處理設計的高速處理器件,即CPU只能讀入和輸出并行數據。但是,實際上要求其發送和接收的數據格式卻不僅僅是并行的,在許多情況下是串行的。例如,為了節省傳輸導線,降低成本,提高可靠性,機間距離較長的通信都采用串行通信。又如,由光電脈沖編碼器輸出的反饋信號是串行的脈沖列,步進電動機要求提供串行脈沖等等。這就要求應將外部送往計算機的串行格式的信息轉換成CPU所能接收的并行格式,也要將CPU送往外部的并行格式的信息轉換成與外圍設備相容的串行格式,并且要以雙方相匹配的速率和電平實現信息的傳送。這些功能在CPU控制下主要由相應的接口芯片來完成。

(3)解決CPU的負載能力和外圍設備端口選擇問題

即使是CPU和某些外圍設備之間僅僅進行并行格式的信息交換,一般也不能將各種外圍設備的數據線、地址線直接掛到CPU的數據總線和地址總線上。這里主要存在兩個問題,一是CPU總線的負載能力的問題:二是外圍設備端口的選擇問題。因為過多的信號線直接接到CPU總線上,必將超過CPU總線的負載能力,采用接口電路可以分擔CPU總線的負載,使CPU總線不致于超負荷運行,造成工作不可靠。CPU和所有外圍設備交換信息都是通過雙向數據總線進行的,如果所有外圍設備的數據線都直接接到CPU的數據總線上,數據總線上的信號將是混亂的,無法區分是送往哪一個外圍設備的數據還是來自哪一個外圍設備的數據。只有通過接口電路中具有三態門的輸出鎖存器或輸入緩沖器,再將外圍設備數據線接到CPU數據總線上,通過控制三態門的使能(選通)信號,才能使CPU的數據總線在某一時刻只接到被選通的那一個外圍設備的數據線上,這就是外圍設備端口的選址問題。使用可編程并行接口電路或鎖存器、緩沖器就能方便的解決上述問題。

此外,接口電路可實現端口的可編程功能以及錯誤檢測功能。一個端口通過軟件設置既可作為輸入口又可作為輸出口,或者作為位控口,使用非常靈活方便。同時,多數用于串行通信的可編程接口芯片都具有傳輸錯誤檢測功能,如可進行奇/偶校驗、冗余校驗等。

接口硬件包含哪些部分?

(1)基本邏輯電路

命令寄存器

狀態寄存器

數據緩沖寄存器

(2)端口地址譯碼電路

根據地址總線上的信號確定是否選中該接口的某個寄存器(端口)

(3)供選電路

與其它部件的連接電路,如與中斷控制器連接以實現中斷方式的數據傳送。

接口軟件有什么功能?

一個完整的設備接口程序包括:

(1)初始化程序段

(2)傳送設置程序段

(3)主控程序段

(4)結束程序段

(5)人機接口程序段

設備驅動程序就是一種標準化的接口軟件。

接口電路有哪些形式?

固定式結構:SSI,MSI (IC)

半固定結構:GAL, PAL

可編程結構:可編程芯片

CPU如何與接口進行數據交換?

查詢方式:CPU<>接口 先確認外設已準備好,才進行傳送

中斷方式:CPU<>接口 為避免不斷讀取狀態位檢查設備是否已準備好而造成等待循環,當輸入設備準備好時,才向CPU發中斷請求,CPU響應后轉入執行中斷服務程序。

DMA方式:存儲器<>接口 接口<>接口 存儲器<>存儲器

I/O端口

什么是I/O端口?

CPU與外設通信時,傳送的數據信息,狀態信息和控制信息分別進入接口電路中不同的寄存器,通常將這些寄存器和它們的控制邏輯統稱為I/O端口(Port),CPU可對端口中的信息直接進行讀寫。

數據端口:存放數據,是主機和外設之間交換的基本信息,長度一般為1-2字節,主要起數據緩沖的作用。

狀態端口:指示外設的當前狀態,每種狀態用1位表示,每個外設可以有幾個狀態位,由CPU讀取以測試或檢查外設的狀態。最常用的狀態位有準備就緒位(Ready),忙碌位(Busy)和錯誤位(Error)。

命令端口:也稱為控制端口,用來存放CPU向接口發出的各種命令和控制字,以便控制接口或設備的動作。常見的命令信息位有啟動位,停止位,允許中斷位等。

I/O端口編址方式

數據信息,狀態信息和控制信息的含義各不相同,但在微機系統中,CPU通過接口與外設交換數據時,只有輸入(IN)和輸出(OUT)兩種指令,所以只能把狀態信息和命令信息也都當作數據信息來傳送。

I/O端口的編址方式: 存儲器映象尋址方式和I/O指令尋址方式。

存儲器映象尋址方式(Memory Mapped I/O):把每一個I/O端口都看作一個存儲單元,并與存儲單元一樣統一編址,可使用訪問存儲器映象的所有指令來訪問I/O端口。

I/O單獨編址方式:對系統中的輸入輸出端口地址單獨編址,構成一個I/O地址空間,不占用存儲空間,用專門的IN和OUT指令來訪問這種具有獨立地址空間的端口。8080/Z80/8088和8086等都采用此種方式。8086用地址總線的低16位來尋址I/O端口,可尋址的端口數最大可達到65536個。

I/O指令

如何訪問I/O端口?通過執行I/O指令。

Intel 8086的I/O指令有哪些?

IN AL, PORT8 ;AL《(PORT8)

IN AL, DX ;AL《(DX)

OUT PORT8, AL ;(PORT8)《AL

OUT DX, AL ;(DX)《AL

其中,PORT8表示8位端口地址, PORT16表示16位端口地址,AX可以替代AL。

例如,MOV DX, 300H ; DX《300H

IN AL, DX ; AL《(DX)

MOV DX, 301H ; DX《301H

OUT DX, AL ; (DX)《AL

IN AX, 80H ; AL 《80H AH 《81H

I/O端口地址譯碼原理

如何在CPU執行I/O指令時可以訪問到相應端口地址的I/O端口?設計I/O端口地址譯碼線路。

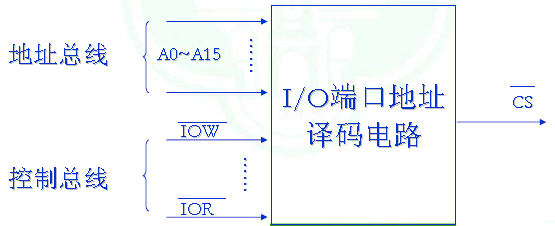

如何設計I/O端口地址譯碼電路?通過地址總線和控制總線產生端口芯片的選擇信號(CS)。

I/O端口地址譯碼電路分類

端口地址譯碼電路的種類:

固定式單端口地址譯碼 采用門電路或譯碼器進行譯碼,設計完畢后端口地址不能更改。

可選式端口地址譯碼 通過比較器和譯碼器等組成,端口地址可以通過DIP開關進行更改。

采用可編程邏輯陣列實現邏輯電路

固定式單端口地址譯碼(1)

固定式單端口地址譯碼(2)

固定式單端口地址譯碼(3)

3-8譯碼器譯碼電路

接口的輸入輸出方法

(1)無條件傳送方式

也稱為同步傳送方式,主要用于對簡單外設進行操作。對這類外設,在任何時刻均已準備好數據或處于接收數據狀態,如LED顯示器的明滅控制(如下圖所示)

(2)查詢方式

執行讀端口指令不斷查詢接口狀態,若接口準備好, 則可以執行I/O指令輸出數據到接口或或從接口讀入數據。

(3)中斷方式

接口準備好之后,便請求CPU中斷現在執行的程序,轉而為之服務。

(4) DMA方式

當外設有大量數據需要與主存儲器交換時,DMA控制器向CPU申請接管總線,若成功,則控制外設與主存儲器直接交換數

DMA方式讀磁盤的過程

系統啟動時,3個開關打向上端,總線與CPU/存儲器/外設連接,并由CPU來控制,進行DMA傳輸前,首先初始化8237A DMA控制器,設定傳送數據的計數器,起始地址,DMA通道和傳送方式。

CPU向磁盤控制器發出讀盤命令,磁盤控制器讀出數據。

磁盤控制器準備好數據后,向DMA控制器發送一個DMA請求信號DREQ,DMA控制器送一個保持請求信號HRQ到CPU的HOLD輸入端,CPU發回保持響應信號HLDA信號,中止當前程序運營。DMA控制器收到HLDA后,將3個總線開關置向下方,讓總線與CPU脫開而與DMA控制器相連。

DMA控制器取得總線控制權后,通過地址總線向存儲器發送地址信號,并向磁盤控制器發出DMA確認信號DACK。

DMA控制器使控制總線上IOR#和MEMW#信號有效,使得磁盤控制器能向數據總線輸出數據字節,并使存儲器單元能夠被寫入。

完成一個字節傳送后,DMA控制器自動修改內部寄存器的內容并指向下一個字節的地址,通過計數器的遞減完成所有數據的傳送。

DMA傳送結束后,DMA控制器撤銷它對CPU發出的保持信號HRQ,并釋放總線。

CPU在每一個非鎖定時鐘周期結束后,都檢測HOLD引腳看是否有DMA信號。

-

接口設計

+關注

關注

2文章

196瀏覽量

29847 -

dma

+關注

關注

3文章

560瀏覽量

100548 -

狀態寄存器

+關注

關注

0文章

39瀏覽量

7083 -

命令寄存器

+關注

關注

0文章

1瀏覽量

1246

原文標題:接口設計

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

讀懂命令寄存器狀態寄存器在接口設計中的作用

讀懂命令寄存器狀態寄存器在接口設計中的作用

評論