本系列所有演示實驗均出自由東南大學湯勇明教授、張圣清教授與Xilinx大學計劃經理陸佳華先生所編著的教材《搭建你的數字積木·數字電路與邏輯設計(Verilog HDL&Vivado版)》。此教材為教育部Xilinx公司產學合作專業綜合改革重點支持項目,并作為Xilinx公司大學計劃指定教材。

本書系統論述了數字電路與邏輯設計的理論、方法與實踐技術。全書基于Verilog HDL與Vivado開發環境,共18章,詳盡介紹了如下內容: 邏輯設計與Vivado基礎、布爾代數與Verilog HDL基礎、組合邏輯電路設計基礎、時序邏輯電路設計基礎、有限狀態機設計基礎、邏輯設計工程技術基礎、Vivado數字積木流程、串行通信接口控制器、RAM接口控制器、字符點陣顯示模塊接口控制器、VGA接口控制器、數字圖像采集、數字邏輯系統設計案例、單周期CPU設計案例、數字信號處理設計案例(FIR)、數字圖像處理設計案例、大學生FPGA設計案例以及Xilinx資源導讀。

為便于教師和廣大讀者學習與動手實踐,本書配套提供了教學課件、教學視頻及程序代碼等教學資源。本書適合作為普通高等院校電子信息類、電氣信息類、自動化類專業的本科生教材,也可作為相關專業研究生參考教材,并適合作為電子與電氣工程技術領域的科研工程技術人員的參考用書。

實驗步驟實驗內容本實驗介紹32位單周期處理器設計,并在EGO1開發板上實現。

實驗原理本實驗用以下模塊來實現:

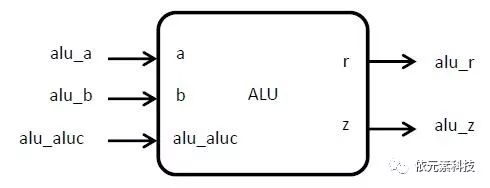

ALU:ALU算術邏輯單元,是處理器中的一個重要功能模塊,用來執行多組加減乘除等算術運算以及或與非等邏輯運算。算術邏輯單元的操作和種類由控制器覺定,處理的數據來自存儲器,處理后的結果送回存儲器或者暫存于算術邏輯單元中。ALU框圖如下所示,alu為控制信號,包括了ALU需要執行的運算的命令,a和b為兩個輸入,r是運算結果,z為carry。

REGFILE:一個32位深度的寄存器文件,用于緩存來自memory或ALU的數據指令op和func將被轉換成wreg、regrt、shift等信號,如下圖所示:

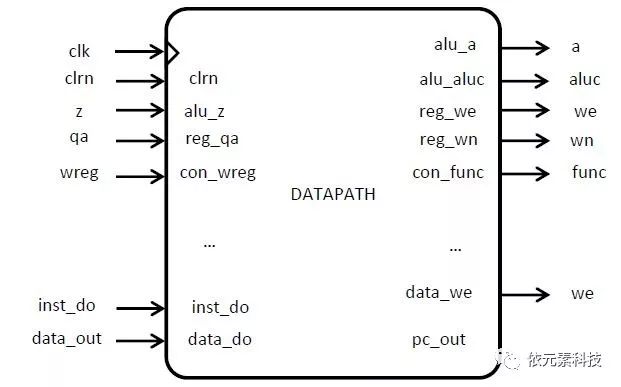

DATAPATH: DATAPATH用于連接所有的子模塊,同時具備指令計數器的功能,其框圖如下圖所示:

INSTMEM:instruction memory,指令儲存器,用于存放工程的測試指令。

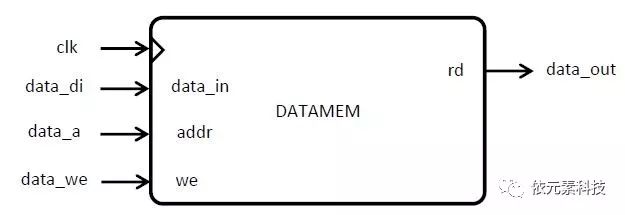

DATAMEM:用于存儲所有工程測試數據例如ALU計算結果等。輸入為寫使能、時鐘、地址以及寫入的數據,輸出為data_out信號,其框圖如下所示:

KEY2INST:將開關狀態轉換為CPU的指令。

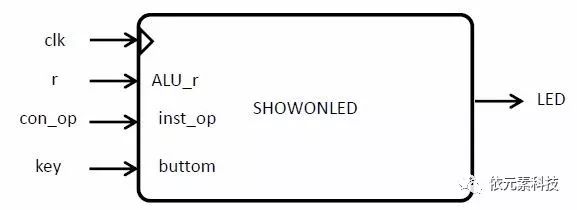

SHOWONLED:將最終計算結果或者開關狀態按照預先設定好的模式通過LED展示給用戶。輸入計算結果和開關狀態,輸出為控制LED的信號,其框圖如下所示:

通過本實驗,可實現一個CPU,根據輸入的指令控制LED燈。

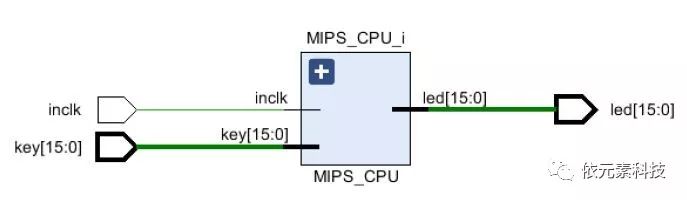

代碼說明:本實驗的代碼已經全部封裝成IP核,用戶只需將IP核調用并正確連續即可,MIPS_CPU.xdc為本實驗的管腳約束文件。

-

本實驗使用Vivado 2017.1 進行開發,開發界面如下。如果您未安裝vivado,安裝流程請點擊這里。

2.實驗RTL視圖:

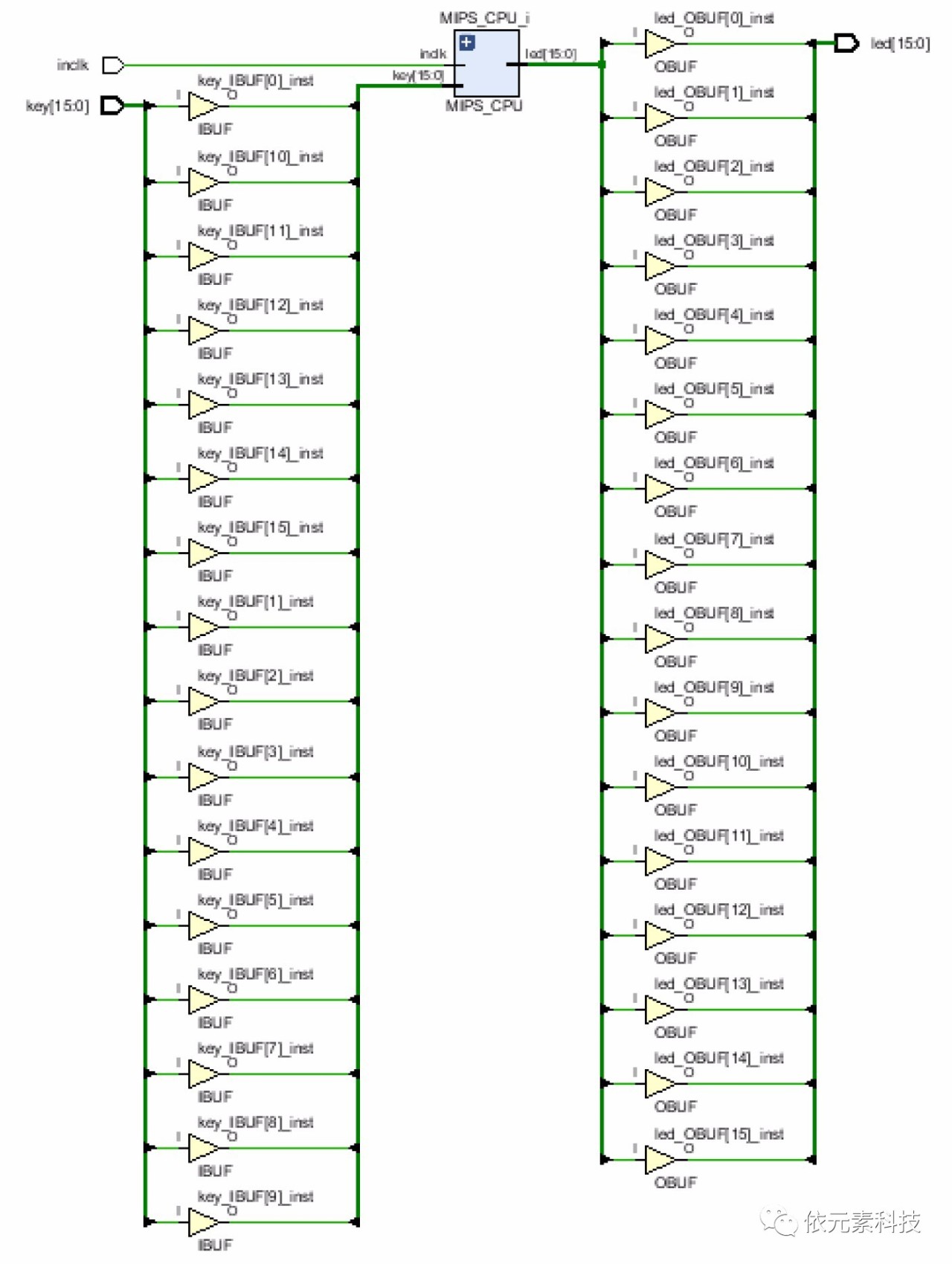

3.代碼綜合后效果圖:

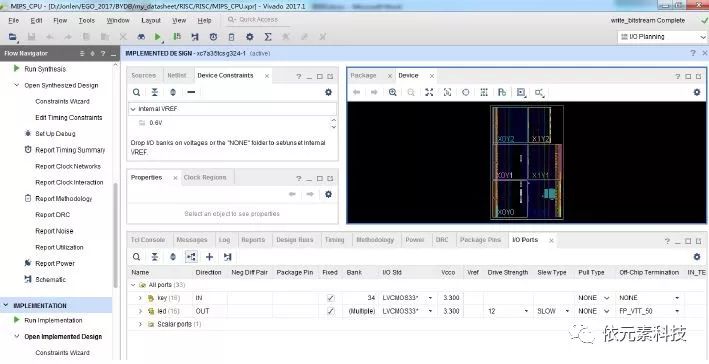

4. 代碼實現后效果圖:

具體vivado步驟請參看之前的微信文章,文章鏈接請點擊這里。

驗證流程將代碼下載到板卡后,可按照下面的操作實現一個簡單的加法運算,兩個家數分別為16位的0000000100000000和16位的0000000000000000,操作過程如下:

-

將B14-B0設置為0,將B15設置為0,然后再設置為1,完成系統復位。

-

將B9-B8設置為10,將B7-B0設置為00000001,然后將B13設置為1后馬上設置為0,目的是加載data+bh。

-

將B9-B8設置為11,將B7-B0設置為00000000,然后將B13設置為1后馬上設置為0,目的是加載data_bl。

-

將B9-B8設置為00,將B7-B0設置為00000000,然后將B13設置為1后馬上設置為0,目的是加載data_ah。

-

將B9-B8設置為01,將B7-B0設置為00000000,然后將B13設置為1后馬上設置為0,目的是加載data_al。

-

將B12-B10設置為000,這樣就選擇了加法運算模式。然后將B14設置為1,此時CPU運行運算,結果為0000000100000000,此時的結果將顯示在16位LED上。

-

ALU

+關注

關注

0文章

33瀏覽量

13107 -

eg01開發板

+關注

關注

0文章

1瀏覽量

1804 -

單周期處理器

+關注

關注

0文章

1瀏覽量

1395

原文標題:【玩轉EGO1系列教程三】:在EGO1開發板上實現RISC

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

OpenHarmony源碼編譯后燒錄鏡像教程,RK3566鴻蒙開發板演示

ARM開發板與FPGA的結合應用

ARM開發板與樹莓派的比較

如何選擇合適的ARM開發板

ElfBoard技術貼|如何在NXP源碼基礎上適配ELF 1開發板的UART功能

linux開發板與樹莓派的區別

linux開發板和單片機開發的區別

米爾基于NXP iMX.93開發板的M33處理器應用開發筆記

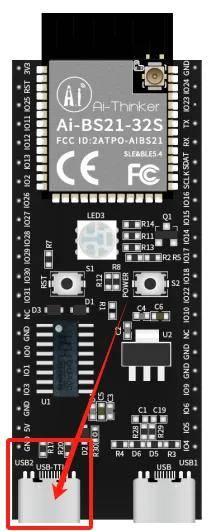

安信可星閃開發板or模組燒錄指導

RK3562開發板:安卓Linux開發從入門到精通(一)

ELF 1技術貼|開發板底板電源電路講解

基于EGO1開發板的32位單周期處理器設計案例

基于EGO1開發板的32位單周期處理器設計案例

評論