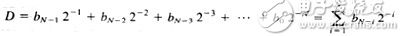

集成電路設計可分為兩大類:模仿和數字。為了顯現這兩類設計辦法的特征,我們必需首先定義模仿信號和數字信號。信號能夠被以為是電壓、電流或電荷等電量的可視值。信號應該反映物理系統的狀態或行為信息。模仿信號定義為在連續時間范圍內具有連續幅度變化的信號,圖1.1-1( a)為模仿信號的示例。數字信號是只在一些離散幅度值上有定義的信號,換句話說,數字信號是一些量化了的離散值。血型的數字信號是只要兩種幅值定義的信號的二進制加權和,如圖1.1-1( b)和式(1.1-1)所示。圖1.1-1 (b)是圖1.1-1(a)所示模仿信號的3位表示。

一個二進制數bi取值僅為0或1。因此,能夠用只工作在兩個穩定狀態的器件來完成數字電路。這招致廠很強的規則性,并可用代數辦法描繪電路的功用。岡此,數字電路設計者能夠得心應手地設計更復雜的電路。

模仿集成電路中還會遇到另一種信號,即模仿采樣數據信號。模仿采樣數據信號是指在連續幅值范圍內僅在時間離散點上有定義的信號。通常,采樣模仿信號堅持的是采樣周期完畢時的值,構成的是采樣堅持信號。模仿采樣堅持信號如圖1.1-1( c)所示。

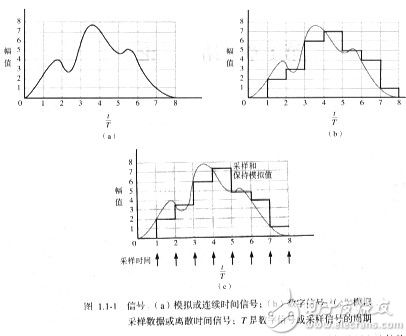

電路設計是為處理特定問題構思一個電路的發明性過程。對電路停止剖析和比擬可以更好天文解設計。如圖1.1-2(a)所示,電路剖析是從電路動身找出其特性的過程。剖析過程的-個重要特性是答案或特性是唯一的。另一方面,電路綜合或者設計是這樣一個過程,從請求的特性動身,找出滿足這些特性的電路。對設計來說計劃并不獨一,于是為設計者提供了發揮發明力的時機。比方以設計一個1.5Ω的電阻為例,能夠用三個0.5Ω電阻的串聯完成,也能夠用兩個1 Ω的電阻并聯后再與一個1 Ω的電阻串聯來完成,等等。一切設計都會滿足1.5 Ω電阻的請求,固然有些設計的其他特性可能會更好。圖1.1-2示出了綜合(設計)與剖析之間的不同。

理解集成和分立模仿電路設計的不同是很重要的。與集成電路不同,分立電路不把有源和無源元件制造在同一襯底上,而將器件嚴密地制造枉同一襯底上的一個主要的優點就是器件間的匹配也能夠作為設計思索的—,個下具。兩種設計方式的一個不同點是在集成電路設計中有源器件和無源器件的兒何尺寸是在設計者的控制之F的。在設計過程中這種控制賦予沒計者更人的自在度。另一個不同點就是集成電路設計無法用電路實驗板考證。因而,設計者必需采用計算機仿真的辦法來考證其電路的性能。再一個不同點是,在集成電路設計中,設計者將會更多地遭到與所用下藝相關的元器件類型的約束。

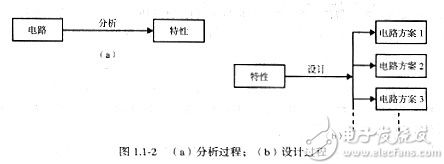

設計一個模仿集成電路分為很多步驟。圖l.l-3所示為一個集成電路設計的普通過程。

主要的步驟有:

1.定義

2.綜合或裝配

3.仿真或模型化

4.幅員設計

5.思索幅員寄生參數后的仿真(后仿真)

6,制造

7.測試和考證

上述一切步驟,除了加工制造外,其他過程均需設計者擔任。第一步是功用的定義和綜合。

這一步十分重要,由于這決議了設計的性能。當這些步驟完成后,設計者必需在制造之前可以確認這個設計。為此,下一步就是對電路停止仿真,察看電路性能。開端設計者只能運用電路物理層的近似參數仿真,一旦完成幅員設計,就能夠用從幅員得到的寄生參數信息檢查仿真結果。爾后設計者可重復用模仿結果改良電路的性能。一旦滿足了性能請求,就能夠進入下一步—一電路的幾何描繪(幅員)。通常狀況下,這種幾何描繪由在不同層面上(Z軸)的各種外形的矩形或多邊形(x-y平面)構成的計算機數據庫組成,它與電路的電性能親密相關。如前所述,幅員完成后,需求將幅員的寄生效應思索進去再次仿真。假如性能滿足,就能夠制造電路了。

制成之后,設計者將會面臨最后一步——肯定制成的電路能否滿足設計請求。假如在整個設計過程中設計者沒有認真思索這一步,那么在停止電路測試以及判別電路能否滿足設計請求時可能會遇到艱難。

正如前面所提到的,分立與集成模仿電路設計的區別之一是后者無法用電路實驗板考證。計算機仿真技術曾經有了長足的開展,能提供恰當的模型。

其優點包括:

·不需求電路實驗板

·具有監測電路任一處信號的才能

·可以將反應環路拆開

·可以方便的修改電路

.可以在不同的工藝和溫度條件下剖析電路

計算機仿真也有一些缺陷:

·模型的精度問題

·由于不收斂而得不出仿真結果

·對大電路停止仿真很費時間

·無法用計算機替代人的思想

由于仿真與設計過程親密相關,本書將在恰當的中央停止引見。

在完成上述各個設計步驟的過程中,設計者運用了三種不同的描繪格式:設計描繪、物理層描繪和模型/仿真描繪。設計描繪的格式用來肯定電路;物理層描繪用來定義電路的幾何外形;模型肪真描繪用來對電路停止仿真。設計者必需在每種描繪格式中都能對設計停止描繪。例如,模仿集成電路設計的第一步能夠用設計描繪格式完成,顯然,幅員設計階段能夠用物理層描繪格式,仿真階段可采用模型/仿真描繪格式。

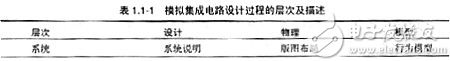

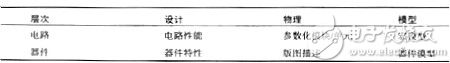

模仿集成電路設計還能夠用分層的觀念來描繪。表1.1-1展現了由器件、電路和系統構成的縱向層次,橫向分為設計、物理和模型三個層次。器件級是設計的最底層。能夠分別用器件性能、幾何圖形和器件模型作為設計、物理和模型的相應描繪。電路級是設計的較高層,能夠用器件的術語來表示。電路級的設計、物理和模型描繪的格式普通為:電壓電流關系、參數化的幅員和宏模型。設計的最高層是系統級——用電路來表示。系統級的設計、物理和模型描繪的格式為:數學或圖形描繪、芯片規劃規劃以及行為模型。

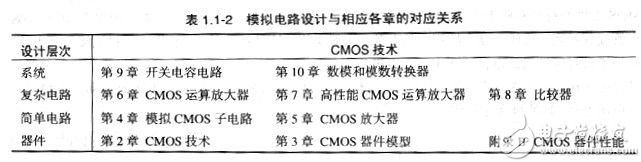

本書的組織體系偏重于集成電路設計的層次化觀念,表1.1-2示出了模仿電路設計與相應各章的對應關系。在器件級,第2章和第3章引見CMOS工藝技術及模型。為了設計CMOS模仿集成電路,設計者必需理解工藝技術,因而第2章概要地引見了CMOS工藝技術以及南工藝思索得出的設計規則。這些信息關于設計者了解工藝的限制和約束是十分重要的。在開端設計之前,設計者應該曾經曉得工藝和器件模型的電參數。建模在綜合與仿真這兩個步驟中是關鍵局部,這在第3章中做引見。設計者還應理解實踐器件的模型參數,以便肯定假定模型參數能否適宜,理想狀況下設計者已取得能夠對這些參數停止丈量的測試芯片。最終,制成后的模型參數測試可被用來測試完好的電路。器件描繪辦法在附錄B中做了引見。

第4章與第5章主要引見由兩個管子及兩個以上管子構成的電路,這類電路稱為簡單電路。在第6章到第8章中引見如何由這些簡單電路設計更復雜的電路。最后,在第9章和第10章中給出了由這些復雜電路設計的模仿系統。各種設計層次間的界線有時并不太明白。但是,根本的關系是有效的,能夠給讀者一個模仿集成電路設計的框架構造概念。

-

CMOS

+關注

關注

58文章

5710瀏覽量

235424 -

模擬電路

+關注

關注

125文章

1556瀏覽量

102721

發布評論請先 登錄

相關推薦

cmos集成電路原理是怎么樣的?

cmos集成電路原理是怎么樣的?

評論