雙核DSP(Digital Signal Processor,數字信號處理器)與單核DSP在多個方面存在顯著差異,這些差異主要體現在處理能力、任務分配、資源利用以及適用場景等方面。

一、處理能力

- 雙核DSP :

- 擁有兩個獨立的處理器核心,能夠并行處理多個任務。

- 主頻通常較高,能夠提供更高的計算性能,適合處理復雜且計算量大的數字信號。

- 能夠在同一時間內執行多個指令,提高處理速度和效率。

- 單核DSP :

- 只有一個處理器核心,按順序執行指令。

- 處理能力相對有限,適用于對實時性要求不高或計算量較小的應用。

- 主頻可能較低,以追求低功耗的實時信號處理。

二、任務分配與資源利用

- 雙核DSP :

- 單核DSP :

- 所有任務都在單個核心上順序執行,缺乏并行處理能力。

- 在處理復雜或高負載任務時,可能會出現性能瓶頸。

三、適用場景

- 雙核DSP :

- 單核DSP :

四、其他差異

- 架構與指令集 :雙核DSP和單核DSP在架構和指令集上可能有所不同,但具體差異取決于具體的芯片設計和制造商。

- 成本與價格 :由于雙核DSP具有更高的處理能力和更復雜的架構,其成本和價格通常也會高于單核DSP。

綜上所述,雙核DSP和單核DSP在處理能力、任務分配與資源利用以及適用場景等方面存在顯著差異。在選擇使用哪種DSP時,需要根據具體的應用需求和預算來進行綜合考慮。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

dsp

+關注

關注

555文章

8142瀏覽量

355195 -

數據管理

+關注

關注

1文章

311瀏覽量

19941 -

數字信號處理器

+關注

關注

5文章

478瀏覽量

27732

發布評論請先 登錄

相關推薦

熱點推薦

請問多核和單核調試區別和方法,有無操作系統(DSP/BIOS)的調試區別以及方法?

本帖最后由 一只耳朵怪 于 2018-6-19 14:39 編輯

具體說明下多核和單核調試區別和方法,有無操作系統(DSP/BIOS)的調試區別以及方法。等等!或者給些這方面的資

發表于 06-19 01:29

ARM+DSP 雙核外設分配 SUSPSRC的理解?

雙核如何來實現對外設的控制?SUSPSRC的作用,從數據手冊里面來看,只是說仿真掛起的時候由哪個ARM/DSP來控制。沒有明確說明SUSPSRC是用來分配某個外設給ARM或者DSP來單

發表于 06-21 10:04

DM8127 CCS調試DSP核

大家好!

目前我手上有一塊TI的DM8127 IPNC開發板,想要利用CCS對DSP單核調試,有些問題還望大家解答。之前只用過單核的DM6137這款芯片,對多核的操作不是很了解。

之前也看了一些帖子

發表于 06-22 02:24

怎么實現ARM/DSP雙核系統的通信接口的設計?

本文介紹了使用ARM和DSP雙CPU構成的雙核嵌入式系統的硬件平臺,以及源代碼開放的Linux作為嵌入式系統中操作系統的方法,給出了系統設計的總體框圖,詳細介紹了ARM和

發表于 05-26 06:21

imx6dl是單核運行還是雙核運行?

1.飛凌imx6dl的板子,請問是運行在單核模式還是雙核模式。uboot的maxcpus參數的值是1,應該是單核,但是內核里看到了cpu0核

發表于 12-05 06:39

DSP MCU雙核,什么是SP MCU雙核

DSP MCU雙核,什么是SP MCU雙核

各種數字消費產品特別是便攜式數字產品的功能已由單一走向多元化,因而原有的半導體解決方案已不能

發表于 03-26 15:00

?1058次閱讀

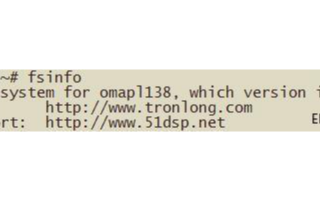

在OMAPL138的ARM核與DSP核上實現TL IPC雙核通信開發

TL_IPC是廣州創龍獨立開發的一種雙核通訊協議,這種開發方式適用于通信邏輯相對簡單的雙核程序的的開發。相較于syslink,它更簡單、直接,依賴更少。

發表于 08-06 08:34

?1596次閱讀

雙核cpu和單核cpu的區別

雙核CPU與單核CPU在多個方面存在顯著差異,這些差異主要體現在處理能力、性能、運行效率、功耗以及適用場景等方面。 一、概念與結構 雙核CP

評論