CMOS(cornplementary MOS)由成對(duì)的互補(bǔ)p溝道與n溝道MOSFET所組成.CMoS邏輯成為目前集成電路設(shè)計(jì)最常用技術(shù)的緣由,在于其有低功率損耗以及較佳的噪聲抑止才干.事實(shí)上,由于低功率損耗的需求,目前僅有CMOS技術(shù)被運(yùn)用于ULSI的制造.

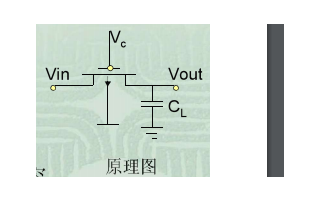

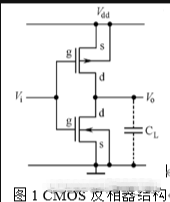

CMOS反相器

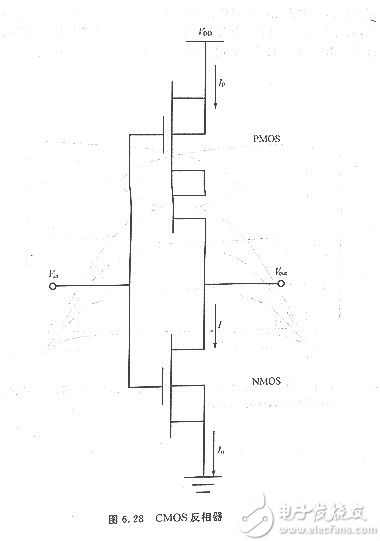

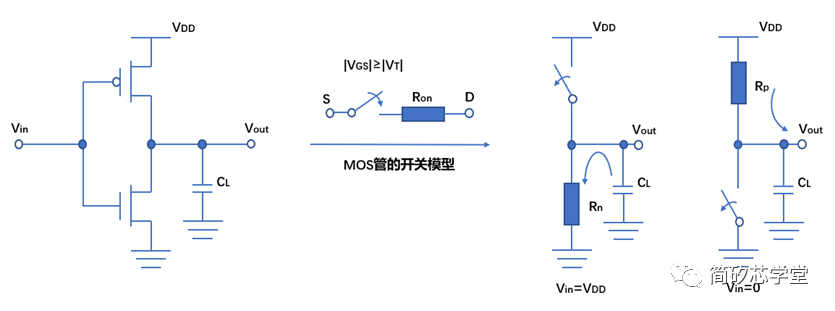

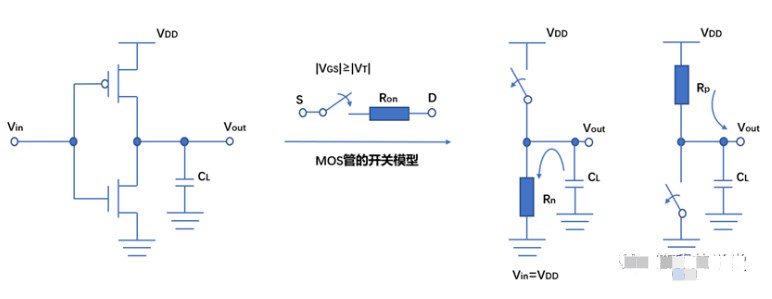

如圖6. 28所示,CMOS反相器為CMOS邏輯電路的基本單元.在CMOS反相器中,p與n溝道晶體管的柵極銜接在一同,并作為此反相器的輸入端,而此二晶體管的漏極也連接在一同,并作為反相器的輸出端.n溝道MOSFET的源極與襯底接點(diǎn)均接地,而p溝道MOSFET的源極與襯底則銜接至電源供應(yīng)端(VDD),需留意的是p溝道與n溝道MOSFET均為增強(qiáng)型晶體管,當(dāng)輸入電壓為低電壓時(shí)(即vin=O,VGsn=o

因此,輸出端經(jīng)過p溝道MOSFET充電至VDD,當(dāng)輸入電壓逐漸升高,使柵極電壓等于VDD時(shí),由于VGSn=VDD>VTn,所以n溝道MOSFET將被導(dǎo)通,而由于|VGSp |≈O<|VTp|,所以p溝道MOSFET將被關(guān)閉.因此輸出端將經(jīng)n溝道MOSFET放電至零電勢(shì),

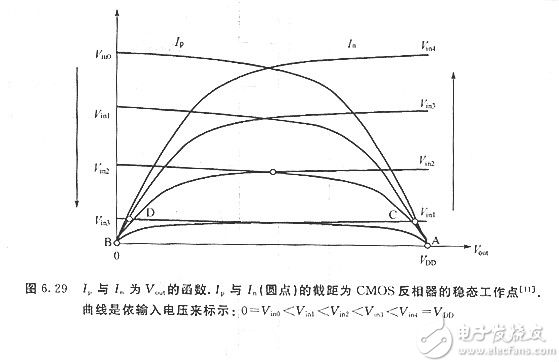

欲更深化天文解CMOS反相器的工作,可先畫出晶體管的輸出特性,如圖6.29所示,其中顯現(xiàn)Ip以及In為輸出電壓(Vout)函數(shù).Ip為p溝道MOSFET由源極(銜接至VDD)流向漏極(輸出端)的電流;In為n溝道MOSFET由漏極(輸出端)流向源極(銜接至接地端)

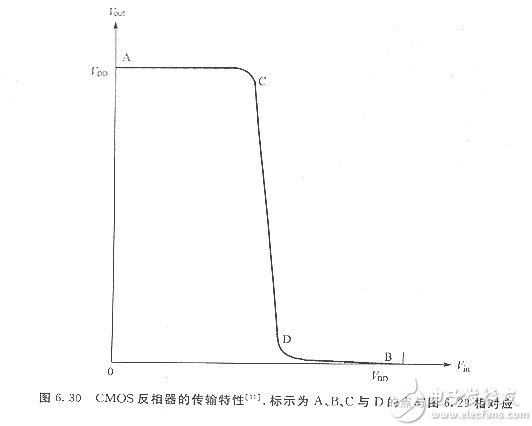

的電流.需留意的是在固定Vout下,增加輸入電壓(vin)將會(huì)增加In而減少Ip,但是在穩(wěn)態(tài)時(shí),In應(yīng)與Ip相同,關(guān)于給定一個(gè)Vin可由In(Vin)與Ip(Vin)的截距,計(jì)算出相對(duì)應(yīng)的Vout如圖6. 29所示.如圖6.30所示的Vin-Vout曲線稱為CMOS反相器的傳輸曲線.

CMOS反相器的一個(gè)重要的特性是,當(dāng)輸出處于邏輯穩(wěn)態(tài)(即Vout=或VDD)時(shí),僅有一個(gè)晶體管導(dǎo)通,因此由電源供應(yīng)處流到地端的電流非常小,且相當(dāng)于器件關(guān)閉時(shí)的漏電流.事實(shí)上,只需在兩個(gè)器件暫時(shí)導(dǎo)通時(shí)的極短暫態(tài)時(shí)間內(nèi)才會(huì)有大電流流過,因此與其他種類如n溝道MOSFET、雙極型等邏輯電路相比,其穩(wěn)態(tài)時(shí)的功率損耗甚低.

-

CMOS

+關(guān)注

關(guān)注

58文章

5710瀏覽量

235411 -

CMOS反相器

+關(guān)注

關(guān)注

0文章

19瀏覽量

6755

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

談?wù)?b class='flag-5'>CMOS反相器的靜態(tài)特性與動(dòng)態(tài)特性

virtuoso中進(jìn)行CMOS反相器和靜態(tài)寄存器的電路設(shè)計(jì)

CMOS反相器構(gòu)建Big Muff

CMOS反相器的電路結(jié)構(gòu)是怎樣的?它有哪些特點(diǎn)?

CMOS反相器工作原理及傳輸特性

反相器,反相器是什么意思

MOS反相器和CMOS反相器的詳細(xì)資料說明

什么叫CMOS電流源(漏)反相器?它有什么優(yōu)點(diǎn)?

為什么可以用CMOS反相器作為邏輯門電路緩沖級(jí)?

影響CMOS反相器特性的因素

TTL反相器和CMOS反相器的區(qū)別

CMOS反相器的工作原理和應(yīng)用

詳細(xì)講解cmos反相器的原理及特點(diǎn)

詳細(xì)講解cmos反相器的原理及特點(diǎn)

評(píng)論