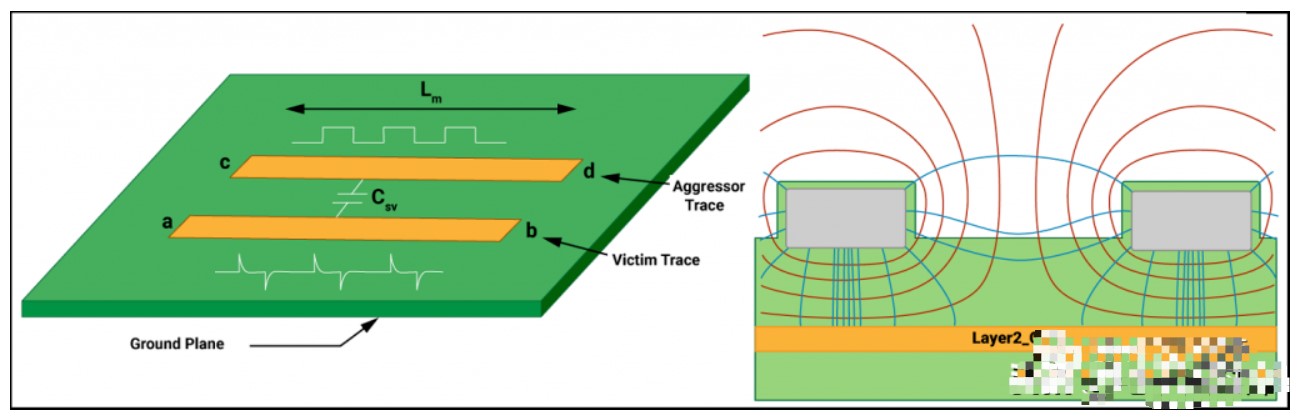

在高頻電路的精密布局中,信號線的近距離平行布線往往成為引發“串擾”現象的潛在因素。串擾,這一術語描述的是未直接相連的信號線間因電磁耦合而產生的不期望噪聲信號,它如同電路中的隱形干擾源,對信號完整性構成威脅。

鑒于高頻信號以電磁波形態沿傳輸線行進,信號線本身便充當了天線的角色,其周圍彌漫著電磁場能量。這些電磁場間的相互作用,不經意間編織出一張復雜的噪聲網絡,即所謂的串擾(Crosstalk)。

影響串擾的因素繁多,包括但不限于PCB板的物理結構、信號線之間的微妙距離、驅動端與接收端的電氣特性,以及信號線終端連接方式的差異。因此,為了有效抑制高頻環境下的串擾現象,布線策略需精心規劃,遵循以下原則:

在布線空間充裕的情況下,于串擾嚴重的線路間巧妙地插入地線或鋪設地平面,仿佛在嘈雜的都市中開辟一片靜謐綠洲,有效阻斷了噪聲的傳播路徑。若信號線不可避免地穿越時變電磁場區域,無法實現物理上的遠離,則可在信號線的背面布置廣闊的“地”域,以此作為電磁屏蔽,大幅削減干擾的影響。

在條件允許的范圍內,增大相鄰信號線之間的距離,縮短它們平行排列的長度,就如同在人群中拉開距離,減少不必要的身體接觸,從而降低相互干擾的幾率。對于時鐘信號這類關鍵線路,應盡量避免與敏感信號線平行,轉而采取垂直布局,如同交錯的交通網絡,既保證了通行效率,又減少了碰撞風險。若同層平行難以避免,那么在不同層間走線時應確保方向正交,形成立體交叉,進一步規避干擾。

數字電路的心臟——時鐘信號,因其邊沿變化迅速而更易成為串擾的源頭。設計時,應將時鐘線包裹在地線的懷抱中,并密集設置地線孔,以此減小分布電容,削弱串擾的力度。對于高頻應用,采用低電壓差分時鐘信號并實施全面接地措施,同時注重接地孔的完整性,確保每一處縫隙都被嚴密封閉,不讓噪聲有機可乘。

-

電磁

+關注

關注

15文章

1158瀏覽量

52640 -

串擾

+關注

關注

4文章

189瀏覽量

27409 -

高頻電路設計

+關注

關注

2文章

3瀏覽量

1892

發布評論請先 登錄

PCB中的串擾是什么?如何測量串擾?

評論