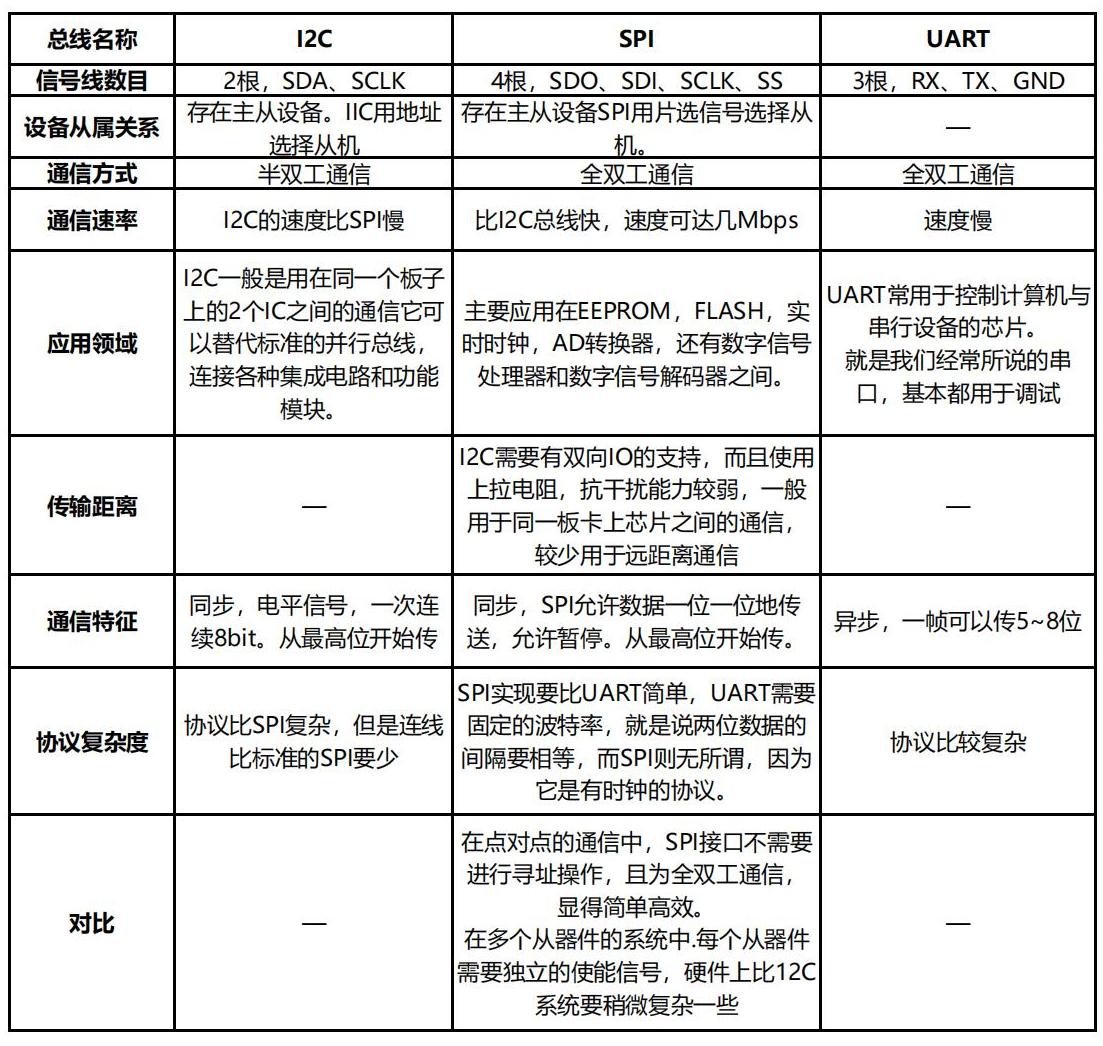

I2C(Inter-Integrated Circuit)通信總線,作為嵌入式系統設計中的一個關鍵組成部分,其靈活性和高效率使其在高級應用中備受青睞。本文旨在提供關于I2C通信總線的深度解析,包括其基本概念、特點、通信協議,以及在不同場景下的高級應用和最佳實踐。I2C接口只有2根信號線,總線上可以連接多個設備,硬件實現簡單,可擴展性強。I2C通信協議可以用普通GPIO引腳進行軟件模擬。I2C接口主要用于通訊速率要求不高,以及多個器件之間通信的應用場景。

01

I2C總線歷史

I2C(Inter-Integrated Circuit)總線是一種重要的串行通信協議,它的歷史可以追溯到上世紀80年代初期。以下是對I2C總線歷史的詳細介紹:

起源:

I2C總線技術由荷蘭的飛利浦半導體(現在的恩智浦半導體)在1982年開發。最初,這項技術是為了在電視機內部實現簡單、高效、低成本的通信而設計的。

設計目標:

設計I2C的初衷是減少電視機等復雜電子系統內部的布線數量,同時也降低制造成本。通過使用只有兩根線的通信總線,它有效地減少了器件間連接的復雜性。

技術發展:

隨著技術的成熟和普及,I2C協議得到了廣泛的應用和擴展。從最初的標準模式(100kHz),發展到快速模式(400kHz)和高速模式(3.4MHz)。

標準化和開放:

雖然最初由飛利浦半導體開發,但I2C協議后來被標準化并廣泛應用于多種設備中。飛利浦半導體放棄了對這項技術的專利權,使其成為開放標準。

廣泛應用:

I2C技術由于其簡單性和有效性,已成為嵌入式系統設計中不可或缺的一部分。

02

I2C通信總線基本概念

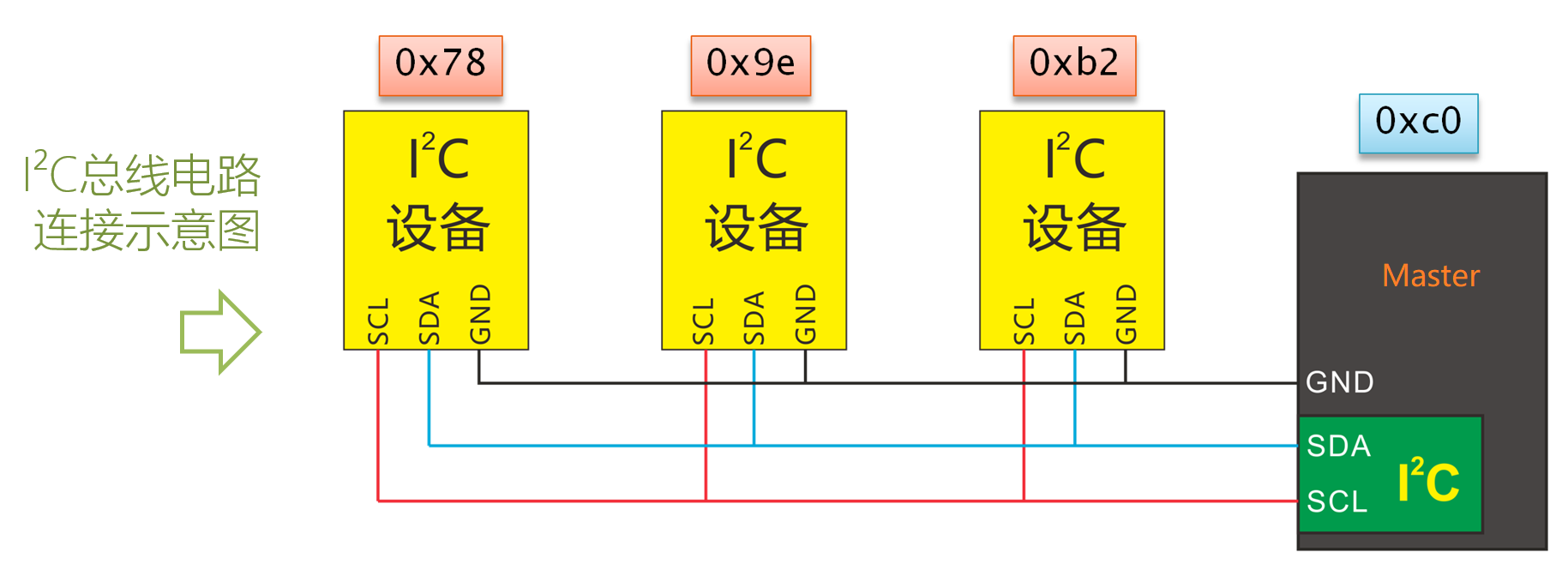

I2C是一種多主機、兩線制、低速串行通信總線,廣泛用于微控制器和各種外圍設備之間的通信。它使用兩條線路:串行數據線(SDA)和串行時鐘線(SCL)進行雙向傳輸。

特點

兩線制總線:I2C僅使用兩條線——串行數據線(SDA)和串行時鐘線(SCL)進行通信,有效降低了連接復雜性。

多主多從設備支持:I2C支持多個主設備和多個從設備連接到同一總線上。每個設備都有唯一的地址。

可變的時鐘速率:I2C總線支持不同的速率模式,如標準模式(100kbps)、快速模式(400kbps)和高速模式(3.4Mbps)。

同步通信:I2C是一種同步通信協議,數據傳輸由時鐘信號(SCL)來控制。

簡單的連接:I2C通信對硬件的要求比較低,很容易在微控制器和外圍設備間實現連接。

地址分配:每個I2C設備都通過一個7位或10位的地址來識別,這使得總線上可以連接多個設備。

阻塞傳輸:I2C支持阻塞傳輸機制,即主設備可以在傳輸過程中控制總線,防止其他設備發送數據。

應用廣泛:由于其簡單和靈活性,I2C被廣泛應用于各種電子產品中,如傳感器、LCD顯示器、EEPROM等。

總線仲裁和沖突檢測:在多主模式下,I2C能夠處理多個主設備同時嘗試控制總線的情況。

低功耗:I2C總線的設計使其成為低功耗的通信方式,適用于電池供電的設備。

基本特征

總線結構:

兩線制:使用兩條線進行通信,分別是串行數據線(SDA)和串行時鐘線(SCL)。

多主多從結構:支持多個主設備和多個從設備連接到同一總線上。

通信方式:

同步串行:數據傳輸同步于時鐘信號。

字節格式:每個字節由8位數據構成,加上開始和停止條件以及可選的應答位。

時鐘速率:

支持多種速率,包括標準模式(100kbps)、快速模式(400kbps)和高速模式(3.4Mbps)。

總線控制:

開始和停止條件:通信由主設備通過在SDA線上生成特定的信號模式來開始和結束。

地址幀:每次通信開始時,主設備發送一個地址幀來指定與之通信的從設備。

數據傳輸:

主從通信:主設備控制時鐘信號,向從設備發送或接收數據。

應答位:每個字節后,接收方

發送一個應答位(ACK)或非應答位(NACK),以告知發送方數據是否被成功接收。

地址和仲裁

設備地址:

7位或10位地址:每個I2C設備都有一個唯一的地址,允許在同一總線上連接多個設備。

總線仲裁:

在多主模式下,當兩個主設備同時嘗試控制總線時,I2C協議包含仲裁機制以決定哪個設備獲得控制權。

03

I2C數據傳輸流程

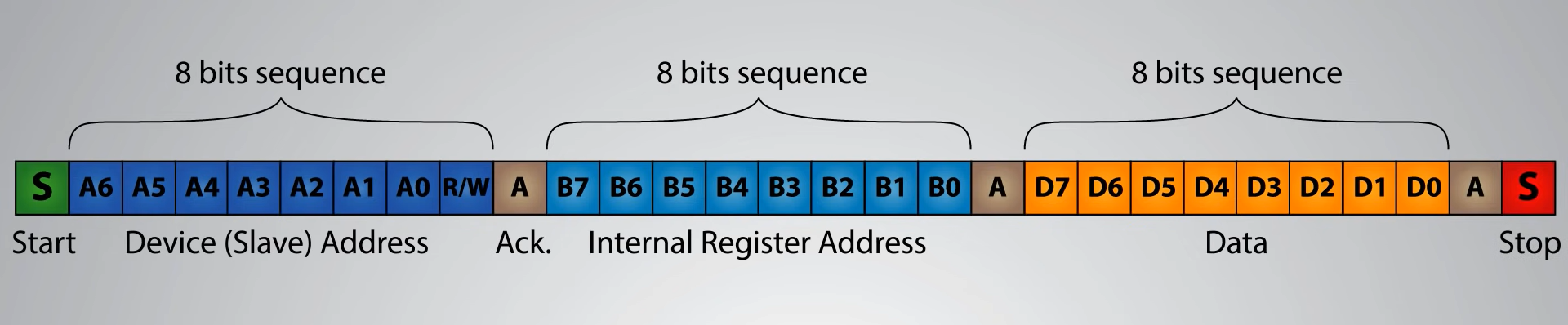

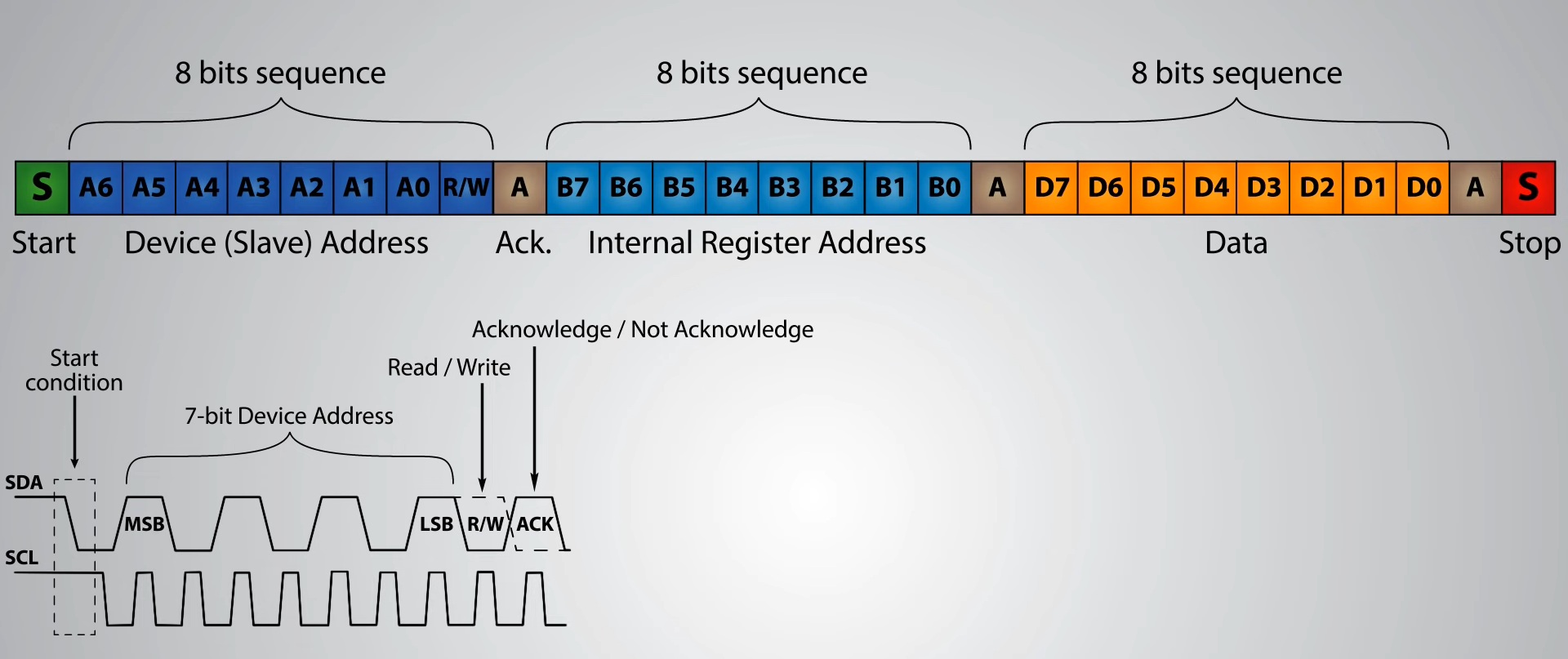

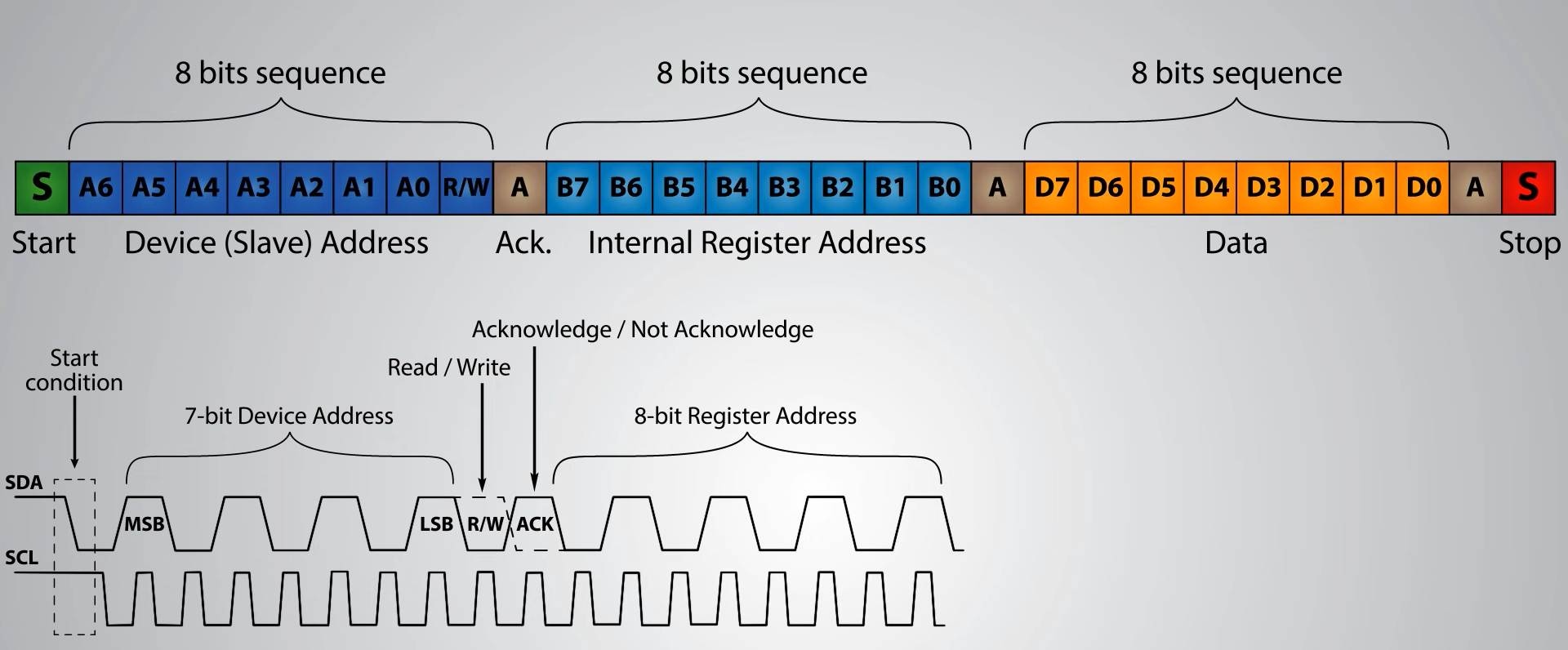

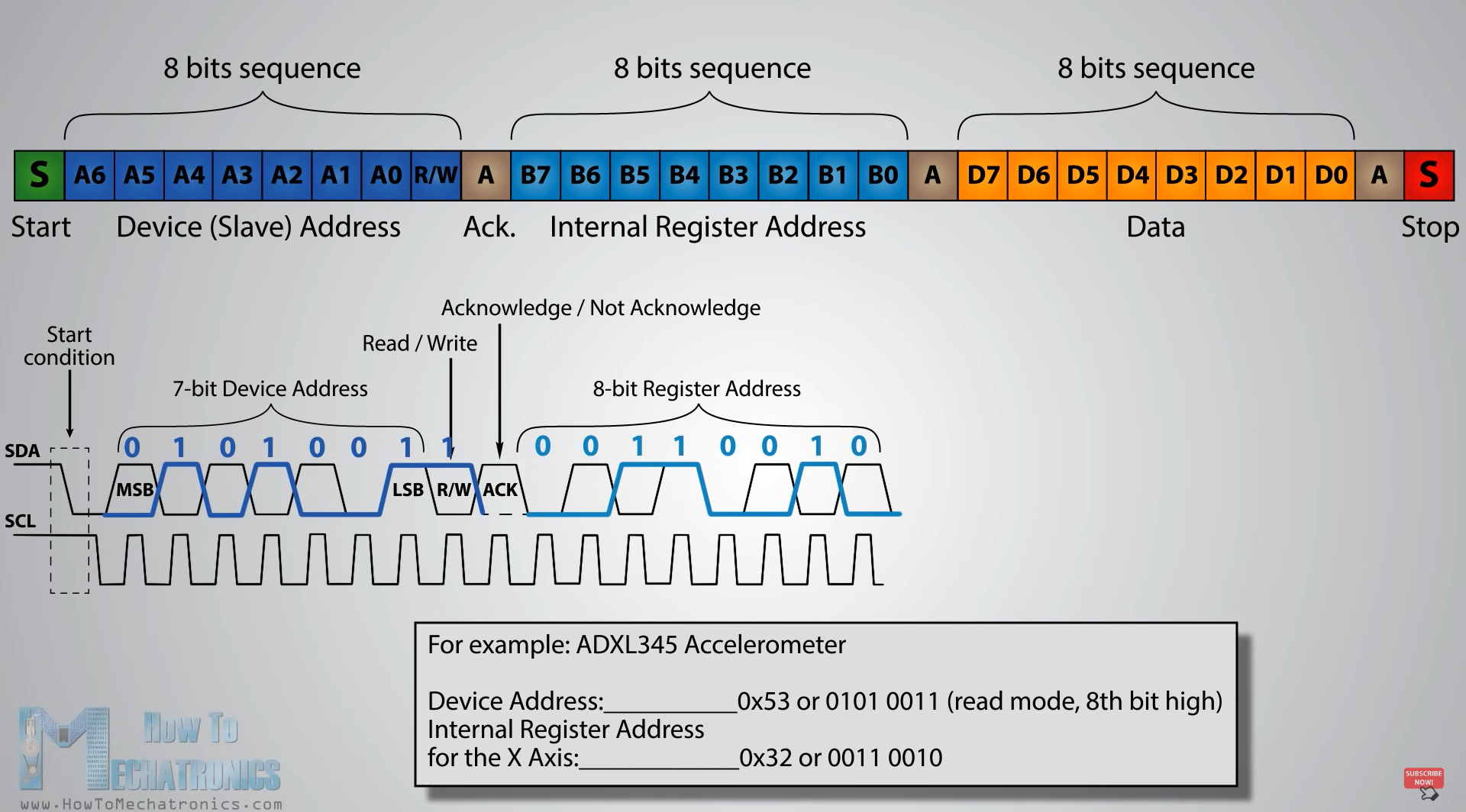

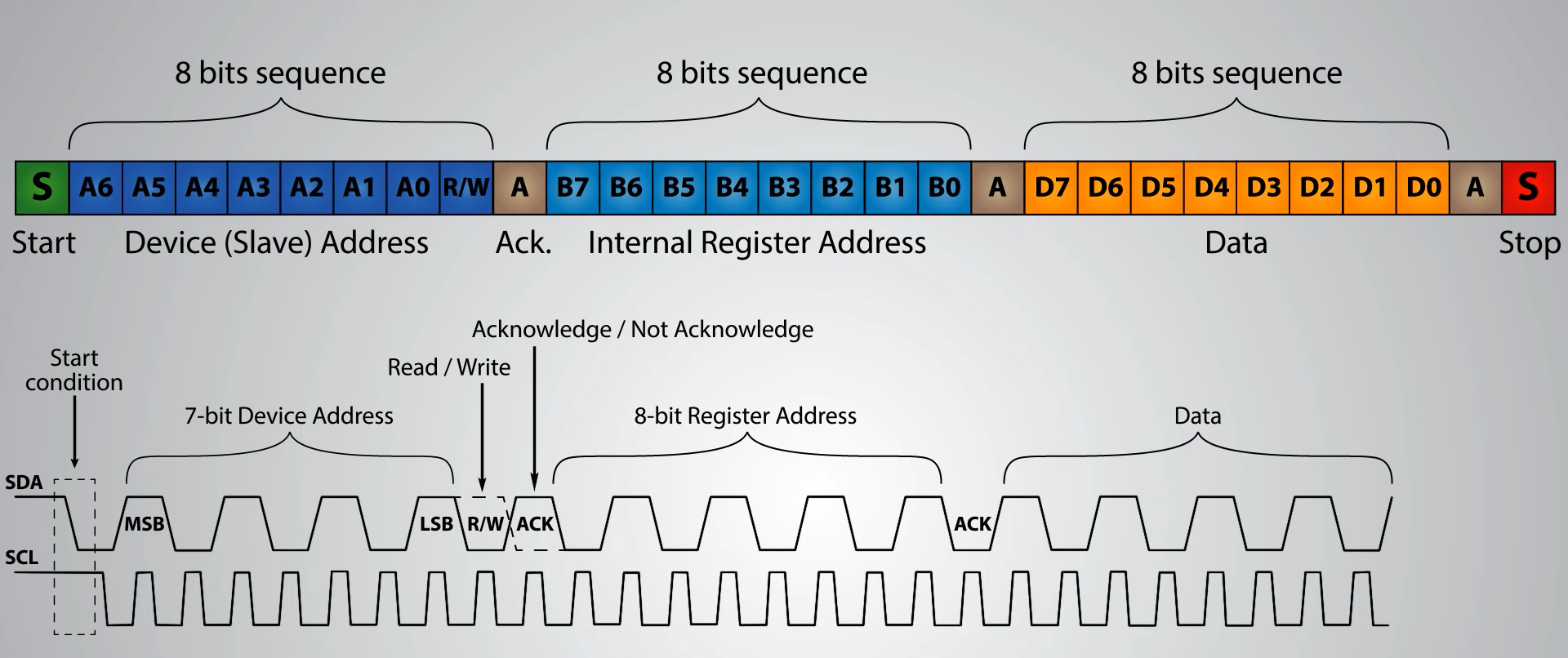

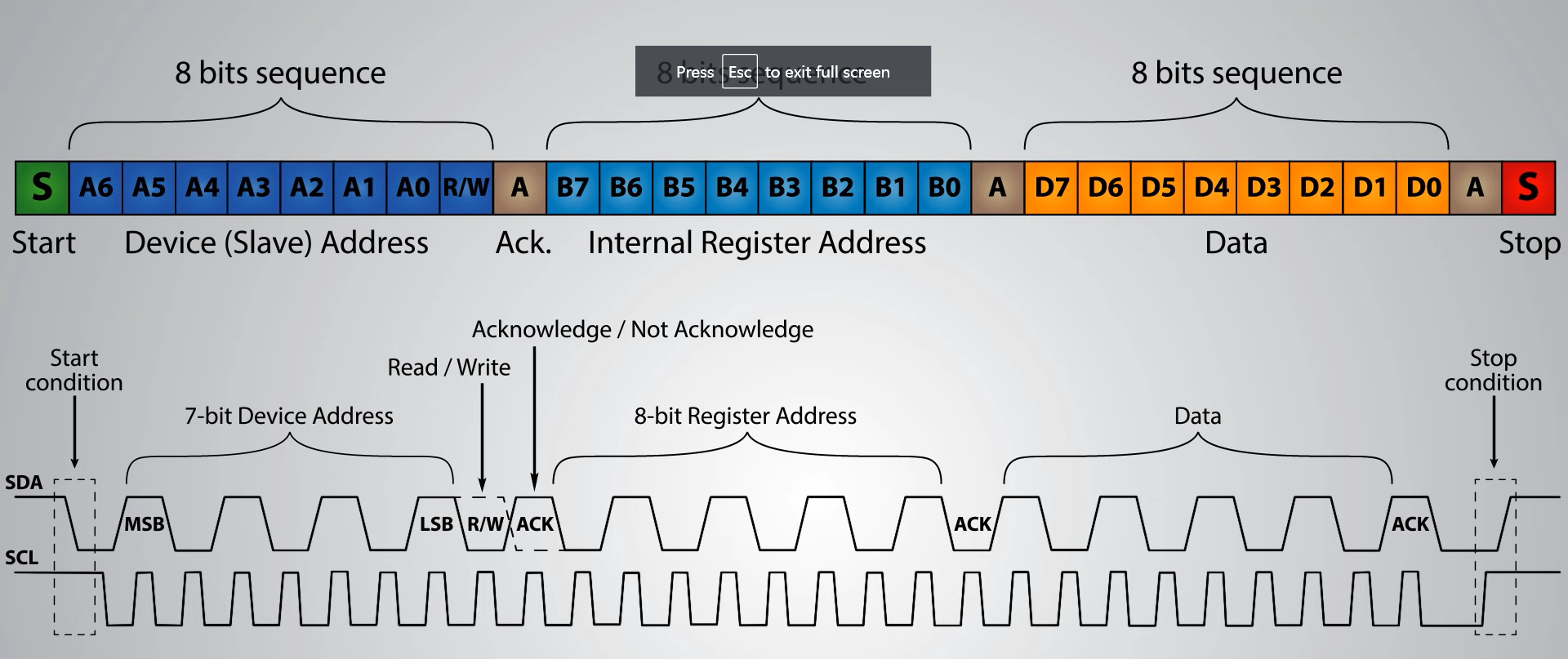

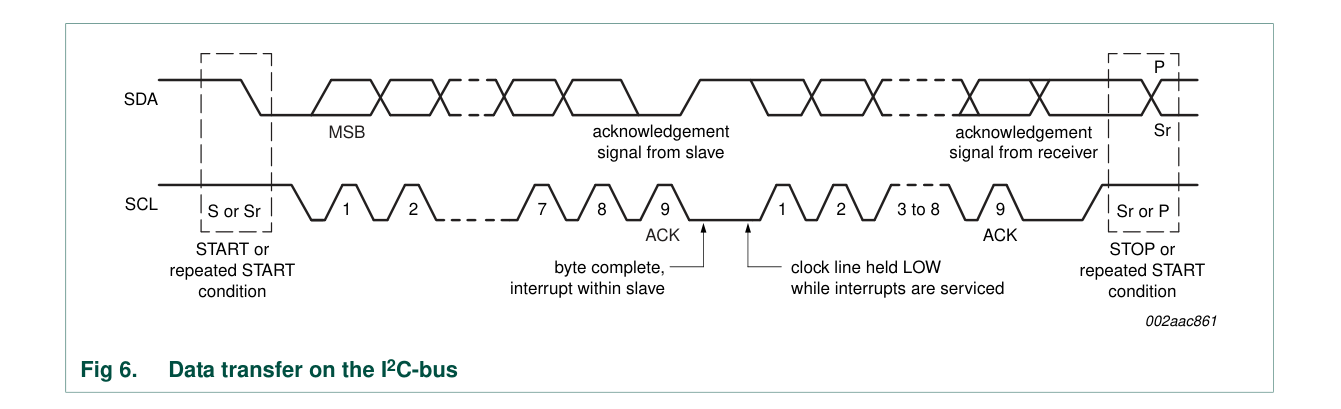

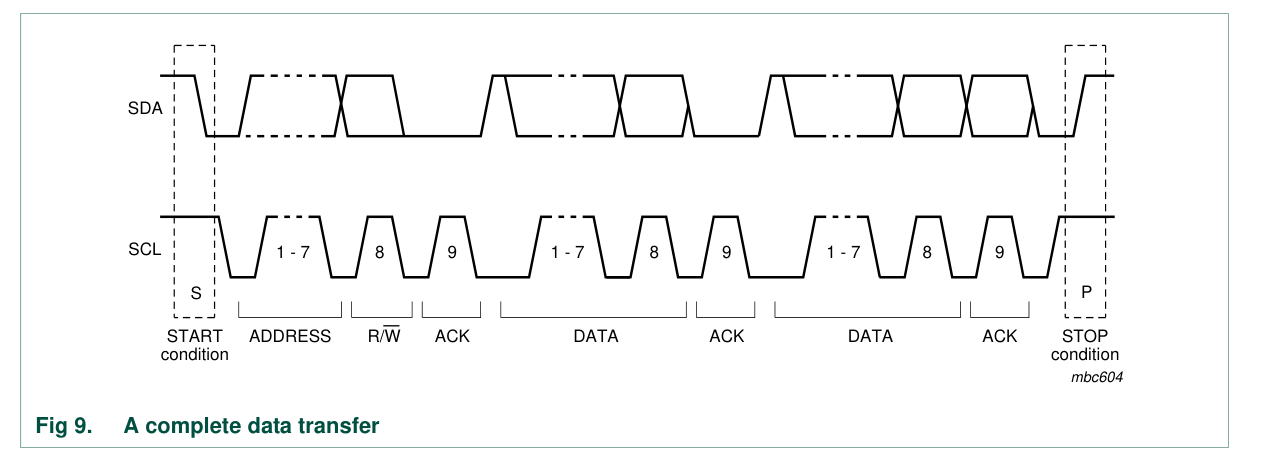

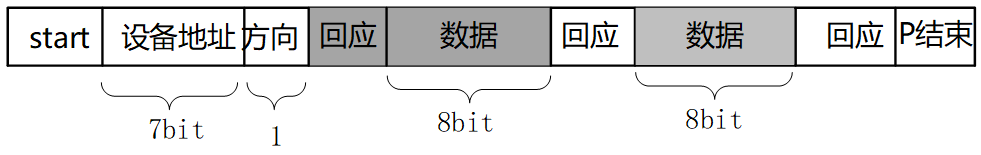

數據信號以8位的序列傳輸。所以在特殊的開始條件發生后,就會出現第一個8位序列,它指示了數據被發送到哪個從設備的地址。每個8位序列之后都會跟隨一個稱為確認的位。

在大多數情況下,第一個確認位之后會跟著另一個尋址序列,但這次是針對從設備的內部寄存器。在尋址序列之后是數據序列,直到數據完全傳輸完畢,并以一個特殊的停止條件結束。

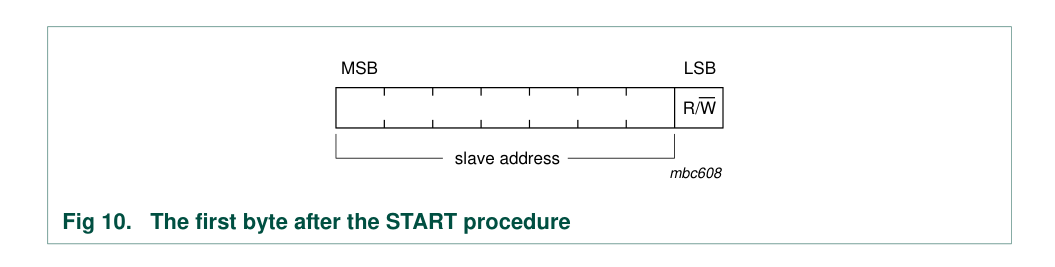

開始條件發生在數據線在時鐘線仍然高電平的時候變低。之后,時鐘開始,并且在每個時鐘脈沖期間傳輸每一位數據。設備尋址序列從最重要的位開始,以最不重要的位結束,實際上是由7位組成的,因為第8位用于指示主設備是向從設備寫入(邏輯低)還是從中讀取(邏輯高)。

下一個確認位由從設備用來指示它是否成功接收了前一個位序列。所以這次主設備將SDA線的控制權交給從設備,如果從設備成功接收了前一個序列,它將把SDA線拉低到所謂的確認狀態。

如果從設備沒有把SDA線拉低,這種狀態被稱為不確認,意味著它沒有成功接收前一個序列,這可能由多種原因造成。例如,從設備可能正忙,可能不理解接收到的數據,或者不能再接收任何數據等等。 在這種情況下,主設備決定如何繼續操作。

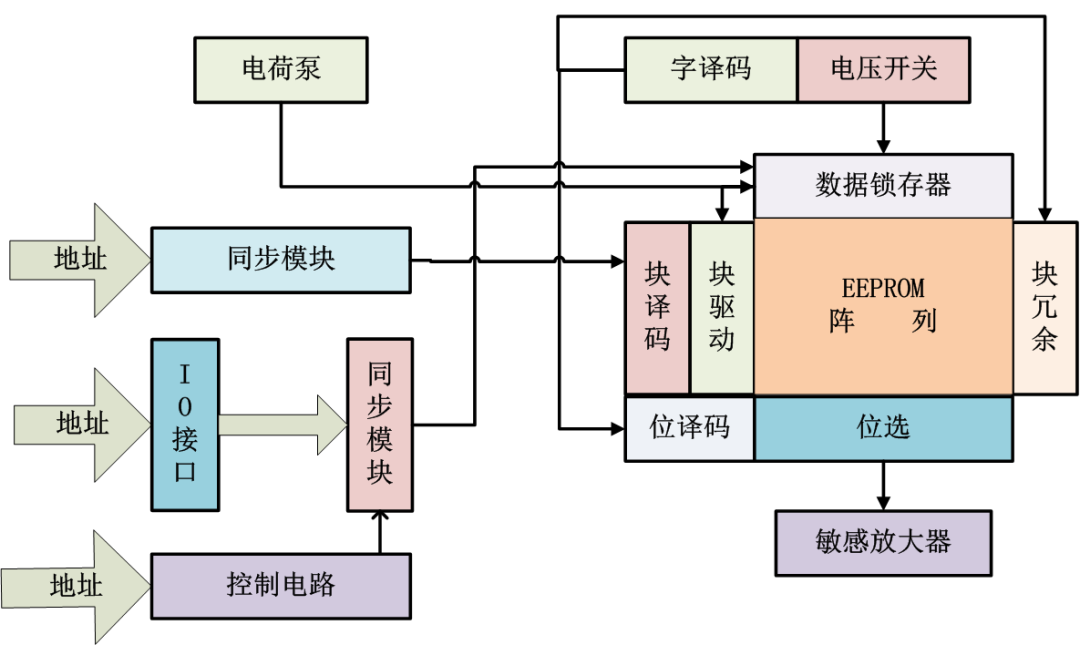

接下來是內部寄存器的尋址。內部寄存器是從設備內存中包含各種信息或數據的位置。

例如,ADXL345加速度計有一個獨特的設備地址和額外的內部寄存器地址,用于X、Y和Z軸。 因此,如果我們首先想讀取x軸的數據,我們需要發送設備地址,然后發送x軸的特定內部寄存器地址。這些地址可以從傳感器的數據手冊中找到。

在尋址之后,數據傳輸序列開始,要么來自主設備,要么來自從設備,這取決于在讀/寫位選擇的模式。

在數據完全發送之后,傳輸將以停止條件結束,當SDA線在SCL線高電平時從低變高。這就是I2C通信協議的工作原理。

上述內容出現了很多特定概念,我們下面來分別解釋他們:

SDA和SCL信號

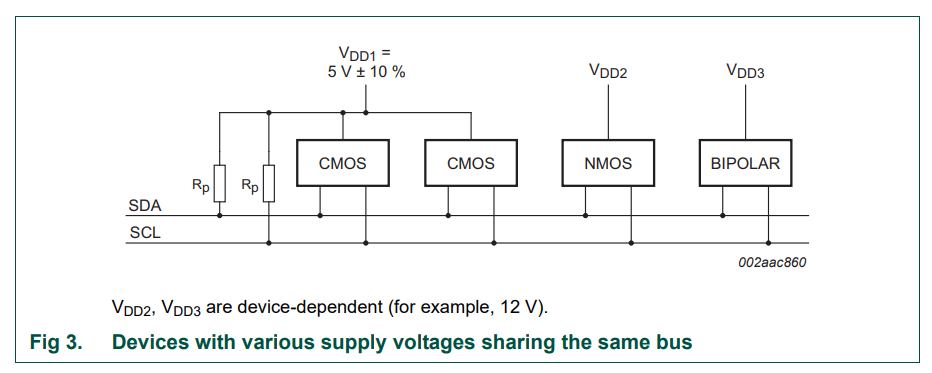

SDA和SCL都是雙向線路,通過電流源或上拉電阻連接到正電源電壓(見圖3)。 當總線空閑時,兩條線路都是HIGH。連接到總線的設備的輸出級必須具有開漏極或開集電極來執行有線與功能。I2C總線上的數據可以在標準模式下以高達100 kbit/s的速度傳輸,在快速模式下可達400 kbit/s,在快速模式+中可達1 Mbit/s,或在高速模式下可達3.4 Mbit/s。總線電容限制了連接到總線的接口數量。

對于單個主應用程序,如果總線上沒有設備會拉伸時鐘,主SCL輸出可以是推挽驅動器設計。

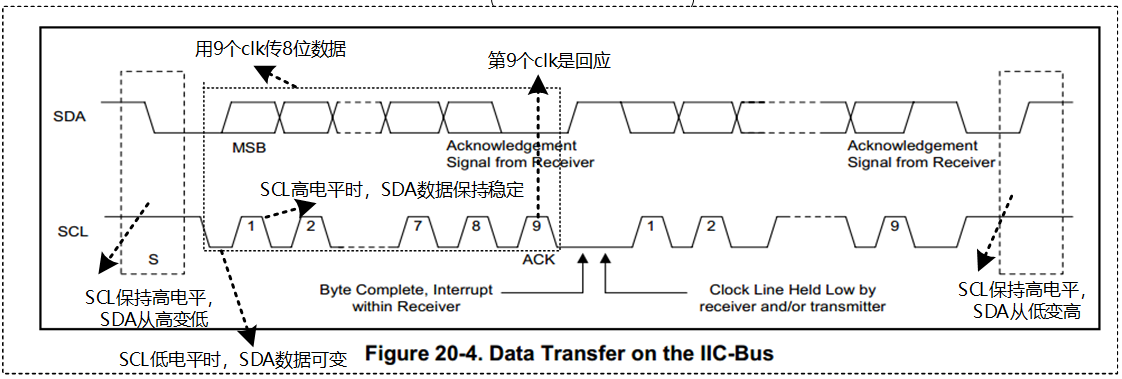

數據有效性

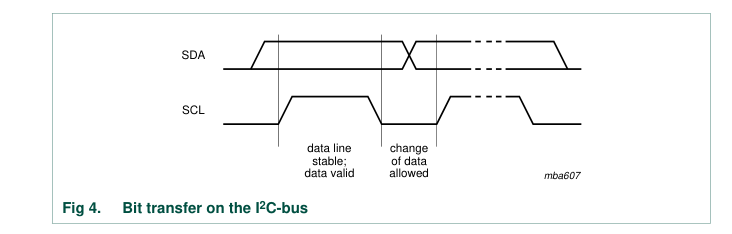

SDA線上的數據必須在時鐘HIGH期間保持穩定。只有當SCL線上的時鐘信號為LOW時,數據線的HIGH或LOW狀態才能改變(見圖4)。傳輸的每個數據位都會產生一個時鐘脈沖。

START和STOP條件

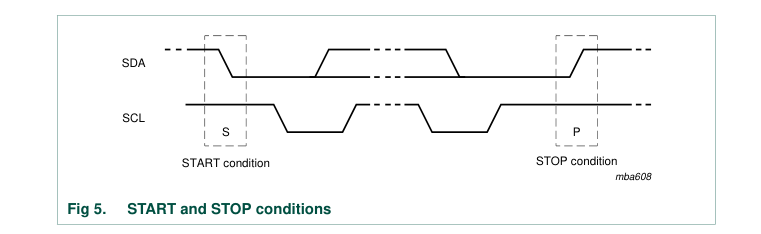

所有事務都以START(S)開始,并由STOP§終止(參見圖5)。 SDA線上SCL為HIGH時,HIGH到LOW的轉換定義了一個START條件。 SDA線上SCL為HIGH時,LOW到HIGH的轉換定義了一個STOP條件。

START和STOP條件總是由主設備產生。在START條件之后,總線被認為是忙碌的。在STOP條件之后的某個時間,總線被認為是空閑的。

如果產生了重復的START(Sr)而不是STOP條件,總線保持忙碌。在這方面,START(S)和重復的START(Sr)條件在功能上是相同的。

因此,對于本文檔的其余部分,S符號被用作代表START和重復的START條件的通用術語,除非Sr是特別相關的。

如果連接到總線的設備合并了必要的接口硬件,則檢測START和STOP條件是容易的。然而,沒有這種接口的微控制器必須在每個時鐘周期內對SDA線采樣至少兩次,以感知轉換。

字節格式

每一個放在SDA線上的字節必須是8位長。每次傳輸可以傳輸的字節數是沒有限制的。每一個字節后面必須跟一個確認位。數據以最有效位(MSB)為首進行傳輸(見圖6)。如果一個從機在執行其他一些功能之前不能接收或傳輸另一個完整的字節數據,例如處理一個內部中斷,它可以保持時鐘線SCL LOW,迫使主機進入等待狀態。當從機準備好接收另一個字節數據并釋放時鐘線SCL時,數據傳輸繼續進行。

Acknowledge(ACK)和Not Acknowledge(NACK)

確認發生在每個字節之后。確認位允許接收端向發送端發出信號,表示字節被成功接收,可以發送另一個字節。主設備產生所有的時鐘脈沖,包括確認的第九個時鐘脈沖。

確認信號定義如下:發送端在確認時鐘脈沖期間釋放SDA線,這樣接收端就可以拉SDA線LOW,并且在該時鐘脈沖的HIGH期間保持穩定的LOW(參見圖4)。設

當SDA在第九個時鐘脈沖期間保持HIGH時,這被定義為不確認信號。主設備然后可以產生一個STOP條件來中止傳輸,或者重復的START條件來啟動一個新的傳輸。有五個條件導致NACK的產生:

沒有接收器在總線上傳輸地址,所以沒有設備響應確認。

接收器無法接收或發送,因為它正在執行一些實時功能,并且還沒有準備好與主服務器進行通信。

在傳輸過程中,接收方收到了它無法理解的數據或命令。

在傳輸過程中,接收方不能接收到任何更多的數據字節。

主接收機必須向從發送機發出傳輸結束的信號。

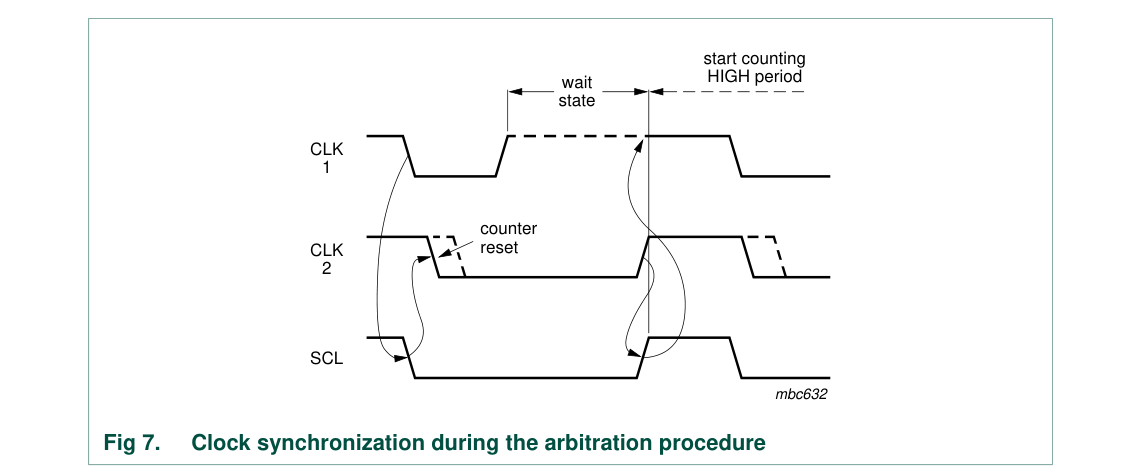

時鐘同步

兩個主控器可以同時在一個空閑總線上開始傳輸,必須有一種方法來決定哪個主控器控制總線并完成傳輸。這是通過時鐘同步和仲裁來實現的。在單主控器系統中,時鐘同步和仲裁是不需要的。

時鐘同步是通過I2C接口到SCL線的有線與連接來實現的。這意味著SCL線上的HIGH到LOW轉換會導致相關的主控器開始計數他們的LOW周期,一旦主控器時鐘變為LOW,它會保持SCL線處于該狀態,直到時鐘達到HIGH狀態(見圖7)。然而,如果另一個時鐘仍然在它的LOW周期內,這個時鐘的LOW到HIGH轉換可能不會改變SCL線的狀態。因此,SCL線被具有最長LOW周期的主控器保持為LOW。具有較短LOW周期的主控器在這段時間內進入HIGH等待狀態。

當所有主控機都結束了低周期時,SCL線釋放并變為高電平。此時主控機時鐘與SCL線的狀態沒有區別,所有主控機開始計算它們的高周期。第一個完成高周期的主控機再次拉低SCL線。

這樣,一個同步SCL時鐘就產生了,它的低周期由低周期最長的主控機決定,而它的高周期由高周期最短的主控機決定。

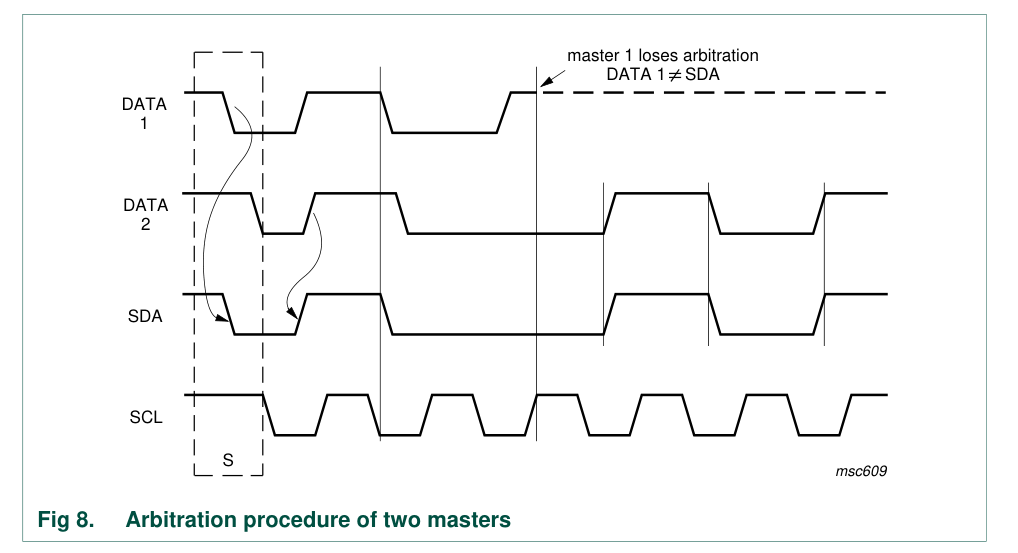

仲裁

仲裁,像同步一樣,是指只有在系統中使用多個主設備時才需要的協議部分。從設備不參與仲裁過程。只有總線空閑時,主設備才可以開始傳輸。兩個主設備可以在最小保持時間(tHD; STA)內產生一個START條件,這會導致總線上產生一個有效的START條件。然后需要仲裁來決定哪個主設備將完成它的傳輸。

仲裁逐位進行。在每個位期間,當SCL為HIGH時,每個主設備檢查SDA電平是否與它所發送的相匹配。這個過程可能需要許多位。兩個主設備實際上可以無誤地完成整個事務,只要傳輸是相同的。第一次一個主設備試圖發送HIGH,但檢測到SDA電平為LOW,主設備知道它已經失去了仲裁并關閉SDA輸出驅動器。另一個主設備繼續完成它的事務。

在仲裁過程中沒有信息丟失。一個失去仲裁的主設備可以產生時鐘脈沖,直到它失去仲裁的字節結束,并繼續產生時鐘脈沖。必須在總線空閑時重新開始它的事務。

如果一個主設備也包含一個從設備功能,并且它在尋址階段失去仲裁,有可能是獲勝的主設備試圖尋址它。因此,失敗的主設備必須立即切換到它的從設備模式。

圖8顯示了兩個主設備的仲裁過程。可能涉及更多內容,這取決于總線連接了多少主設備。當產生DATA1的主設備的內部數據電平與SDA線上的實際電平之間存在差異時,DATA1輸出被關閉。這不影響由獲勝的主設備發起的數據傳輸。

由于I2C總線的控制完全由競爭主設備發送的地址和數據決定,所以沒有中心主設備,總線上也沒有任何優先順序。

如果仲裁程序仍在進行,當一個主設備發送重復的START或STOP條件,而另一個主設備仍在發送數據時,則存在一個未定義的條件。換句話說,以下組合會導致一個未定義的條件:

主設備1發送重復的START條件,主設備2發送一個數據位。

主設備1發送STOP條件,主設備2發送一個數據位。

主設備1發送重復的START條件,主設備2發送一個STOP條件。

時鐘拉伸

時鐘拉伸通過保持SCL線LOW暫停事務。事務無法繼續,直到該線再次釋放為HIGH。時鐘拉伸是可選的,事實上,大多數從設備不包括SCL驅動程序,因此它們無法拉伸時鐘。

在字節級,設備可能能夠以較快的速度接收字節數據,但需要更多的時間來存儲接收到的字節或準備傳輸另一個字節。從設備可以在接收和確認一個字節后保持SCL線LOW,以迫使主設備進入等待狀態,直到從設備準備好在一種握手過程類型中進行下一個字節傳輸(見圖7)。

在位級,設備如微控制器,具有或不具有I2C總線有限的硬件,可以通過延長每個時鐘LOW周期來減慢總線時鐘。任何主設備的速度都適應于該設備的內部運行速率。

從地址和R/W位

數據傳輸遵循圖9所示的格式。在START條件(S)之后,發送一個從地址。這個地址是7位長,后面跟著第八位,這是一個數據方向位(R/W)——“0”表示傳輸(WRITE),“1”表示數據請求(READ)(參見圖10)。數據傳輸總是由master生成的STOP條件§終止。然而,如果master仍然希望在總線上通信,它可以生成一個重復的START條件(Sr)并在沒有首先生成STOP條件的情況下尋址另一個從設備。在這樣的傳輸中,各種讀/寫格式的組合是可能的。

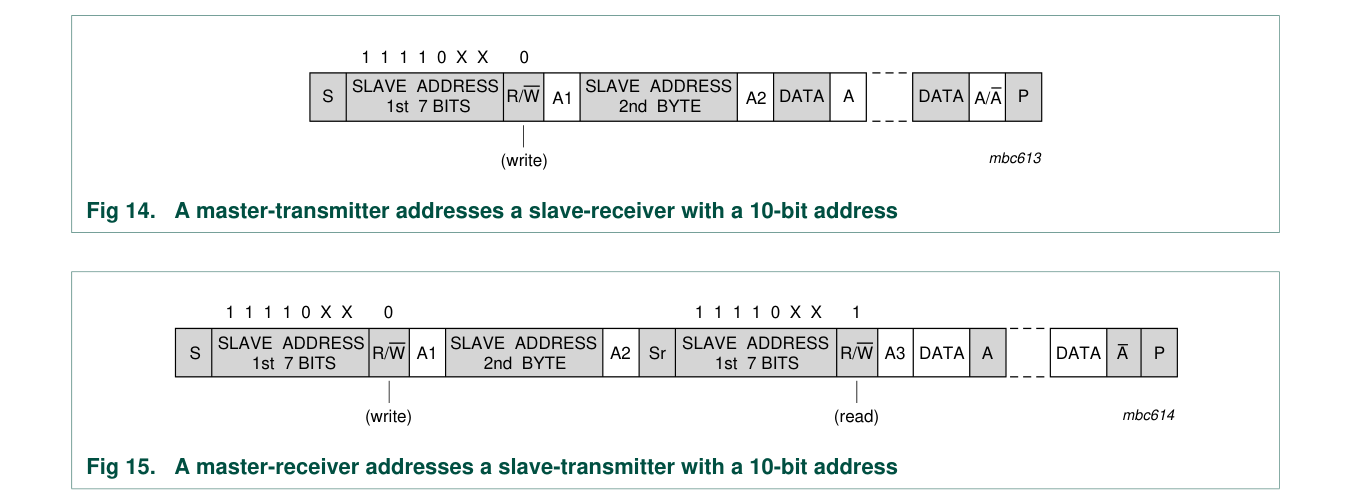

10位尋址

10位尋址擴展了可能的地址數。具有7位和10位地址的設備可以連接到同一個I2C總線,并且7位和10位尋址都可以在所有總線速度模式下使用。目前,10位尋址還沒有被廣泛使用。 10位從屬地址是由一個START條件(S)或重復的START條件(Sr)之后的前兩個字節組成的。 第一個字節的前7位是組合1111 0XX,其中最后兩個位(XX)是10位地址的兩個最有效位(MSB);第一個字節的第八位是R/W位,它決定了消息的方向。 雖然有8個可能的保留地址位1111 XXX的組合, 但只有四個組合1111 0XX用于10位尋址。其余四個組合1111 1XX被保留用于未來的I2C總線增強。

所有先前描述的7位尋址的讀/寫格式組合都可能用10位尋址。這里詳細介紹兩種格式:

主發送器用一個10位從屬地址向從屬接收器發送。 傳輸方向不變(見圖14)。當一個10位地址跟隨一個START條件時,每個從屬比較從屬地址第一個字節的前7位(1111 0XX)與自己的地址,并測試第八位(R/W方向位)是否為0。可能有多個設備找到一個匹配并產生一個確認(A1)。所有找到匹配的從屬比較從屬地址第二個字節的八位(XXXX XXXX)與自己的地址,但只有一個從屬找到一個匹配并產生一個確認(A2)。匹配的從屬仍然由主尋址,直到它接收到一個STOP條件§或重復的START條件(Sr),后面跟著一個不同的從屬地址。

主接收器用一個10位從屬地址讀取從屬發送器。 傳輸方向在第二個R/W位之后改變(圖15)。直到并包括確認位A2,過程與前面描述的用于一個從屬發送器的程序相同。主發送器尋址從接收器。在重復的START條件(Sr)之后,匹配的從設備記住它之前被尋址過。這個從設備然后檢查Sr之后的從地址的第一個字節的前7位是否與它們在START條件(S)之后是相同的,并測試第八位(R/W)是否為1。 如果有匹配,從設備認為它被作為一個發送器尋址,并產生確認A3。從發送器保持尋址狀態,直到它接收到一個STOP條件§或接收到另一個重復的START條件(Sr)后跟隨一個不同的從地址。在重復的START條件(Sr)之后,所有其他從設備也將比較從地址(1111 0XX)的第一個字節的前7位與它們自己的地址,并測試第八位(R/W)。 然而,它們中沒有一個被尋址,因為R/W=1(10位設備),或者1111 0XX從地址(7位設備)不匹配。

具有10位尋址的從設備對“通用調用”的反應與具有7位尋址的從設備相同。硬件主設備可以在“通用調用”后傳輸其10位地址。在這種情況下,“通用調用”地址字節后面跟著兩個連續的字節,其中包含主發送器的10位地址。格式如圖15所示,第一個數據字節包含主地址的最低有效位8位。

開始字節0000 0001 (01h)可以以與7位地址相同的方式出現在10位地址之前。

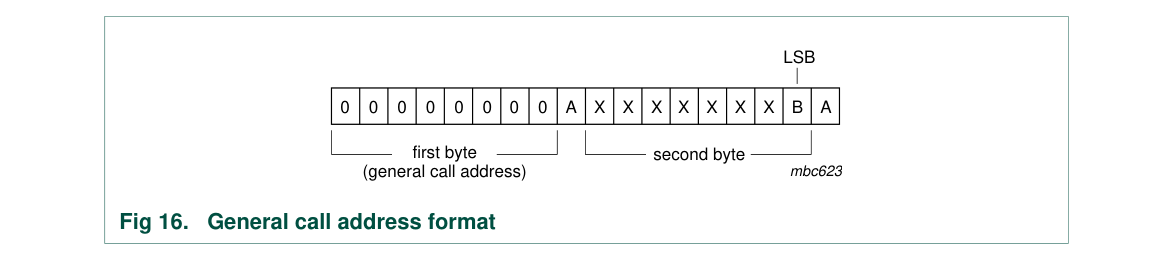

通用調用地址

通用調用地址用于同時尋址連接到I2C總線的每個設備。然而,如果一個設備不需要通用調用結構中提供的任何數據,它可以通過不發出確認來忽略這個地址。如果一個設備確實需要來自通用調用地址的數據,它會確認這個地址并表現為從接收器。如果一個或多個設備響應,主設備實際上不知道有多少設備確認。第二個字節和后續字節被每一個能夠處理此數據的從接收器確認。一個不能處理這些字節之一的從設備必須通過不確認來忽略它。同樣,如果一個或多個從設備確認,主設備將不會看到不確認。通用調用地址的含義總是在第二個字節中指定(見圖16)。

有兩種情況需要考慮:

當最低有效位B為“0”時。

當最低有效位B為“1”時。

當位B為“0”時,第二個字節有以下定義:

0000 0110 (06h):硬件復位并寫入從地址的可編程部分。在接收到這個2字節序列時,所有設計用于響應通用調用地址的設備都復位并接收其地址的可編程部分。

必須采取預防措施,以確保設備在施加電源電壓后沒有拉下SDA或SCL線,因為這些低電平會阻塞總線。

0000 0100 (04h):硬件寫入從地址的可編程部分。 行為與上述相同,但設備不復位。

0000 0000 (00h):此代碼不允許用作第二個字節。

編程過程的序列在適當的設備數據表中公布。其余代碼尚未固定,設備必須忽略它們。

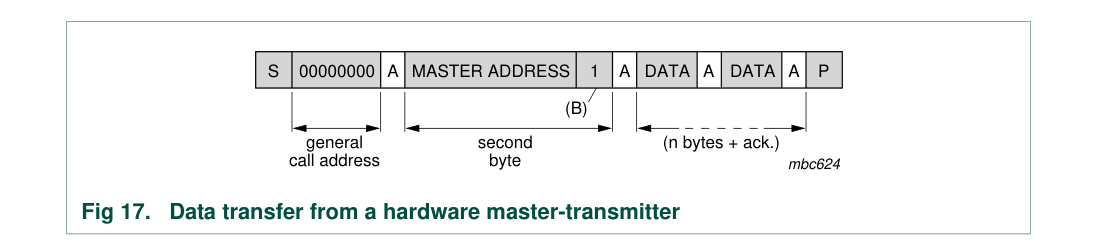

當位B為“1”時,2字節序列是“硬件通用調用”。這意味著該序列由硬件主設備傳輸,例如鍵盤掃描器,

它可以被編程來傳輸所需的從地址。由于硬件主設備事先并不知道消息必須被傳輸到哪個設備,它只能生成這個硬件通用調用和它自己的地址 — 向系統標識它自己(參見圖 17)。

第二個字節中剩下的七位包含硬件主機的地址。

這個地址被連接到總線的智能設備(例如,微控制器)識別,然后接受來自硬件主機的信息。如果硬件主機也可以充當從機,從機地址與主機地址相同。

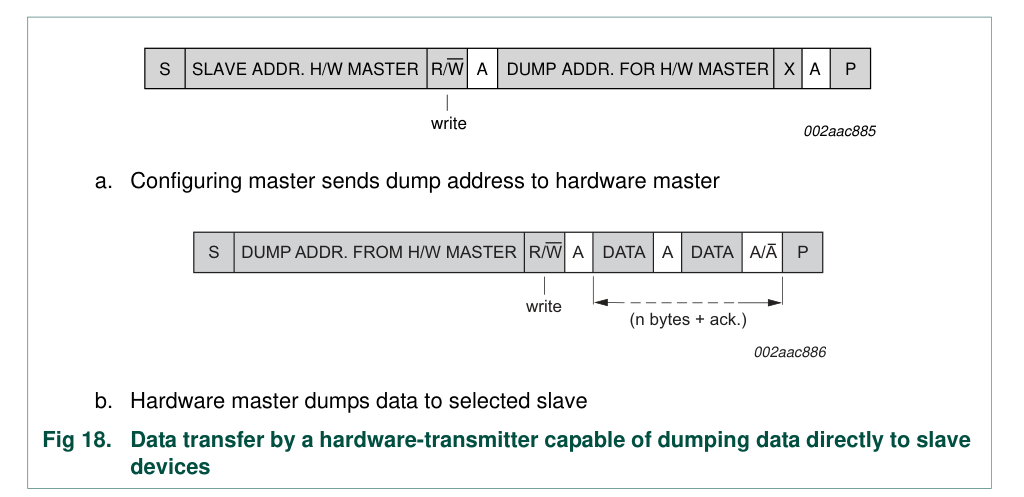

在某些系統中,另一種方法是將硬件主發射機在系統復位后設置為從接收機模式。這樣,系統配置主可以告訴硬件主發射機(現在處于從接收機模式)必須發送數據到哪個地址(見圖18)。在編程程序之后,硬件主保持在主發射機模式。

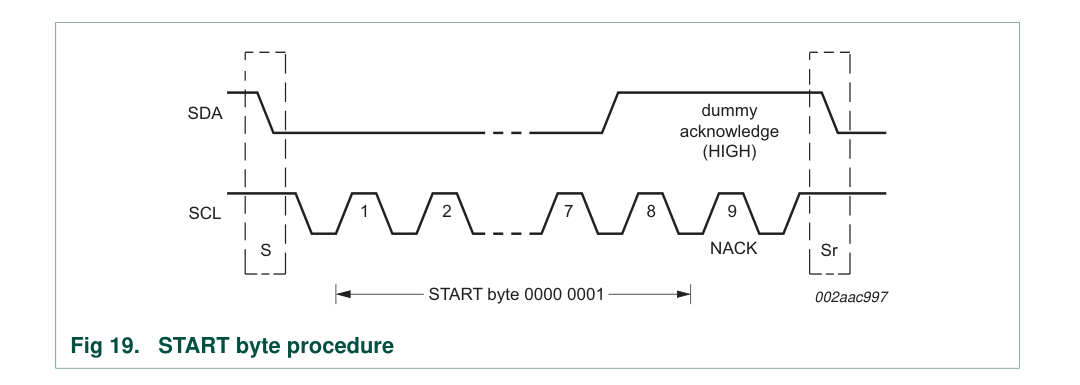

開始字節

微控制器可以以兩種方式連接到I2C總線。帶有片上硬件I2C總線接口的微控制器可以被編程為只被總線請求中斷。當設備沒有這樣的接口時,它必須通過軟件不斷地監視總線。顯然,微控制器監視或輪詢總線的次數越多,它執行預定功能的時間就越少。

因此,在快速的硬件設備和相對較慢的依賴于軟件輪詢的微控制器之間存在速度差異。

在這種情況下,數據傳輸可以先由一個比正常情況長得多的啟動過程(見圖19)。啟動過程包括:

一個開始條件(S)

一個開始字節(0000 0001)

一個確認時鐘脈沖(ACK)

一個重復的開始條件(Sr)

在需要總線訪問的主機傳輸了START條件S之后,

傳輸START字節(0000 0001)。另一個微控制器因此可以以低采樣率對SDA線進行采樣,直到檢測到START字節中的7個零之一。在檢測到SDA線上的LOW電平后,微控制器可以切換到更高的采樣率,以找到重復的START條件Sr,然后用于同步。

硬件接收器在接收到重復的START條件Sr后重置,因此忽略START字節。

在START字節后生成一個與確認相關的時鐘脈沖。這只是為了符合總線上使用的字節處理格式。不允許任何設備確認START字節。

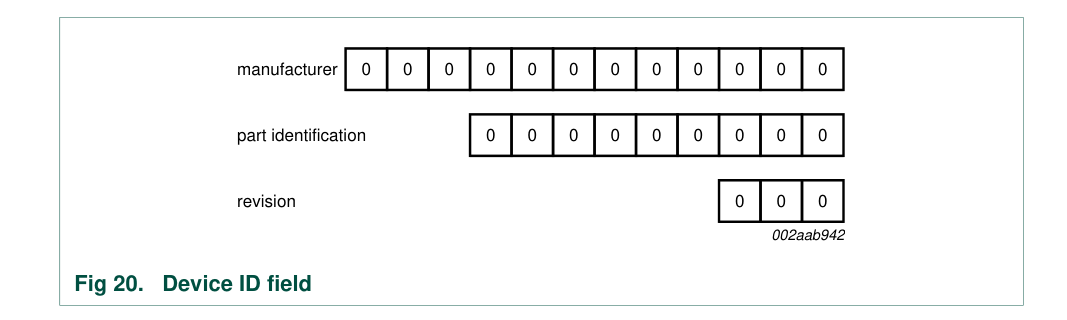

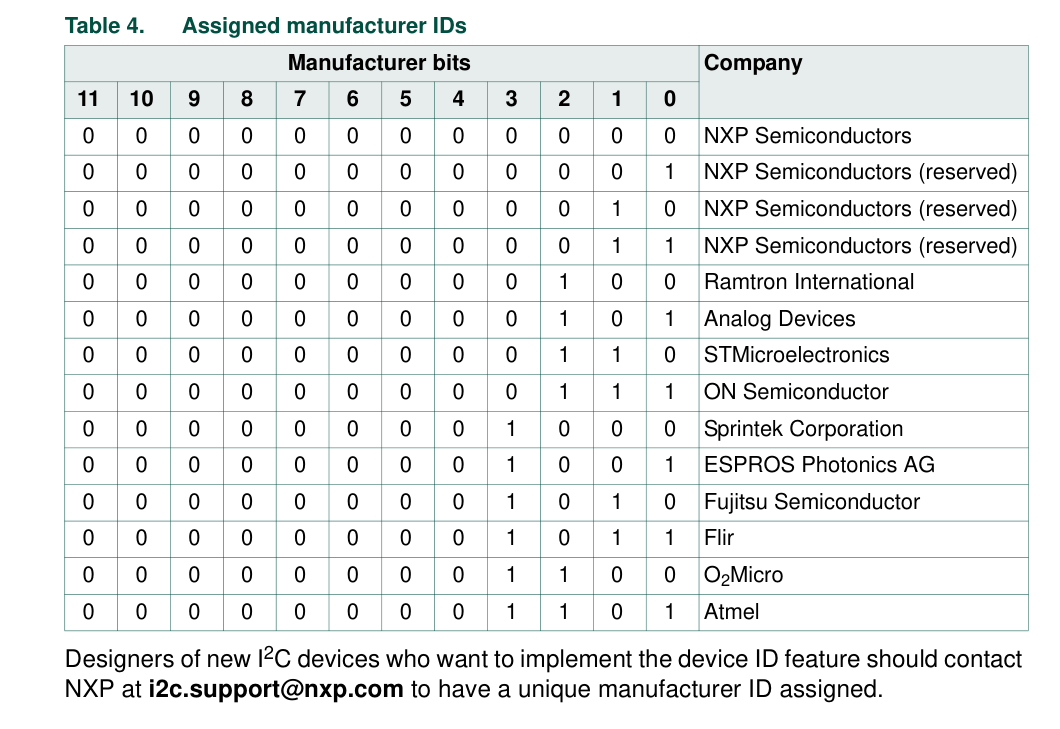

設備ID

設備ID字段(見圖20)是一個可選的3字節只讀(24位)字,提供以下信息:

12位制造商名稱,每個制造商(例如NXP)都是唯一的

9位部件標識,由制造商指定(例如PCA9698)

3位模具修訂,由制造商指定(例如RevX)

設備ID是只讀的,硬連接在設備中,可以按如下方式訪問:

START 條件

主控器發送保留設備ID I2C總線地址,后面跟著設置為‘0’的R/W位(寫入):“1111 1000”。

主設備發送它必須識別的從設備的I2C總線從地址。LSB是一個“不關心”的值。只有一個設備必須確認這個字節(具有I2C總線從地址的設備)。

主設備發送一個Re-START條件。

備注:一個STOP條件跟隨一個START條件重置從設備的狀態機,設備ID讀取無法執行。同樣,一個STOP條件或一個Re-START條件跟隨訪問另一個從設備重置從設備的狀態機,設備ID讀取無法執行。

主控器發送保留設備ID I2C總線地址,后面跟著設置為‘1’的R/W位:‘1111 1001’。

設備ID讀取可以完成,從12個制造商位(第一個字節+第二個字節的四個MSB)開始,接下來是9個部件識別位(第二個字節的四個LSB+第三個字節的五個MSB),然后是三個模具修正位(第三個字節的三個LSB)。

主設備通過ACK最后一個字節結束讀取序列,從而重置從設備的狀態機并允許主設備發送STOP條件。

備注:設備ID的讀取可以通過發送一個ACK在任何時候停止。

如果主設備繼續ACK第三個字節后的字節,從設備回滾到第一個字節并繼續發送設備ID序列,直到檢測到一個ACK。

04

I2C傳輸數據的格式

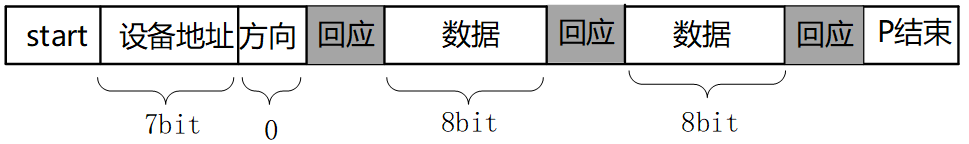

4.1 寫操作

流程如下:

主芯片要發出一個start信號

然后發出一個設備地址(用來確定是往哪一個芯片寫數據),方向(讀/寫,0表示寫,1表示讀)

從設備回應(用來確定這個設備是否存在),然后就可以傳輸數據

主設備發送一個字節數據給從設備,并等待回應

每傳輸一字節數據,接收方要有一個回應信號(確定數據是否接受完成),然后再傳輸下一個數據。

數據發送完之后,主芯片就會發送一個停止信號。

下圖:白色背景表示"主→從",灰色背景表示"從→主"

4.2 讀操作

流程如下:

主芯片要發出一個start信號

然后發出一個設備地址(用來確定是往哪一個芯片寫數據),方向(讀/寫,0表示寫,1表示讀)

從設備回應(用來確定這個設備是否存在),然后就可以傳輸數據

從設備發送一個字節數據給主設備,并等待回應

每傳輸一字節數據,接收方要有一個回應信號(確定數據是否接受完成),然后再傳輸下一個數據。

數據發送完之后,主芯片就會發送一個停止信號。

下圖:白色背景表示"主→從",灰色背景表示"從→主"

4.3 I2C信號

I2C協議中數據傳輸的單位是字節,也就是8位。但是要用到9個時鐘:前面8個時鐘用來傳輸8數據,第9個時鐘用來傳輸回應信號。傳輸時,先傳輸最高位(MSB)。

開始信號(S):SCL為高電平時,SDA山高電平向低電平跳變,開始傳送數據。

結束信號(P):SCL為高電平時,SDA由低電平向高電平跳變,結束傳送數據。

響應信號(ACK):接收器在接收到8位數據后,在第9個時鐘周期,拉低SDA

SDA上傳輸的數據必須在SCL為高電平期間保持穩定,SDA上的數據只能在SCL為低電平期間變化

I2C協議信號如下:

4.4 協議細節

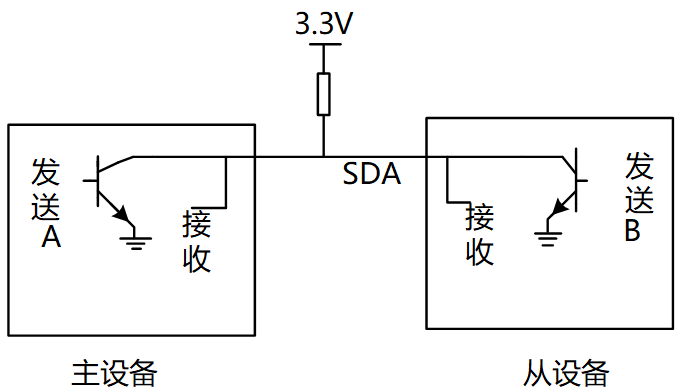

如何在SDA上實現雙向傳輸?

主芯片通過一根SDA線既可以把數據發給從設備,也可以從SDA上讀取數據,連接SDA線的引腳里面必然有兩個引腳(發送引腳/接受引腳)。

主、從設備都可以通過SDA發送數據,肯定不能同時發送數據,怎么錯開時間?

在9個時鐘里,

前8個時鐘由主設備發送數據的話,第9個時鐘就由從設備發送數據;

前8個時鐘由從設備發送數據的話,第9個時鐘就由主設備發送數據。

雙方設備中,某個設備發送數據時,另一方怎樣才能不影響SDA上的數據?

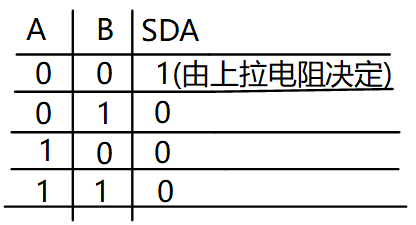

設備的SDA中有一個三極管,使用開極/開漏電路(三極管是開極,CMOS管是開漏,作用一樣),如下圖:

真值表如下:

從真值表和電路圖我們可以知道:

當某一個芯片不想影響SDA線時,那就不驅動這個三極管

想讓SDA輸出高電平,雙方都不驅動三極管(SDA通過上拉電阻變為高電平)

想讓SDA輸出低電平,就驅動三極管

4.5 示例:主設備發送(8bit)給從設備

從下面的例子可以看看數據是怎么傳的(實現雙向傳輸)。

舉例:主設備發送(8bit)給從設備

前8個clk

從設備不要影響SDA,從設備不驅動三極管

主設備決定數據,主設備要發送1時不驅動三極管,要發送0時驅動三極管

第9個clk,由從設備決定數據

主設備不驅動三極管

從設備決定數據,要發出回應信號的話,就驅動三極管讓SDA變為0

從這里也可以知道ACK信號是低電平

從上面的例子,就可以知道怎樣在一條線上實現雙向傳輸,這就是SDA上要使用上拉電阻的原因。

4.6 為何SCL也要使用上拉電阻?

在第9個時鐘之后,如果有某一方需要更多的時間來處理數據,它可以一直驅動三極管把SCL拉低。

當SCL為低電平時候,大家都不應該使用IIC總線,只有當SCL從低電平變為高電平的時候,IIC總線才能被使用。

當它就緒后,就可以不再驅動三極管,這是上拉電阻把SCL變為高電平,其他設備就可以繼續使用I2C總線了。

對于IIC協議它只能規定怎么傳輸數據,數據是什么含義由從設備決定。

05

I2C通信的高級應用

在嵌入式系統設計中,I2C應用廣泛,如:

5.1 傳感器網絡

在多傳感器系統中,I2C用于讀取各種環境參數,如溫度、濕度、光照強度等。這些數據可以被用于自動化控制系統或數據監測。

5.2 多設備控制

在復雜的嵌入式系統中,如機器人或無人機,I2C用于控制和監測多個執行器和傳感器,實現精確的運動控制和環境反饋。

5.3 嵌入式通信網絡

I2C也常用于建立微控制器和各種外圍設備(如顯示屏、存儲設備等)之間的通信網絡。

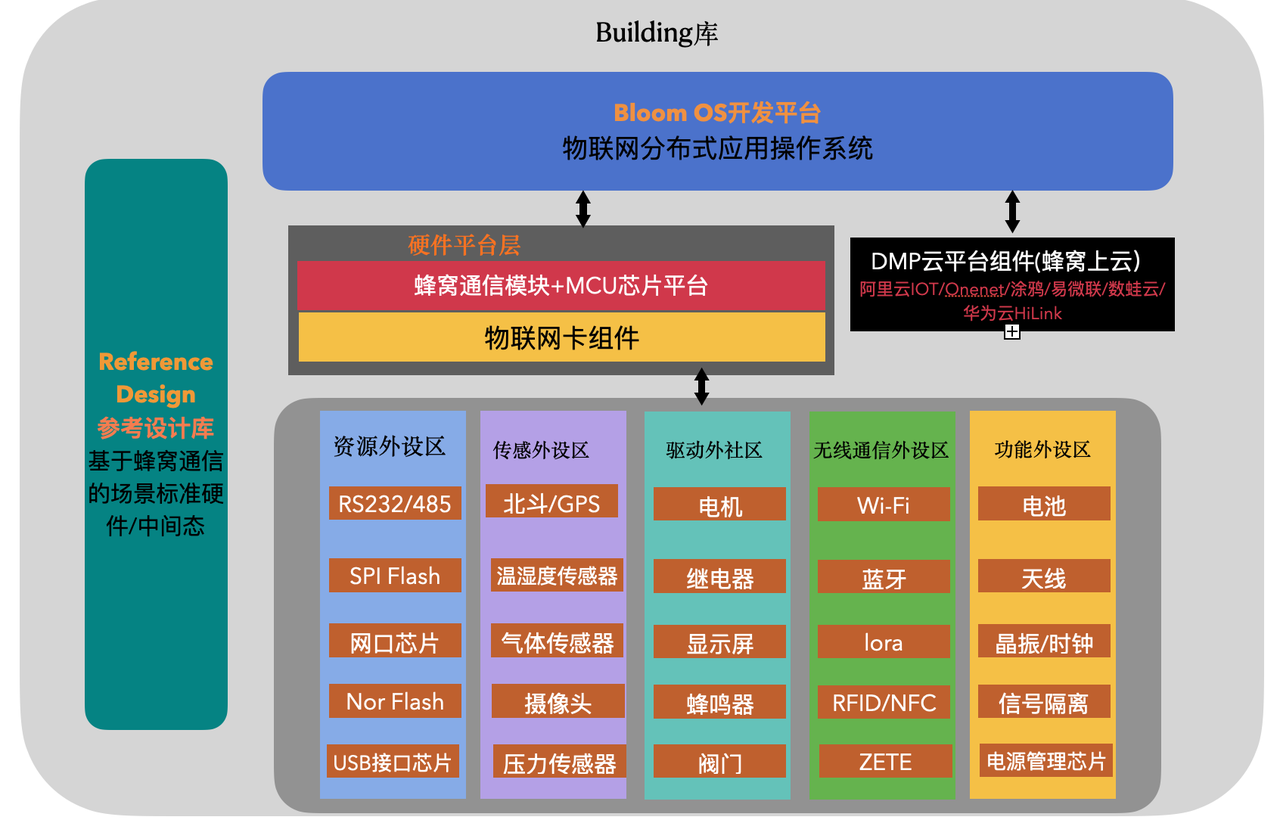

本文章源自奇跡物聯開源的物聯網應用知識庫Cellular IoT Wiki,更多技術干貨歡迎關注收藏Wiki:Cellular IoT Wiki 知識庫(https://rckrv97mzx.feishu.cn/wiki/wikcnBvAC9WOkEYG5CLqGwm6PHf)

歡迎同學們走進AmazIOT知識庫的世界!

這里是為物聯網人構建的技術應用百科,以便幫助你更快更簡單的開發物聯網產品。

Cellular IoT Wiki初心:

在我們長期投身于蜂窩物聯網 ODM/OEM 解決方案的實踐過程中,一直被物聯網技術碎片化與產業資源碎片化的問題所困擾。從產品定義、芯片選型,到軟硬件研發和測試,物聯網技術的碎片化以及產業資源的碎片化,始終對團隊的產品開發交付質量和效率形成制約。為了減少因物聯網碎片化而帶來的重復開發工作,我們著手對物聯網開發中高頻應用的技術知識進行沉淀管理,并基于 Bloom OS 搭建了不同平臺的 RTOS 應用生態。后來我們發現,很多物聯網產品開發團隊都面臨著相似的困擾,于是,我們決定向全體物聯網行業開發者開放奇跡物聯內部沉淀的應用技術知識庫 Wiki,期望能為更多物聯網產品開發者減輕一些重復造輪子的負擔。

Cellular IoT Wiki沉淀的技術內容方向如下:

奇跡物聯的業務服務范圍:基于自研的NB-IoT、Cat1、Cat4等物聯網模組,為客戶物聯網ODM/OEM解決方案服務。我們的研發技術中心在石家莊,PCBA生產基地分布在深圳、石家莊、北京三個工廠,滿足不同區域&不同量產規模&不同產品開發階段的生產制造任務。跟傳統PCBA工廠最大的區別是我們只服務物聯網行業客戶。

連接我們,和10000+物聯網開發者一起降低技術和成本門檻

讓蜂窩物聯網應用更簡單~~

哈哈你終于滑到最重要的模塊了,

千萬不!要!劃!走!忍住沖動!~

歡迎加入飛書“開源技術交流群”,隨時找到我們哦~

點擊鏈接如何加入奇跡物聯技術話題群(https://rckrv97mzx.feishu.cn/docx/Xskpd1cFQo7hu9x5EuicbsjTnTf)可以獲取加入技術話題群攻略

Hey 物聯網從業者,

你是否有了解過奇跡物聯的官方公眾號“eSIM物聯工場”呢?

這里是奇跡物聯的物聯網應用技術開源wiki主陣地,歡迎關注公眾號,不迷路~

及時獲得最新物聯網應用技術沉淀發布

審核編輯 黃宇

-

物聯網

+關注

關注

2909文章

44557瀏覽量

372757 -

總線

+關注

關注

10文章

2878瀏覽量

88051 -

I2C

+關注

關注

28文章

1484瀏覽量

123619 -

通信總線

+關注

關注

0文章

44瀏覽量

9853

發布評論請先 登錄

相關推薦

為什么嵌入式調試經常用UART,卻很少用SPI、I2C或USRT?

嵌入式常用總線有哪些

I2C總線協議的工作原理和尋址格式

SPI和I2C通信協議:應用與區別

什么是I2C協議 I2C總線的控制邏輯

物聯網嵌入式軟件中的I2C總線設計詳解

物聯網嵌入式軟件中的I2C總線設計詳解

評論