現在做電源,除了效率以外,空載或者待機功耗也變得越來越重要了。這不僅是因為各種各樣的能效標準的執行,也確實很符合實際應用的需求,因為大部分的用電設備都長期工作在待機狀態。以離線式的AC/DC電源為例,不同的應用要求不一樣,有500mW、300mW、再到100mW,甚至是很多充電器所追求的10mW以下。

實際上把待機功耗做低也不是什么太高深的事兒,不需要高等數學頻譜分析什么高大上的理論,基本只是需要一些經驗,有時要做些妥協。這里就把和大家分享一些本人的淺見。

先從AC輸入端說起, 這里最大的損耗就來自于X電容放電的電阻。大部分的安規標準都要求1s內把X電容的電壓放到安全電壓以下。這樣容值越大,放電的電阻就越小,損耗也就越大。舉個例子,.33uF的電容并個3M的電阻,230Vac條件下的空載損耗就有~18mW。

也就是說為了節約這部分功耗,X電容要盡量小,這個節約成本倒也是一致的。但是必要的情況下,為了降低損耗也不得不多花點錢了,也就是用專門的X電容放電芯片,比如CAPZero或者HF81。這類芯片可以 自動檢測AC是否掉電,所以在正常工作的時候幾乎沒有損耗。這類芯片放在橋前面都需要有相應的安規認證的,也都是比較可靠的。

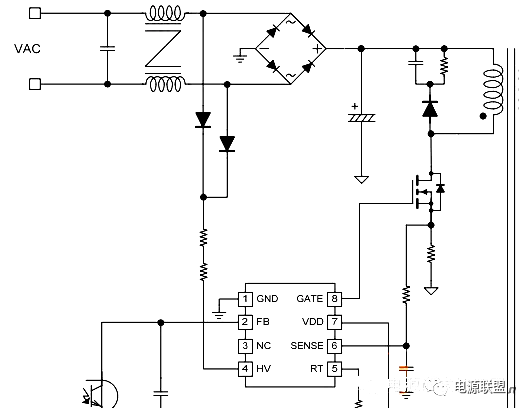

也有一些吧這個功能集成到主控芯片里面的,比如FAN6756。有一個HV腳通過兩個二極管直接接到AC,同時實現X電容放電和啟機的功能。

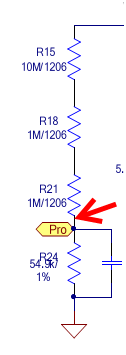

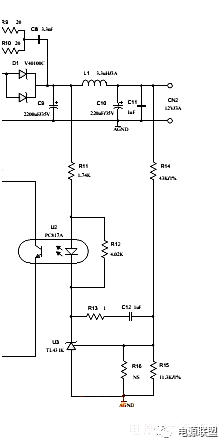

雖然沒這么做過,但據說是可行的。個人感覺這個管子要注意兩點,一是要足夠的耐壓;二是要放在信號的上端以防后端芯片過壓,(圖中紅色箭頭位置),為了做到這一點就要有個足夠高的驅動電壓。

接著說整流橋的后面。在母線上會有很多高壓器件,所以需要特別注意漏電。300V的母線每10uA就產生3mW的損耗。

半導體器件一般來說都還好,像整流橋、MOSFET,關斷時的漏電基本都在1uA以下。高溫情況下會大得多,但是空載損耗基本也只看常溫條件,沒有負載電路本身也沒什么熱量產生。

電解電容的漏電在有些情況下就不能忽略了,電容越大漏電越強,基本上是和CV成正比關系的。而且電容的質量參差不齊,質量差的電容漏電要大好幾倍。可以測試一下如果達到10uA這個數量級了使用的時候就要小心一些了。

對了,如果是比較老的或者低成本的開關電源芯片,還有一組啟動電阻掛在高壓母線上,用來提供啟機的初始電流,正常工作后一般由輔助繞組供電,啟動電阻就沒有用了,但是功耗還在那里。

現在內置高壓啟動電流源的芯片都不新鮮了,沒必要舉例。還用電阻做啟動的話那是明顯沒有把待機功耗做低的誠意了。

今天主攻電源芯片

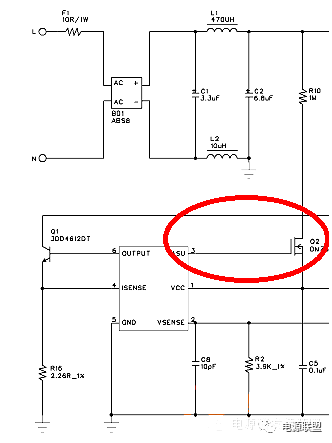

前面已經提過了,有意做低待機功耗,至少要先一個有內置高壓啟動電流源的控制芯片。如果真沒有的話,也至少要外搭一個。 一些沒有高壓引腳的芯片也提供一個控制引腳來連接外置的高壓開關管。這樣就是BOM復雜一點。

芯片本身的功耗是Icc*Vcc/?。 Icc是工作電流,Vcc是工作電壓,?是轉換效率。因為芯片穩定工作的工作電壓一般都來自輔助繞組,所以?取決于開關頻率和功率電路的設計,后面也會陸續提到影響轉換效率的一些因素。

就目前看到的水平,AC/DC類的功能電源芯片,只要功能不是特別復雜的,Icc都應該能做到百uA這個數量級。只有一些很復雜的芯片,比如PFC+LLC combo這種,或是大功率電源中所采用的數字芯片耗電才會在mA級別。特別大功率的電源有時會采樣輔助電源的方式來節約待機功耗。

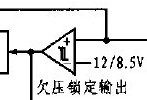

Vcc則是取決于輔助繞組的設計。為了是芯片功耗最小化,設計的時候當然應采用盡量低的供電電壓。只是要注意輔助繞組提供的電源一般會隨著負載減輕而降低。必須保證Vcc在空載條件下也能保持在最低工作電壓以上。

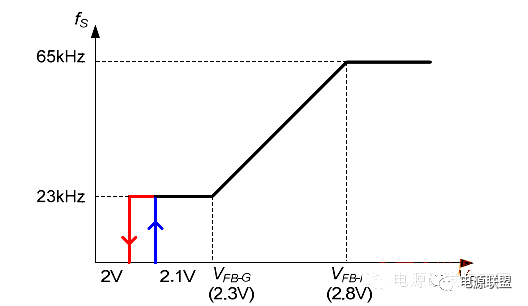

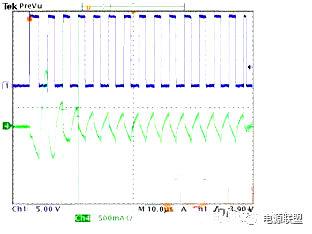

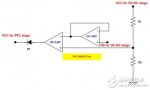

芯片的控制方式可以說是決定待機功耗最重要的一環。相信大家都清楚,輕載或空載狀態下,開關損耗在轉換效率中占主導地位。所以為了降低待機功耗,大部分電源芯片都采取載輕降頻的控制方式。以中小功率常用的反激電源為例,現在比較流行的一種復合控制模式如下,重載時采用PWM,隨著負載減輕頻率下降,在接近空載的區域采用Burst的工作模式進一步降低開關頻率。

這種控制方式在實際應用中有一個矛盾需要考慮。理論上來說保持最大的ipk可以再空載狀態下獲得最低的開關頻率(1/2 *Lm*ipk^2*fs)。但開關頻率在20kHz一下就會有噪音的問題,從這個角度來看就需要ipk越小越好。因此在實際應用的時候就需要找到最佳的折衷設計了。

實際上Burst的方式也有一些細節是值得注意的。每隔100ms連出10個開關和每10ms出一個開關,看起來平均頻率是一樣的,但轉換效率會不會有差別呢?仔細考慮還是會有一寫區別的。比如反激電源中,有RCD鉗位電路中的能量每次Burst都是充滿再放光的,這樣的話連出的開關數多一點會比較好。

LLC的情況會不一樣,因為LLC的Burst基本前一兩個周期把能量已經都輸出來了,后面再開關基本上只剩勵磁電流了,換句話說后面出的開關都是在做無用功,除了產生開關損耗外沒干別的。這樣就是連出的開關數少一點會比較好。

原邊反饋和副邊反饋的芯片在待機功耗上的表現也是有所區別的。大家都知道原邊反饋的好處是省了光耦和TL431,但可以說還有一個附贈的禮品就是降低了空載損耗,因為光耦和TL431也都不是省油的燈。

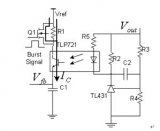

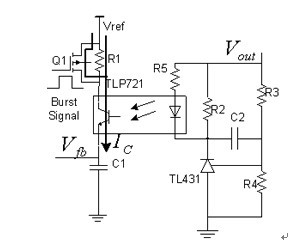

這里是一個典型的副邊反饋的配置,空載狀態下典型的偏置電流都在500uA-1mA之間,那么假設副邊和輔助繞組的供電都是12V的話,這里就產生了10-20mW的損耗。哦,別忘了還要考慮轉換效率

有人減小偏置電流來降低這部分損耗,但是別忘了,滿載時的偏置電流空載時還要小很多。這樣做可能會影響整個的環路性能甚至失調。

再談談一些周邊輔助電路設計的影響。

RCD是比較常用的吸收電路,主要是吸收漏感的能量以限制開關管上的尖峰電壓。相信大家都清楚,RCD如果做的太強的話會對效率有很明顯的影響,那自然也會影響輕載效率和待機功耗。如果考慮到待機狀態下電源都是工作在極低頻率的Burst狀態下的話,實際上C的大小對待機功耗的影響比R要大得多,因為每次C都會充滿再放光的。這部分能量就像一個假負載掛在那里 一樣

從這個角度出發,有一種做法是把C徹底拿掉,用一個TVS來代替,這樣就拿掉了這個“假負載”。

在多路輸出的應用里面還有一些小手段可以減小待機功耗的,之前提到過作反饋用的光耦和431的損耗,這里再補充一點。在多路繞組輸出的應用里面,光耦和431的偏置電流應該取自電壓最低的那一路,(當然是在不影響反饋性能的前提下),這樣可以非常明顯的節約待機功耗。

有一種在家電、智能家居應用中非常常見的兩路輸出的結構,是基于LDO的。一般比較高的電壓是18V、12V等供風扇、繼電器或者背光的,再通過一個LDO提供穩定的5V或3.3V給MCU。因為風扇、繼電器這些基本上在待機狀態下都是不用的,那么就可以用MCU提供一個待機信號,把18V、12V降到5-6V只要能保持MCU正常工作就行了。這個是從系統的角度出發來實現節約的。

-

電源

+關注

關注

185文章

17953瀏覽量

252753 -

開關電源

+關注

關注

6478文章

8405瀏覽量

484857 -

功耗

+關注

關注

1文章

828瀏覽量

32205

原文標題:深入分析開關電源的待機功耗

文章出處:【微信號:Power-union,微信公眾號:電源聯盟】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何降低LED照明開關電源待機功耗

怎么提高開關電源的待機效率

【技巧分享】降低開關電源的待機功耗

怎樣對開關電源進行環路分析?

低待機功耗開關電源充電器的設計

詳解如何實現開關電源待機低功耗

開關電源功耗分析和提高待機效率的方法

對開關電源的待機功耗的分析

對開關電源的待機功耗的分析

評論