隨著電子技術的發展,應用系統向小型化,快速化,大容量,重量輕的方向發展,電子設計自動化(ElectronicsDcsignAutomation)技術應運而生,他是電子產品及系統開發領域中一場革命性變革,也是高科技化發展的必然產物。主要應用于數字電路的設計,目前他在中國的應用多數是用在FPGA/CPLD/EPLD的設計中。系統為電子產品的開發,電子系統的設計,電子系統工程提供了高度集成的軟件環境,具有完整而自動的實現流程,直觀的沒計環境,龐大的模擬庫,簡單而優良的仿真功能等優勢。

1引言

搶答器在各種知識、智力競賽中有很大的用處,他能準確、公正、直觀地判斷出第一搶答者,并通過搶答器的指示燈顯示和警示蜂鳴等手段指示出第一搶答者。如今在很多的綜藝節目中,更多的采用大屏幕顯示搶答者,渲染出更加激烈的比賽氣氛,而且配合演播廳的整體效果,就要求搶答器也能提供多種接口,并拋棄傳統的長長的蜘蛛網似的開關引線。本文所介紹的是一種基于EDA技術的實用器系統的設計方案,他采用超大規模邏輯器件CPLD來處理搶答器的邏輯,通過上位微機來完成聲音和動畫等效果。該方案的優點在于:反應快、安裝簡單、覆蓋范圍廣、可擴展性強、使用效果更美觀等。

2系統構成

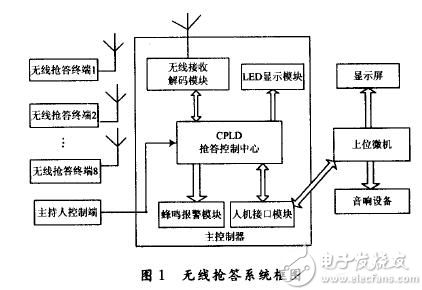

基于CPLD和無線編解碼發射接收技術的器系統的原理框圖如圖1所示,由8路終端、主控制器以及上位微機系統組成。

2.1無線搶答終端

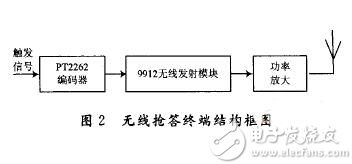

在本設計中,無線搶答終端主要包括編碼模塊、無線發射模塊和功率放大模塊,其內部結構框圖如圖2所示。

其中編碼模塊采用的是專用紅外遙控編碼芯片PT2262-IR,在主控制器端的無線解碼模塊采用的與其配對使用的解碼芯片PT2272,他們都是***普城公司生產的一種CMOS工藝制造的低功耗低價位通用編解碼電路,最多可有12位三態地址端管腳,任意組合可提供531441地址碼。PT2262最多可有6位(DO~D5)數據端管腳,設定的地址碼和數據碼從17腳串行輸出,非常適合用于無線遙控發射電路,其有效發射接收距離為80m,發射電路電源范圍為2-12V,接收電路電源范圍為4.8~5.0V,發射電路有效發射反應時間≤0.2ms.

無線發射接受模塊采用通用系列產品9912,在主控制器端的無線接收模塊采用的是9921,這樣不僅可以加快制作過程,而且還可以增加電路的穩定與可靠性。

2.2CPLD主控芯片

系統核心控制芯片采用的是Altera公司MAX7000S系列新一代CPLD器件EPM7128SLC84-15。該芯片采用CMOSE2PROM工藝,傳輸延遲僅為5ns;內部具有豐富的資源-128個觸發器、2500個用戶可編程門;而且具有68個用戶可編程的I/O接口,為系統定義輸人、輸出和雙向口提供了極大的方便;為了比較適合混合電壓系統,通過配置,輸人引腳可以兼容3.3V/5V邏輯電平,輸出可以配置為3.3V/5V邏輯電平輸出。EPM7128同時還提供了JTAG接口,可進行ISP編程,極大地方便了用戶。

新的CPLD芯片技術除了大大減少集成芯片的數目,便于對系統進行擴展,還可以縮短開發周期。降低開發成本,同時提高了技術保密性。與FPGA技術相比,CPLD有掉電不易失的優點,使用更加方便。

2.3人機接口電路

本系統中,主控制器與上位微機的通信采用RS232串行異步通信方式。由于CPLD主控芯片的輸出電平與RS232的電平不匹配,所以主控制器與上位微機的人機接口電路,主要選用采用Max232芯片的進行電平轉換。Max232是MAXIM公司生產的,包含兩路驅動器和接收器的RS232轉換芯片。芯片內部有一個電壓轉換器,可以把輸入的+5V電壓轉換為RS232接口所需的±10V電壓。

3軟件設計

本設計中的軟件由CPLD控制程序和土位機PC端的動態效果演示程序2部分組成。CPLD控制程序實現與無線接收解碼模塊的連接及完成與外圍模塊之間的數據轉換和通訊。上位機PC端的動態效果演示程序重點是完成基于VB的交互界面的設計。

3.1基于CPLD的核心控制程序

CPLD控制程序是本系統軟件設計的核心,他采用的是在美國Altera公司的Max+PlusII10.0平臺上用VHDI高級語言輸人設計方法。他有專用的工具來實現將語言描述過的電路功能轉換為實際的電路,具有很好的通用性和靈活性。他的主要功能:接收并保存無線接收解碼模塊傳送的搶答成功的終端的編碼并封鎖接收模塊,直至控制端復位;同時蜂鳴器奏響并在LED顯示搶答成功的終端編號;并完成CPLD與串行接口芯片的數據交換.

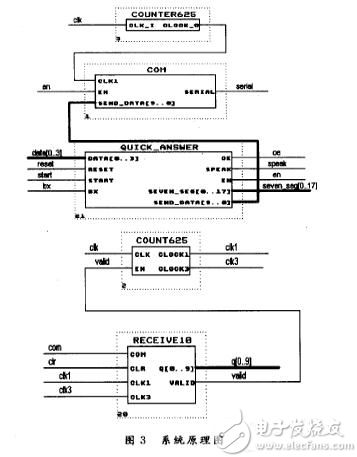

該控制程序主要包括4個功能子模塊:分頻模塊、搶答終端編碼接收模塊、串行發送模塊、串行接收模塊。在Max-f-PlusII10.0中設計輸人各個模塊的VHDL的程序后,生成庫器件并合成系統原理圖如圖3所示。以下簡要介紹搶答終端編碼接收模塊和串行發送模塊的程序設計。

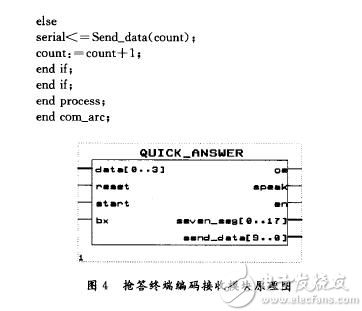

圖4為生成的該模塊原理圖,其VHDL源程序如下:

3.1.2串行發送模塊

如圖4所示,該模塊將搶答終端編碼接收模塊輸出的搶答終端的編碼按照串行異步通訊規則發送給人機接口電路。在串口通訊中,我們約定的幀格式為1位開始位+8位數據位+1位停止位,沒有校驗位,通訊波特率為9600。根據約定,該模塊輸出數據為10位,在發送完10位后,就停止發送,并使發送端電平處于邏輯1,然后等候下次的發送。其VHDL源程序如下:

3.2上位機PC端的演示程序

本軟件是在VB6.0環境下開發的,并利用其數據管理功能,建立比賽題庫并提供管理界面。其與主控制器之間的串行口通信設計部分充分利用了Mscomm串行口通信控件。由于該控件提供通過串口發送和接收數據的串行通信能力,包括了全部WindowsAPI中關于串行通信的16個函數所完成的功能,而且開拓了更多使用戶設計方便的對象屬性來滿足不同用戶不同業務的需求,因此給編程帶來極大的方便。

本軟件在PC環境下運行,包括以下幾個功能:根據設定自動抽出比賽題目、控制主控制器的工作、聲光效果顯示搶答終端編號并倒數計時、現場效果渲染等。詳細程序在此不再贅述。

4結語

經過反復試驗,該系統運行穩定,操作方便,達到了預期的設計效果,具有可操作性強、現場效果好的特點,已經在知識竟賽等相關活動中實際使用。

-

cpld

+關注

關注

32文章

1248瀏覽量

169355 -

eda

+關注

關注

71文章

2758瀏覽量

173253

發布評論請先 登錄

相關推薦

eda的常見誤區和解決方案

EDA在物聯網設計中的應用

是德科技攜手西門子EDA加速無線和國防通信系統設計

是德科技與西門子EDA深化合作,共促無線與國防通信系統設計

AMD Embedded+架構助力Concurrent EDA打造機器視覺系統

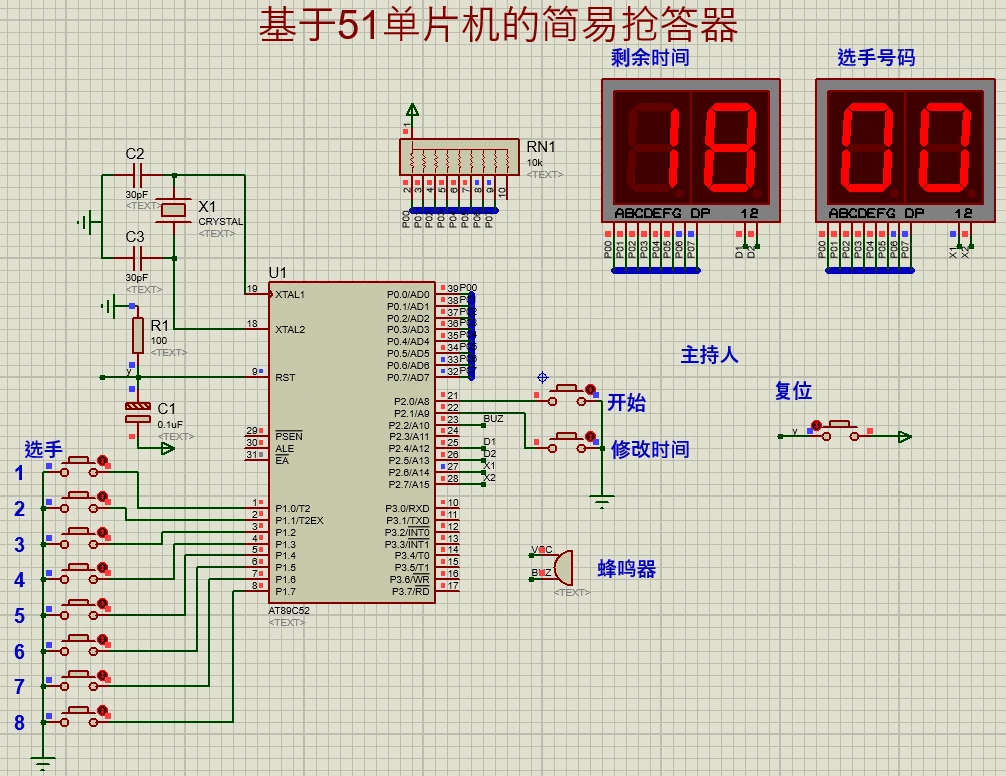

基于51單片機的簡易搶答器

LoRa技術農田自動無線智能灌溉系統

農業無線灌溉系統方案

三星已開始使用AI技術設計半導體

基于51單片機的多路搶答器的設計與制作,電路,程序,原理圖,論文

芯片設計及使用的EDA工具介紹

R&S基于Analog Devices的技術打造無線電池管理系統生產測試解決方案

巧用EDA技術設計無線搶答系統方案

巧用EDA技術設計無線搶答系統方案

評論