在芯片設計中,我們常用PPA(Power, Performance, Area)來衡量一塊芯片的指標。Performace直接取決于Timing參數。由此可見,時序設計在后端設計中占有舉足輕重的地位。那今天我們就來介紹下,時序分析中的最重要概念——STA。

我們現在生活中其實存在著不少時序問題,比如以下兩個例子:

?我打電話給張三,李四卻接了電話

這就代表著數據傳輸過程中出現問題,導致芯片不工作

?我想要一輛法拉利,你卻給我的是裝著QQ引擎的法拉利

這就代表著芯片沒有工作在正常的頻率之下

同樣在芯片設計過程中,存在著很多時序的違例。這就需要我們在設計中去驗證時序的正確與否。

通常,我們有以下兩種驗證方法:

(1) 動態時序分析(Dynamic timing simulation)

(2) 靜態時序分析(Static Timing Analysis, 簡稱STA)

動態時序分析,主要是通過輸入向量作為激勵,來驗證整個設計的時序功能。動態時序分析的精確與否取決于輸入激勵的覆蓋率,它最大的缺點就是速度非常慢,通常百萬門的設計想全部覆蓋測試的話,時間就是按月來計算了。

而靜態時序分析呢?

Static timing Analysis is a method for determining if a circuit meets timing constraints without having to simulate clock cycles.

翻成中文的話: 套用特定的時序模型(Timing Model),針對特定電路分析其是否違反設計者給定的時序限制(Timing Constraint)。

和動態時序分析相比,它不需要輸入激勵,因此速度會很快,并且它是Path Based分析,采用窮舉型邏輯,如下圖所示,理論上能分析到所有同步邏輯是否違反約束。

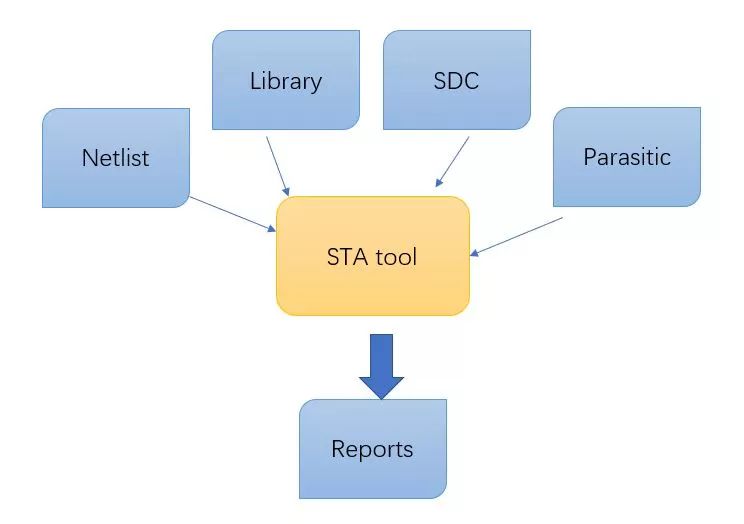

那么如何去做STA,需要準備些什么文件呢?簡單的可以用下圖表示:

我們需要準備設計的libarary data (包括cell的lib和operating condition等等),Timing constraints(包括clock的描述,design boundry的約束等其他sdc),Gate-level-netlist,sdf/spef等rc信息文件; 然后需要指定時序分析模式,最后會產生設計中的詳細時序分析報告。

-

時序分析

+關注

關注

2文章

127瀏覽量

23817 -

STA

+關注

關注

0文章

52瀏覽量

19309

原文標題:時序分析基本概念介紹——STA概述

文章出處:【微信號:IC_Physical_Design,微信公眾號:數字后端IC芯片設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

簡析Modbus與MQTT的區別

群延遲的基本概念和仿真實例分析

暨南大學選購我司HS-STA-001同步熱分析儀

長沙醫學院選購我司HS-STA-002同步熱分析儀

集成電路設計中靜態時序分析介紹

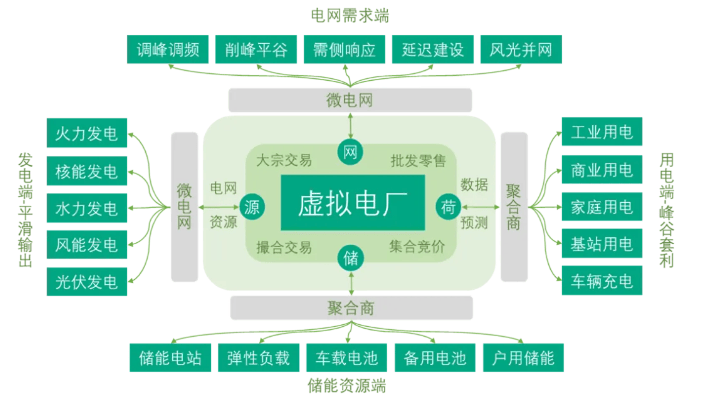

了解虛擬電廠的基本概念

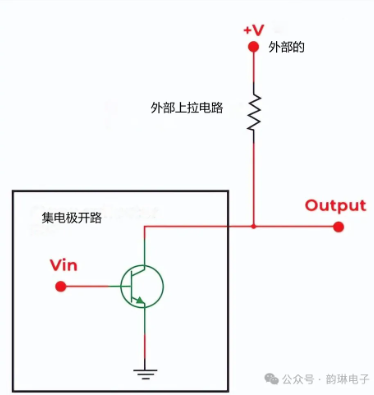

集電極開路的基本概念與原理

時序邏輯電路的基本概念、組成、分類及設計方法

時序邏輯電路的功能表示方法有哪些

伺服系統基本概念和與變頻的關系

socket的基本概念和原理

鎮江安恬新材料有限公司選購我司HS-STA-002同步熱分析儀

評論