摘要:隨著集成電路密度的不斷提高,多晶硅柵的線寬不斷變小,柵氧化層的厚度繼續變薄,多晶硅的刻蝕變得越來越關鍵。多晶硅柵的形貌控制,柵氧化層二氧化硅的損失等關鍵特征已經被普遍關注。多晶硅刻蝕中的另一種現象:微溝槽缺陷(microtrench defect)也顯得越發重要。該現象會造成器件的大面積漏電,嚴重殺傷每一個管芯,造成硅片的報廢。作者通過相關試驗,從工藝參數的角度對微溝槽缺陷的形成和控制做了討論,對主要工藝參數對微溝槽缺陷的影響作了分組實驗,為優化工藝參數來徹底防止微溝槽缺陷提供必要的指導。

1 引言

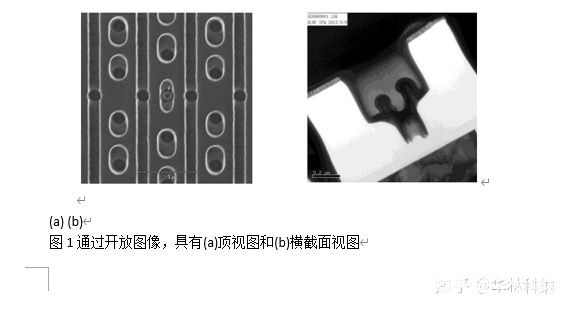

多晶硅刻蝕在集成電路芯片制造工藝中有著至關重要的作用,線寬和形貌的控制非常重要,也被大家普遍關注。但微溝槽缺陷(圖 1,微溝槽缺陷的截面圖)現象容易被忽視,因為通常的目檢,鏡檢不易發現該缺陷[1-3]。但微溝槽缺陷對器件性能有致命影響,一旦形成器件漏電急劇加大,從而導致器件的各種失效[4]。微溝槽缺陷是在多晶刻蝕過程中,反應離子撞擊下層柵氧化層,造成柵氧化層局部被擊穿,在硅襯底上形成一個溝槽。由于其非常小,直徑只有0.05~0.2 μm,深度只有 2 000~5 000 A,所以稱之為微溝槽缺陷[5,6]。該缺陷在 0.35 μm 或以下線寬的技術中極易形成,主要是因為柵氧化層薄(小于 50 A), 較難阻擋離子的撞擊。所以就有必要對刻蝕工藝的菜單進行優化,在取得垂直形貌的同時,也要尋找合適的工藝窗口,開發強大的工藝菜單,將微溝槽缺陷徹底消滅。

在實際生產中,多晶硅刻蝕的主流設備是反應離子刻蝕設備,且都具備獨立可調的兩組 RF 功率即源功率和偏壓功率,都使用氯氣和溴化氫氣體作為主刻蝕氣體,同時還有調節選擇比的氧氣和氦氣混合氣體。本次實驗,我們在主刻蝕工藝步驟(終點監測步驟),對主要工藝參數:腔體壓力,源功率,偏壓功率,氯氣/溴化氫氣體比率這四個參數進行大范圍的調整,用終點檢測方法刻蝕實驗片,通過掃描電鏡仔細觀察多晶硅邊緣的缺陷數量,來判斷該參數對微溝槽缺陷的影響,并對這一缺陷形成的原因進行了相應解釋,并提出了改善措施。

2 實驗

2.1 實驗條件

在多晶硅刻蝕的主刻蝕步驟,對腔體壓力,源功率(Source Power),偏壓功率(Bias power)和氯氣/溴化氫氣體的比率進行分別拉偏分組,實驗條件如下:

第 1 組,腔體壓力分組:3 mT,5 mT,10 mT,20 mT。

第 2 組,源功率分組:150 W,200 W,250 W,300 W。

第 3 組,偏壓功率分組:50 W,100 W,150 W,200 W

第 4 組,氯氣/溴化氫氣體比率分組: 25 / 75,33 / 66,50 / 50,66 / 33 (單位:SCCM)

附注:標準主刻蝕步驟的菜單為:腔體壓力 10 mT,源功率 200 W,偏壓功率 75W,氯氣/溴化氫氣體 33 / 66 SCCM,氧氣-氦氣 5 SCCM。終點監測:97%。

2.2 觀察結構

為了方便觀察刻蝕后的微溝槽缺陷程度,我們設計了一種特殊的圖形結構。

在 3.3 μm×3.3 μm 的正方形區域中,設計了多根線寬為 0.3 μm 的多晶線條(Line),其間距也為 0.3 μm (Space)。即 Line 和 Space 的比例為1:1,共六條 Line,5 個 Space。

用掃描電鏡觀察兩條多晶硅線條之間,在多晶硅邊緣是否有微溝槽缺陷。一般用 10 K~50 K 的倍率觀察,用 10 K 倍率尋找可疑點,用 50 K 倍率確認缺陷的存在。

2.3 多晶硅樣片制備

硅片表面清洗后,先生長一層 50 A 的熱氧氧化層,用 LPCVD 爐管淀積 3 000 A 多晶硅,DUV 光刻機曝光形成測試圖形供刻蝕使用。光刻膠的形貌必須符合要求,即垂直的形貌(大于 88 ℃)并且無任何底膜殘留。

2.4 缺陷程度

為了便于定性定量分析工藝參數與微溝槽缺陷數量的對應關系,我們對微溝槽缺陷的程度的描述做了如表 1。

3 實驗結果

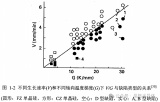

四組實驗的結果(詳見圖 2,圖 3,圖 4 和圖5)表明:

(1)腔體壓力變化對微溝槽缺陷現象的產生有著重大影響。從線段圖上可以看出隨著腔體壓力的減低,微溝槽缺陷現象越來越嚴重,在 3 mT 時,經常發現某些區域上許多微小的溝槽會逐漸連接結起來形成一條長溝槽(大于 0.5 μm),這說明微溝槽缺陷現象已經非常嚴重了。

(2)源功率的變化對微溝槽缺陷現象的產生幾乎沒有影響。在 150 W 到 300 W 范圍內沒有觀察到微溝槽缺陷,由于在實際應用中沒有必要使用大于 300 W 的源功率,所以沒有做進一步加大源功率的實驗。

(3)偏壓功率對微溝槽缺陷現象的產生有著重大影響。從線段圖上可以看出隨著偏壓功率的增加,當偏壓功率達到一定數值時,微溝槽缺陷越來越嚴重,微溝槽缺陷數量會急劇增加。

(4)氯氣/溴化氫氣體比率的變化對微溝槽缺陷影響不大,但氯氣上升太多,當氯氣/溴化氫氣體比率達到 2:1 比率時,也會形成中等數量的微溝槽缺陷。

4 微溝槽缺陷的形成機制與實驗結果分析

微溝槽缺陷的形成已經被普遍認為和反應離子的反射有關,圖 6 為簡單示意圖。在腔體中,反應離子向下撞擊,部分離子撞擊到多晶硅線條的側壁上,會反射到多晶硅的邊緣,造成局部區域的轟擊力特別強大,這些區域的柵氧化層會首先被擊穿,一旦氧化層被擊穿,反應離子迅速刻蝕硅襯底,形成微溝槽。顯而易見多晶硅下面的柵氧化層對微溝槽缺陷的形成起著阻擋和保護作用,只要柵氧化層足夠強大,足夠厚,就沒有機會形成微溝槽。但是柵氧化層的厚度是由器件的性能決定的,0.35 μm 技術一般柵氧化層的厚度在 50~60 A 左右,0.18 μm 技術在 20~30 A 左右,這個厚度不足以阻擋微溝槽缺陷的形成。

腔體內反應離子的反射是客觀存在的,在目前的條件下是無法避免的。但是反應離子要轟擊氧化層就需要能量,如果能量不夠大,在整個刻蝕時間內并不能擊穿氧化層,微溝槽缺陷也不能形成。

所以反應離子的能量對微溝槽缺陷的形成起著決定性的作用。能量越大,離子對柵氧化層的轟擊力也越大,造成氧化層局部被破壞的可能行就越大,就越容易形成微溝槽缺陷。

對上述四組試驗結果分析。

(1)腔體壓力的降低,反應離子的能量會顯著增加。在刻蝕腔體中有大量的離子存在,這些運動中的離子都有一定的能量(動能),由于這些離子在運動,它們之間會不斷地相互碰撞,碰撞會損失能量,最終導致撞擊多晶硅線條側壁的離子能量減低。

但是,隨著腔體壓力的降低,離子的平均自由程就變長。平均自由程長,離子間相互碰撞的幾率就降低,離子的能量損失就會大幅度減少。

所以,壓力越低,反應離子的能量就越大,柵氧化層就越容易被轟擊擊穿,微溝槽缺陷的程度就會顯著增加。

(2)源功率的變化主要影響反應離子的密度即單位體積內的反應離子的數量,不增加反應離子的能量。所以它的增加,對微溝槽缺陷數量的變化沒有貢獻,但源功率增加會小幅增加刻蝕的速率。

(3)偏壓功率變化對離子能量變化起著直接的作用。在反應離子刻蝕中,偏壓是負值,而反應離子是正電荷。由負偏壓產生的電場能顯著加快離子向下(向著硅片表面)的運動速度,使撞擊的力量顯著增強。所以反應離子的能量隨著偏壓功率的增加而增加,那么微溝槽缺陷程度也隨之增強。

(4)氯氣/溴化氫氣體主要是用來調節多晶硅對二氧化硅的刻蝕選擇比,不對反應離子的能量變化產生影響。

正是因為該比率會影響選擇比,所以氯氣增加過多時,即氯氣/溴化氫氣體比率增加,對底部二氧化硅刻蝕速率也會增加,二氧化硅相對容易被刻蝕掉,這樣二氧化硅就不能提供阻擋保護作用,從而形成微溝槽缺陷。

5 結語

通過實驗明確了工藝參數對微溝槽缺陷形成的影響,工藝參數對多晶硅刻蝕過程和結果產生的影響是相互制約的,為了取得比較垂直的多晶硅形貌就需要比較大的偏壓功率和較低的腔體壓力,這對微溝槽缺陷的控制又是不利的。

一般建議壓力不要低于 10 mT,偏壓功率維持在 100 W 以下。在多晶硅刻蝕工藝開發中,要做好平衡,進行多尺度優化,對工藝窗口做一個全面檢查,不能故此失彼,這樣才能為生產提供一個足夠強大的工藝菜單。

參考文獻

[1] Michael A.Lieberman , Alan J.Lichtenberg.Principles of Plasma Discharges and Materials Processing, 2nd Edition[M].

[2] Stanley Wolf,Richard N. Tauber.Silicon Processing for the VLSI Era,Vol.1: Process Technology 2nd Edition[M].

[3] Wai-Fah Chen.VLSI Technology[M].

[4] 嚴利人等.微納尺度制造工程[M].電子工業出版社,2011.

[5] S.Van Nguyen, D.Dobuzinski, S.R.Stiffler, G.Chrisman.Ion scattering from sloped sidewall surfaces[J]. Electrochem. Soc, 1991, (138)1112 .

[6] Robert J.Hoekstra,Mark J.Kushner, Valerity Sukharev, Phillipe Schoenborn, J.Vac.Sci.Microtrenching resulting from specular re?ection during chlorine etch of silicon[J].Technol B,1998, 16(4).

-

集成電路制造

+關注

關注

0文章

11瀏覽量

6938 -

反應離子刻蝕

+關注

關注

0文章

5瀏覽量

1808

原文標題:微溝槽缺陷的形成與改進

文章出處:【微信號:appic-cn,微信公眾號:集成電路應用雜志】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

通過一體式蝕刻工藝來減少通孔的缺陷

單路溝槽式廁所節水器的改進

溝槽結構SiC-MOSFET與實際產品

MEMS開關缺陷的改進概述

MEMS開關缺陷改進

手柄溝槽信號蝶閥

溝槽結構SiC MOSFET幾種常見的類型

A/B型缺陷和D/V類缺陷介紹

工藝參數對微溝槽缺陷形成的影響并改進微溝槽缺陷

工藝參數對微溝槽缺陷形成的影響并改進微溝槽缺陷

評論