一、引言

為了提高傳輸速率和傳輸距離,計算機行業和通信行業越來越多的采用高速串行總線。在芯片之間、板卡之間、背板和業務板之間實現高速互聯。這些高速串行總線的速率從以往USB2.0、LVDS以及FireWire1394的幾百Mbps到今天的PCI-Express G1/G2、SATA G1/G2 、XAUI/2XAUI、XFI的幾個Gbps乃至10Gbps。計算機以及通信行業的PCB客戶對差分走線的阻抗控制要求越來越高。這使PCB生產商以及高速PCB設計人員所面臨的前所未有的挑戰。本文結合PCB行業公認的測試標準IPCTM-650手冊,重點討論真差分TDR測試方法的原理以及特點。

二、IPC-TM-650手冊以及PCB特征阻抗測試背景

IPC-TM-650測試手冊是一套非常全面的PCB行業測試規范,從PCB的機械特性、化學特性、物理特性、電氣特性、環境特性等各方面給出了非常詳盡的測試方法以及測試要求。其中PCB板電氣特性要求在第2.5節中描述,而其中的2.5.5.7a,則全面的介紹了PCB特征阻抗測試方法和對相應的測試儀器要求,重點包括單端走線和差分走線的阻抗測試。

三、TDR的基本原理及IPC-TM-650對TDR設備的基本要求

3.1 TDR的基本原理

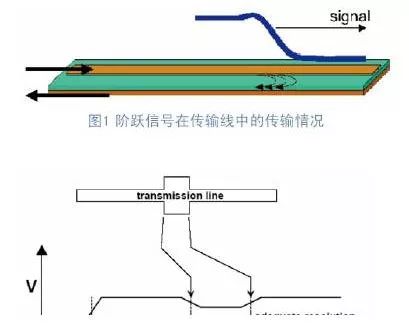

圖1是一個階躍信號在傳輸線(如PCB的走線)上傳輸時的示意圖。而傳輸線是通過電介質與GND分隔的,就像無數個微小的電容的并聯。電信號到達某個位置時,就會令該位置上的電壓產生變化,就像是給電容充電。因此,傳輸線在此位置上是有對地的電流回路的,因此就有阻抗的存在。但是該阻抗只有階躍信號自身才能“感覺到”,這就是我們所說的特征阻抗。

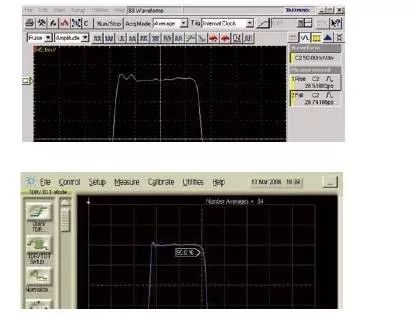

當傳輸線上出現阻抗不連續的現象時,在阻抗變化的地方階躍信號就會產生反射的現象,如果將反射信號進行取樣并顯示在示波器的屏幕上,就會得出如圖2所示的波形,從波形中我們可以看出一條被測試的傳輸線在不同位置上的阻抗變化。同時我們可以比較圖2中的兩個波形。這是使用兩臺分辨率不同的TDR設備在測試同一條傳輸線時獲得的測試結果。對于傳輸線阻抗變化的反映一個明顯而另一個不明顯。TDR設備感知傳輸線阻抗不連續的分辨率取決于TDR設備所發出的階躍信號上升時間的快慢,上升時間快所獲得的分辨率就高。而TDR設備的上升時間往往和測試系統的帶寬緊密相關,帶寬高的測試系統有更快的上升時間。

從另外一個角度來考慮,TDR設備的系統帶寬限制了TDR測試的分辨率。在IPC-TM-650測試手冊中對TDR設備的上升時間是按照系統上升時間(tsys)來定義的。當我們要測量一臺TDR設備的系統上升時間時,我們可以短路一臺TDR設備的輸出,此時可以測出該TDR設備的(tsys)(上升時間以及下降時間)。例如圖3的TDR設備的系統上升時間就高達28ps左右。

圖4是另一臺TDR設備的系統上升/下降時間的測試結果,系統的上升/下降時間在38ps~40ps之間。可見不同的TDR設備在系統上升/下降時間上是有很大的區別的,由此帶來的就是傳輸線阻抗測試分辨率的很大不同。

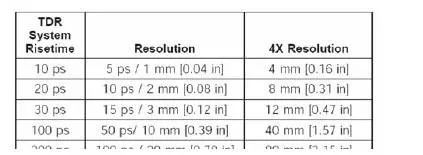

系統上升時間和分辨率的關系可以用下列的公式來描述:

Resolution= (tsys*V)/2,V為電信號在被測試傳輸線上的傳輸速率。

為了方便測試者了解TDR測試的分辨率以及PCB板走線的最小測試長度,在IPC-TM-650測試手冊的表4-1(圖5)中給出了速查數據。

3.2 IPC-TM-650手冊對差分TDR設備的基本要求

IPC-TM-650測試手冊是一套非常全面的PCB行業測試規范,從PCB的機械特性、化學特性、物理特性、電氣特性、環境特性等各方面給出了非常詳盡的測試方法以及測試要求。在以往的IPC-TM-650手冊中,對PCB差分TDR測試的要求較為寬松。手冊中允許測試者根據TDR測試設備的情況使用兩種不同的方法。

方法一:當測試者擁有差分TDR測試設備時,測試設備同時打出兩個幅度相等、方向相反的階躍脈沖,并通過這對差分信號的相互作用直接測出差分走線的阻抗。

方法二:當測試者沒有差分TDR測試設備時,測試設備在差分走線(A線與B線)時,先在A線上打出階躍信號,測試A階躍信號在A線上的反射特性記作AA,同時測出A階躍信號在B線上的感應信號,記錄為BA。隨后,在B線上打出階躍信號,測試B階躍信號在B線上的反射特性記作BB,同時測出B階躍信號在A線上的感應信號,記錄為AB。通過對獲得的AA、AB、BB、BA四個數值進行計算可以得出差分走線的阻抗。該方法又叫做“Super-Position”。

但是在(2004年3月版)IPC-TM-650手冊中,僅僅保留了方法一中的真差分TDR測試描述。而不再有方法二的“偽差分”TDR測試方法的描述。

-

pcb

+關注

關注

4352文章

23409瀏覽量

406696

原文標題:PCB差分走線的阻抗控制技術(一)

文章出處:【微信號:mcugeek,微信公眾號:MCU開發加油站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

評論