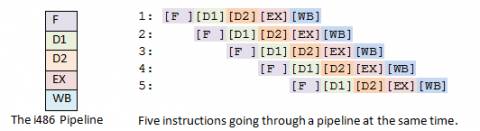

1989年推出的i486處理器引入了五級流水線。這時,在CPU中不再僅運行一條指令,每一級流水線在同一時刻都運行著不同的指令。這個設計使得i486比同頻率的386處理器性能提升了不止一倍。五級流水線中的取指階段將指令從指令緩存中取出(i486中的指令緩存為8KB);第二級為譯碼階段,將取出的指令翻譯為具體的功能操作;第三級為轉址階段,用來將內存地址和偏移進行轉換;第四級為執行階段,指令在該階段真正執行運算;第五級為退出階段,運算的結果被寫回寄存器或者內存。由于處理器同時運行了多條指令,大大提升了程序運行的性能。

處理器一般由如下功能單元組成:

取指單元

譯碼單元

執行單元

Load/store單元(load用于從內存中取數據,而STORE用于存數據到內存)

例外/中斷單元

電源管理單元

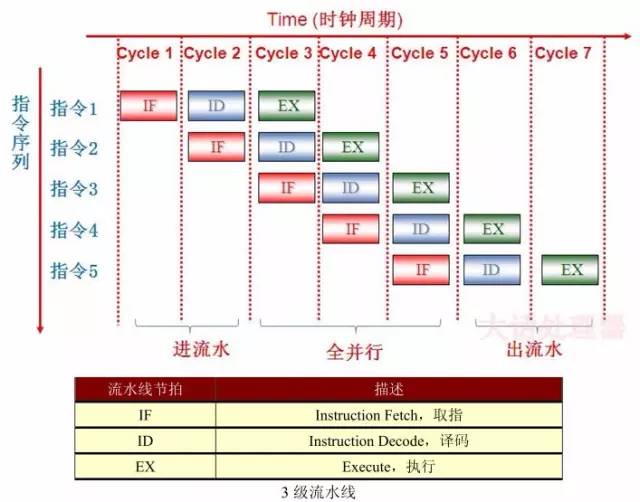

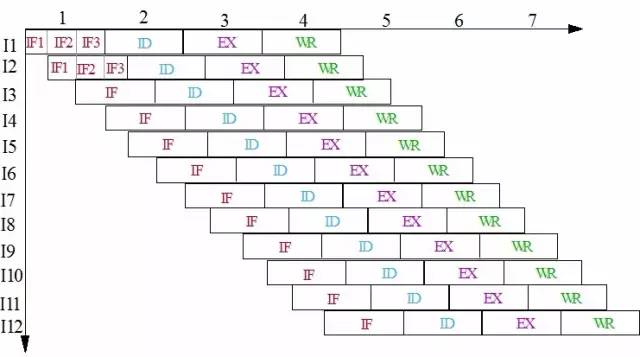

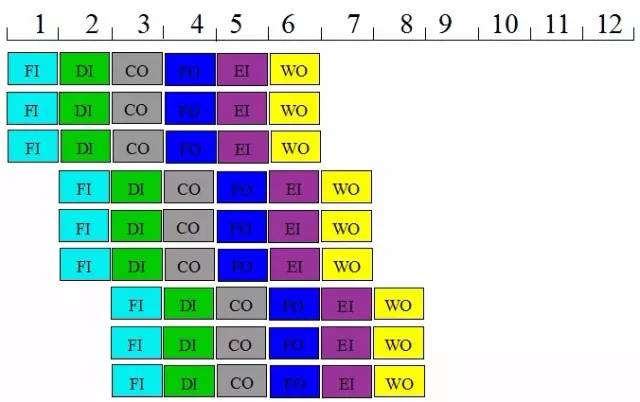

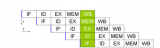

流水線通常由取指、譯碼、執行及Load/Store等單元組成。各單元按圖所示的幾個步驟循環重復自身工作。

流水線的含義:

與工廠生產線類似,將一件工作分成若干個固定的工序進行。

cpu流水線技術是一種將指令分解為多步,并讓不同指令的各步操作重疊,從而實現幾條指令并行處理,以加速程序運行過程的技術。指令的每步有各自獨立的電路來處理,每完成一步,就進到下一步,而前一步則處理后續指令。(原理和生產流水線一樣)

CPU指令流水線

根據之前描述的基礎,指令進入流水線,通過流水線處理,從流水線出來的過程,對于我們程序員來說,是比較直觀的。

I486擁有五級流水線。分別是:取指(Fetch),譯碼(D1, main decode),轉址(D2, translate),執行(EX, execute),寫回(WB)。某個指令可以在流水線的任何一級。

但是這樣的流水線有一個明顯的缺陷。對于下面的指令代碼,它們的功能是將兩個變量的內容進行交換。

|

1 2 3 |

XOR a, b XOR b, a XOR a, b |

從8086直到386處理器都沒有流水線。處理器一次只能執行一條指令。再這樣的架構下,上面的代碼執行并不會存在問題。

但是i486處理器是首個擁有流水線的x86處理器,它執行上面的代碼會發生什么呢?當你一下去觀察很多指令在流水線中運行,你會覺得混亂,所以你需要回頭參考上面的圖。

1、第一步是第一條指令進入取指階段;

2、然后在第二步第一條指令進入譯碼階段,同時第二條指令進入取指階段;

3、第三步第一條指令進入轉址階段,第二條指令進入譯碼階段,第三條指令進入取指階段。

4、但是在第四步會出現問題,第一條指令會進入執行階段,而其他指令卻不能繼續向前移動。

5、第二條xor指令需要第一條xor指令計算的結果a,但是直到第一條指令執行完成才會寫回。

所以流水線的其他指令就會在當前流水級等待直到第一條指令的執行和寫回階段完成。第二條指令會等待第一條指令完成才能進入流水線下一級,同樣第三條指令也要等待第二條指令完成。

這個現象被稱為流水線阻塞或者流水線氣泡。

常用概念:

1、流水線級數:流水線的節拍數。

2、吞吐率:單位時間內流水線能處理的任務數量。

3、最大吞吐率:流水線達到不間斷流水的穩定狀態后可獲得的吞吐率。

4、加速比:流水方式的工作速度與等效的順序工作方式時間的比值。

流水線指標:

1、流水技術無助于減少單個任務的處理延遲(latency),但有助于提高整體工作負載的吞吐率

2、多個不同任務同時操作, 使用不同資源

3、潛在加速比= 流水線級數

4、流水線的速率受限于最慢的流水段

5、流水段的執行時間如果不均衡,那么加速比就會降低

6、開始填充流水線的時間和最后排放流水線的時間降低加速比

超流水

超流水線技術是通過細化的流水,提高主頻。使得機器在一個周期內完成一個甚至多個操作,其實質是用空間換取時間。

超流水處理器是相對于基準處理器而言的,一般cpu的流水線是基本的指令預取,譯碼,執行和寫回結果四級。超流水線(superpiplined)是指某型CPU內部的流水線超過通常的5~6步以上,例如Pentium pro的流水線就長達14步。將流水線設計的步(級)數越多,其完成一條指令的速度越快,因此才能適應工作主頻更高的CPU。這一點我們可以用日常事例來說明,比如有5個人接力傳送木頭(對應一個5級的流水線),超流水是說細化該流水過程,即由10個人接力(此時為10級流水),顯然完成全部任務的速度會快。相當于***的一句話:人多力量大(效率高)。

超標量

超標量

超標量是指在CPU中有一條以上的流水線,并且每時鐘周期內可以完成一條以上的指令,這種設計就叫超標量技術。 其實質是以空間換取時間。

CPU架構是指在一顆處理器內核中實行了指令級并行的一類并行運算。這種技術能夠在相同的CPU主頻下實現更高的CPU吞吐率(throughput)。

-

處理器

+關注

關注

68文章

19807瀏覽量

233559 -

cpu

+關注

關注

68文章

11036瀏覽量

216005 -

流水線

+關注

關注

0文章

124瀏覽量

26492

原文標題:CPU的流水線

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA中的流水線設計

ARM架構系列中的流水線設計

現代RISC中的流水線技術

流水線操作,應用處理器,應用處理器的結構和原理是什么?

DSP設計中的流水線數據相關問題解析

處理器系列之CPU流水線科普

評論