IIC總線,是INTER-IC串行總線的縮寫。INTER-IC原文大意是用于相互作用的集成電路,這種集成電路主要由雙向串行時鐘線SCL和雙向串行數據線SDA兩條線路組成,由荷蘭菲利浦公司于80年代研制開發成功。

IIC總線在傳送數據時其速率可達100kbps,最高速率時可達400kbps,總線上允許連接的設備數主要決定于總線上的電容量,一般設定為400pF以下。I2C總線主要在微處理器的控制之下,因此通常稱微處理器是I2C總線的主機。習慣上總稱受控設備及功能電路為I2C總線的從機。這種主機與從機之間的連接通常是在總線的輸出端,而輸出端的電路結構為IIC總線的從機。這種主機與從機之間的連接通常是在總線的輸出端,而輸出端的電路結構又總是開漏輸出或集電極開路輸出。 通常數據傳送要由主機發出啟動信號和時鐘信號,向所控從機發出一個地址、一個讀寫位和一個應答位,其中地址位為7位數據,在實際控制中,一般一次只能傳送一個8位數據,并以一個停止位結束。在實際應用中,往往被傳送的數據位數會超過8位,也就是說總會有多字節傳送,這時必須在傳送數據地址結束后再傳送一個副地址。因此,被傳送的字節沒有限制,但每一個字節后面必須有一位應答位。應答位通常被設定在低電平,當應答位處于高電平時,指示被傳送的數據已結束。I2C總線在空閑狀態時,也就是不在進行任何操作控制時,數據線SDA和時鐘線SCL總是處于高電平輸出狀態。當操作控制系統時,I2C總線的主機將發出啟動信號,使數據線SDA由高電平變為低電平,同時時鐘線SCL也發出時鐘信號。I2C總線在傳送數據時,總是將最高位數碼放在前面作為其特有的傳送順序。在數據傳送過程中,如果從機在完成某一操作之前不能接收下一個字節數據,即數據中斷,這時時鐘線SCL將被位至低電平,從而迫使發送器主機進入等待狀態,當接收器從機準備好接收下一個字節時再釋放時鐘線SCL,繼續傳送數據。在I2C總線的控制系統中,有時從機也可以是多臺微處理器,在多臺微機同時工作時,它們對總線的控制也由相似于時鐘的同步方式進行仲裁,也就是說時鐘的同步與仲裁過程是同時進行的,不存在因是主機而有優先權次序。不同速度的從機可以接在同一I2C總線上完成相互間數據的傳送。高速方式芯片和普通芯片可以混合于同一I2C總線上。

I2C總線的特點與特性I2C總線與傳統的PWM調寬脈沖相比較,其最大的特點是串行數據線和時鐘線都是雙向傳輸線。I2C總線在實際電路的應用中,兩根線各自通過一個上拉電阻連接到電源電壓的正極端,當總線空閑時,數據線SDA和時鐘線SCL必須保持高電平,同時各接口電路的輸出又必須是開路漏極或開路集電極,因此I2C總線的最大特性是在地址信息傳輸過程中,即可以是主控器也可以是被控器,或既可以是發射器又可以是接收器,從而為掛在總線上的各集成電路或功能模塊完成各自的功能提供了極大方便。如果I2C總線用作主控器電路即微處理電路,則在總線上將提供時鐘傳送及初始化的數據傳輸,而控制數據信息傳送的對象、方向及傳送的終止也由主控器來決定。在I2C總線上被主控器所尋址的集成電路或功能模塊,稱之為被控器。在I2C總線上,被控器每接收一個“數碼”后都要在數據線上給主控器發送一個識別應答信號,以示完成一個控制功能。因此,I2C總線具有十分靈活的運用性。并且還具有多重主控的能力,如多個作為主控器去控制占用總線的電路,都可以根據在I2C總線上進行數據傳送的工作狀態,被分為主控發送器、主控接收器、被控發射器、被控接收器。在多重主控能力中,由于總線的仲裁過程,I2C總線的時鐘信號將是各試力占用總線的各主控器的時鐘信號的同步組合。所謂仲裁是在多個主控器試圖同時控制總線時一個裁決過程,它只允許其中的一個主控器繼續占用總線,并保證在整個過程中總線上的數據不會被丟失或出錯誤;所謂同步是將兩個或多個器件的時鐘信號進行處理。I2C總線上的時鐘信號是由主控器產生,每個主控器在占用總線傳送數據期間都有自已的時鐘,因此,在應用中,由一個主控器產生的I2C總線時鐘信號只可能被一個低速的被控器或另一個主控器改變。然而,一個低速的被控器可將串行時鐘線保持低電平,以延長總線時鐘信號的低電平周期,使高速的主控器和低速的被控器達到同步,因此,當總線上正在進行仲裁時,另一個主控器也能改變總線的時鐘周期。

I2C總線的控制技術由于在I2C總線中的多主控器的控制權總是相互競爭,并且在相互競爭中進行尋址和數據發送,因此總線上沒有中央微處理器,也沒有任何優先級。在I2C總線上進行數據傳輸時,所有的主控器都會在串行時鐘線上產生自己的時鐘信號,而且只有當時鐘線上的信號處于高電平時,數據線上的數據才是有效的。因此,當各主控器向總線上輸出各不相同的時鐘頻率時,只有通過仲裁過程,才可使總線上有一個統一的時鐘信號。只有總線上的時鐘線上的一種“線與”連接和雙向傳輸特性來實現的。因此,I2C總線的控制基礎主要是仲裁過程和時鐘同步。在總線的仲裁過程中,一旦有一主控器輸出一個低電平時鐘信號,則串行時鐘線將由此變為低電平,直到該主控器時鐘信號的高電平狀態到來,數據信號才開始傳送。在總線上這個時鐘線的電平轉換,將影響所有主控器的時鐘信號低電平周期的計時。事實上,當一個主控器的時鐘信號由低電平向高電平轉換時,它可能并不會改變串行時鐘線的低電平狀態,因為此時可能有另一個主控器仍然處于時鐘低電平周期。也就是說,在I2C總線控制中,時鐘線將由時鐘低電平周期最長的主要控器保持為低電平狀態,而其他時鐘低電平周期較短的主控器則將相繼進入時鐘高電平等待狀態。只有當總線上的所有主控器都結束了時鐘低電平周期的計時后,時鐘線才被完全釋放,即時鐘線的狀態達到一致高電平狀態。當所有主控器時鐘信號都進入高電平狀態后,便開始了各自的時鐘信號高電平周期計時。當有一個主控器的時鐘高電平狀態計時結束時,這個主控器將再次使I2C總線上的時鐘線SCL處于低電平狀態。從而,在總線的仲裁過程中,使時鐘線通過各主控的時鐘輸出產生一個統一的時鐘同步信號成為現實。簡言之,在多重主控器的I2C總線上,時鐘線信號的低電平周期由時鐘信號低電平周期最長的主控器決定,而時鐘線信號的高電平周期則由時鐘信號高電平周期最短的主控器決定。在I2C總線中,具有主控能力的器件的數據傳輸和尋址也是在仲裁中進行的。當有多個主控器企圖同時占用總線傳輸數據時,根據I2C總線的規約它們之間會有一個促裁過程,以決定誰將占用總線。促裁是在時鐘線SCL為高電平時,根據數據線SDA的狀態進行的。因此,仲裁過程和時鐘電平、數據線狀態是相輔相成的。也正是這種相輔相成的機制,使在總線仲裁過程中,當有其他主控器在數據線上傳送低電平時,發送高電平的主控器將會發現此時數據線上的電平與其輸出電平不一致,從而被裁決失去總線的主控權,并立即關閉其數據輸出。仲裁過程可以持續詐多位,以對多個主控器正在企圖尋址同一電路的事件進行判決。如果一個主控器在發送某一字節期間被裁決失去主控權,則它的時鐘信號可繼續輸出,直到整個字節發送結束為止。如果主控器在其尋址階段被仲裁決定失去主控權,則該主控器必須立刻進入被控接收器狀態,以判決被仲裁決定獲得主控權的主控器是否正在對它進行尋址。產生數據的主控器一旦發現內部數據電平與數據總線的實際電平之間有差異,則它的輸出將被立即關閉,隨即在總線上輸出一個高電平(釋放總線),這就不會影響獲得主控權的主控器所進行的數據傳輸,總線上的尋址和數據傳輸等住處也不會丟失。因此,I2C總線的仲裁過程使I2C總線上的數據傳輸得以順利進行,為多種控制功能的實施奠定了良好的基礎。

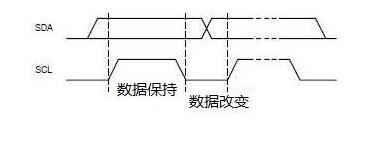

I2C總線的傳輸I2C總線的傳輸是一個比較復雜的數碼傳輸,它主要是以8bit的字節進行數據傳輸,而傳輸時又總有一個時鐘脈沖相對應,因此,I2C總線的數據傳送實質上是個脈沖串的傳輸,其傳輸格式如圖1-14所示。圖中1為字節傳送完成接收器內產生中斷信號,2為當處理中斷服務時時鐘線保持低電平。在I2C總線上,每一個數據中,邏輯“0”和邏輯“1”的信號電平取決于相應的正端電壓。I2C總線在進行傳送時,在時鐘信號為高電平期間,數據線上的數據必須保持穩定,只有在時鐘線上的信號為低電平期間,數據線上的高電平或低電平狀態才允許變化。這就保持了數據傳輸的有效性。在時鐘線保持高電平期間,由于數據線由高電平向低電平的變化是一種穩定的狀態,所以就將其狀態規定為起始條件;而當時鐘線保持高電平期間,數據線是由低電平向高電平變化,則規定為停止條件。只有I2C總線中主控器產生起始條件和停止條件兩個信號時,總線才會被認為處于“忙”態或“閑”態,從而準確控制了比特位的傳送。在I2C總線上,比特位傳送字節的后面都必須跟隨一位確認位,或稱跟隨一位應答位。并且數據是以最高有效位首先發出。但是,當正在進行數據傳輸的接收器收到完整的一個數據字節后,有可能還要完成一些其他的工和,如處理一個內部中斷服務等。在這種情況下就有可能無法立刻接收另一字節的數據,因而,此時接收器可以通過總線上的時鐘保持為低電平,從而使發送器進入等待狀態,直到接收器準備好接收新的數據,而接收器通過釋放時鐘線使數據傳輸繼續進行,正是I2C總線能允許其他總線的數據格式進行傳輸,才有一個特殊尋址開始的信息傳輸,以及通過對總線產生一個停止信號進行停止。當一個字節的數據能夠被總線上的一個已被尋址的接收器接收后,總線上的一般要產生一個確認信號,并在這一位時鐘信號的整個高電平期間,使數據保持穩定的低電平狀態,從而完成應答確認信號的輸出。確認信號通常是指起始信號和停止信號,如果這個信息是一個起始字節,或是總線尋址,則總線上不允許有應答信號產生。如果因某種特殊情況,被控器不對應的被控尋址進行確認回答,則必須將數據線置于高電平,然后主控器可以通過產一個停止信號來結束總線的數據傳輸。如果被控接收器對被控尋址做出了確認應答,但在數據傳輸的一段時間以后,又無法繼續接收更多的數據,則主控器也將停止數據的繼續傳送。因此,被控接收器可以通過對無法接收的第一個數據字節不產生確認應答信號來通知主控器,即在相應的應答信號時鐘位上將數據線置于高電平,主控器則在總線上產生停止信號,從而結束數據的傳送。注:1-7 為地址位;8為讀/寫位;9為應答位在I2C總線上,它的數據傳輸總有一些規約要求,例如,起始信號的后面總有一個被控器的地址。被控器的地址一般規定為7bit的數據,數碼中的第8比特是數據的傳輸方向位,即讀/寫位。在讀/寫位中,如果是“0”,則表示主控器發送數據,也就是執行“寫”的功能;如果是“1”,則表示主控器接收數據,也就是執行“讀”的功能。而數據的每次傳輸總是隨主控器產生的停止信號而結束。而I2C總線中,有時主控器希望總占用總線,并不斷進行數據傳輸,因此,在設定規約時,可以在不首先產生信號的情況下,再次發出起始信號對另一被控器進行尋址。為解決這一問題,可以采用多種讀/寫組合形式來進行總線的一次數據傳輸。在多種讀/寫組合形式中,主要有三種措施,其中:1.主控發送器向被接收器發送數據,數據傳輸方向在整個傳輸過程中不變。2.主控器在第一個字節后立即從被控制器讀數據,在首位確認應答信號產生后,主控發送器變成主控接收器,而被接收器變成被控發送器,同時首位應答信號仍由被控器產生,使停止信號總是由主控器產生。3.數據傳輸過程中的復合格式需要改變傳送方向時,起始信號和被控器地址都會被重復產生一次,但兩次的讀/寫方向正好反相。總之在I2C總線上,通過接口電路收到起始信號后,必須復位它們的總線邏輯,以使被控制器地址的傳輸得以預處理,從而完成對各不相同功能電路的控制

總結一下:1、無論讀與寫,都是在時鐘線為低時把數據送到數據總線上,在高時采樣數據,把數據鎖存到內部,所以讀之前先把時鐘線拉低,做好準備(數據線為高表示釋放數據線),為接下來讀數據做好準備。也就是時鐘信號為低時,數據線上的高低電平才允許變化,時鐘信號為高時,數據總線上的數據必須保持穩定。2、起始信號產生后,總線為被占用狀態(SDA拉低);終止信號產生后,總線為空閑狀態(SCL被釋放了)。3、接收器件收到一個完整的數據字節后有可能需要完成一些其它工作,如處理中斷,可能無法立刻接收下一字節,這時從機將SCL拉成低電平,從而使主機處于等待狀態。直到從機準備好接收下一字節,再釋放SCL線使之為高,從而數據傳送可繼續進行。數據線上的數據是在時鐘信號為高時被采樣。

4、當主機接收數據時,它收到最后一個數據字節后,必須向從機發出一結束信號。這個信號是由對從機的非應答來實現的。然后,從機釋放SDA線,以允許主機產生終止信號。

-

I2C

+關注

關注

28文章

1484瀏覽量

123619

原文標題:I2C總線的深入淺出介紹

文章出處:【微信號:ittbank,微信公眾號:ittbank】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

I2C總線原理詳解

用Verilog HDL實現I2C總線功能

I2C總線詳解

基于CPLD的I2C總線接口設計

I2C總線的特點、控制技術與傳輸分析

I2C總線的特點、控制技術與傳輸分析

評論