卡內基梅隆大學的Kevin K. Chang發表了一篇亮眼、出色的博士論文——《理解和改進基于DRAM的內存系統的延遲》(Understanding and Improving the Latency of DRAM-Based Memory Systems),解決了DRAM問題,并提出了一些新的架構改進辦法,以在DRAM延遲方面做出實質性的改進。

三個問題

Kevin將DRAM延遲問題分成四個部分,筆者將在這里總結其中三個:

·低效的批量數據移動。

·DRAM刷新干擾。當DRAM正在刷新時,它不能全部被訪問。

·單元格(Cell)潛伏期的變化——由于制造變異性。

至于第四個問題:延遲所帶來的影響,有興趣的朋友可以一起討論。

1.低效的批量數據移動

在內存和存儲代價高昂的時候,數據移動被限制在一個寄存器大小的塊中,或者最多是來自磁盤的512字節塊。但如今,在存儲容量達千兆字節的存儲空間和海量內存的情況下,海量數據移動變得越來越普遍。

但數據移動的架構——從內存到CPU,再到有限的內存總線——都沒有改變。Chang的建議是一種新型的、高帶寬的存儲器子陣列之間的數據通路,利用幾個隔離晶體管在同一存儲器中的子陣列之間創建寬——8192位寬——并行總線。

2.DRAM刷新干擾

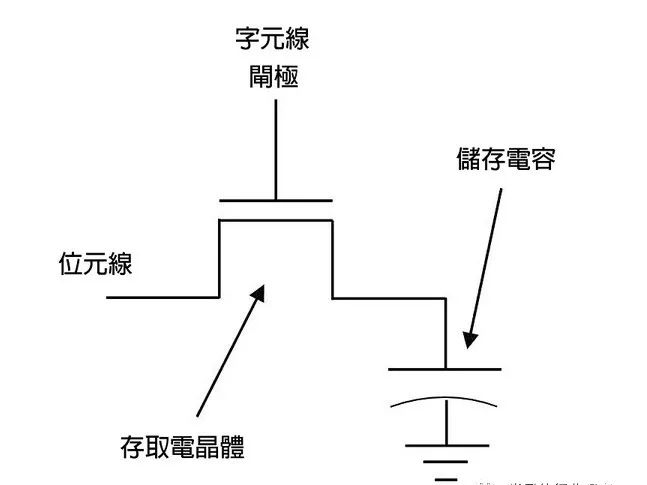

DRAM內存單元需要刷新以保存數據,這就是為什么它被稱為動態RAM。DRAM刷新是成隊列,而不是一次性刷新的,因為這樣做需要太多的能耗。但是,當一個隊列被刷新時,它不能被訪問,這會造成延遲。

DRAM的延遲正在變高,因為隨著芯片密度的增加,需要更新更多的隊列,32Gb的芯片上可能降低將近20%的性能。

Chang提出了兩種機制,即通過對bank和子陣列的內存訪問進行并行刷新來隱藏刷新延遲。一個是使用無序的per-bank刷新,使內存控制器可以指定一個空閑的bank來刷新,而不是常規的嚴格循環順序。第二種策略是寫-刷新操作并行化,使刷新延遲和寫延遲重疊。

在他的測試中,使用8核CPU,這些策略提高了超過27%的加權內存性能。

3.單元格延遲變化

得益于制造工藝的提升,記憶單元格可以有大量性能提升,隨著密度的增加而增加。但是DRAM被指定以最慢的單元的速度可靠運行,這意味著如果使用最快的單元格,就會有顯著的性能上升。

Chang在論文中提出了兩種利用這種變化的機制,獲得的速度提升從13%提高到了幾乎20%。

探索與優化

在系統架構中,探索瓶頸和修復瓶頸的工作是沒有終點的。過去20年內,DRAM一度被認為難有進步,但我們看到,其延遲水平也會被改變。

隨著越來越多的晶體管、專業指令集和諸如此類的性能的提高,降低DRAM延遲也將成為性能改進的主要目標。

-

DRAM

+關注

關注

40文章

2350瀏覽量

185733 -

延遲

+關注

關注

1文章

74瀏覽量

13796

原文標題:20年難有進步,DRAM延遲問題得到優化

文章出處:【微信號:cunchujie,微信公眾號:存儲界】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

[分享]直接總線式DRAM的信號連接

DRAM內存原理

【內存知識】DRAM芯片工作原理

NUC8i7BEH DRAM頻率不穩定

FPGA DRAM數據錯位

什么是EDO DRAM/All-in-One

展望2013:DRAM產業五大重點趨勢預測

鈺創科技開發全新的DRAM架構

DRAM的架構/標準/特點/未來展望

評論