首先來說說退偶電容的布局布線

下圖中a-e都不對?什么原因?

如上圖,這種位置的電容,一般有兩個作用。

二是作為一種去耦的作用,即抑制IC內部的雜訊如振蕩器的多次諧波傳到電源里而干擾其它電路的,也就是說雜訊不要傳遞到電源層或地層。

不過在此圖中已經標注了此電容為去耦電容。

對于第一種情況,不一定非要經過電容后,才接到IC的電源或地引腳,但要盡量的靠近。典型的例子是BGA封的去耦合電容,一般都放在背面。盡量靠近的情況下,也要注意電容到電源和地平面的布線,越短、越粗越好;否則會引入布線電感。因瞬時電源的補給也是找最短阻抗路徑的,過大的分布電感會帶來不利因素。

對于第二種情況,IC的電源先經過電容后,再接到電源或地層,這是最好的,這樣雜信先由電容去掉了,就不會到電源或地層上了。

圖中a到e里,噪聲從的地線和電源線出來的后,在到達這個退耦電容之前已經通過過孔的支路跑到其它電路里去了,圖中的f的走法比較好。也不是說不這樣走線就一定就會出問題一定就不行了,比實際pcb走線的時候由于各種客觀原因不一定能完全滿足這個走線標準,只能說盡量按圖中f的方式來。

另外再這種情況,尤其要注意不要在布線中引入過大的電感,因高頻雜信,及其高次諧波,其頻率都很高,而在高頻下,小小的電感都會帶來較大的阻抗,至高頻雜信不能由電容低阻地耦合到地,從面降低了去耦效果。

再來說說退偶電容為何大都取值104電容?

這叫去耦而非濾波,用于對付電源回路中的高頻噪聲。對于常規低速數字電路和一般模擬電路而言,其工作頻率不算高,104電容的頻譜特性已經可以滿足,而頻譜特性可以滿足時,容量越大越好,所以這些電路多用104的去耦電容。不過容量越大的電容,其ESL也越大,高頻特性也就越不好,高頻電路去耦時就需要用到小容量的去耦電容,對于GHz級的電路,去耦電容甚至需要用到10pF量級的,這時往往采用多種不同容量的電容并聯來去耦。

還可以引申到各種電路上各個節點的電容,對于電容取值可以不用去關心去耦和濾波的區別。這個是去耦電容也好,濾波電容也好,是為了濾除電源上的噪聲的。

對于數字電路,104就可以了。

對于高頻電路,一般需要104、102、100P、10P等多個電容并聯。

和電容的等效電路有關,和頻率有關。比如39P適合900MHz,10P適合1800MHz。

-

電容

+關注

關注

100文章

6089瀏覽量

150714 -

退耦電容

+關注

關注

1文章

29瀏覽量

9596

原文標題:【實踐出真知】一顆小小的退偶電容,引發的糾結!

文章出處:【微信號:fcsde-sh,微信公眾號:fcsde-sh】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

HDMI2.0 接口保護 僅用一顆料

求推薦一顆level shifter!

拿到一顆DCDC芯片應該測試哪些參數

什么是退耦電容

一張圖看退耦電容布局布線資料下載

在電子設計中如何選擇一顆合適的電容呢?

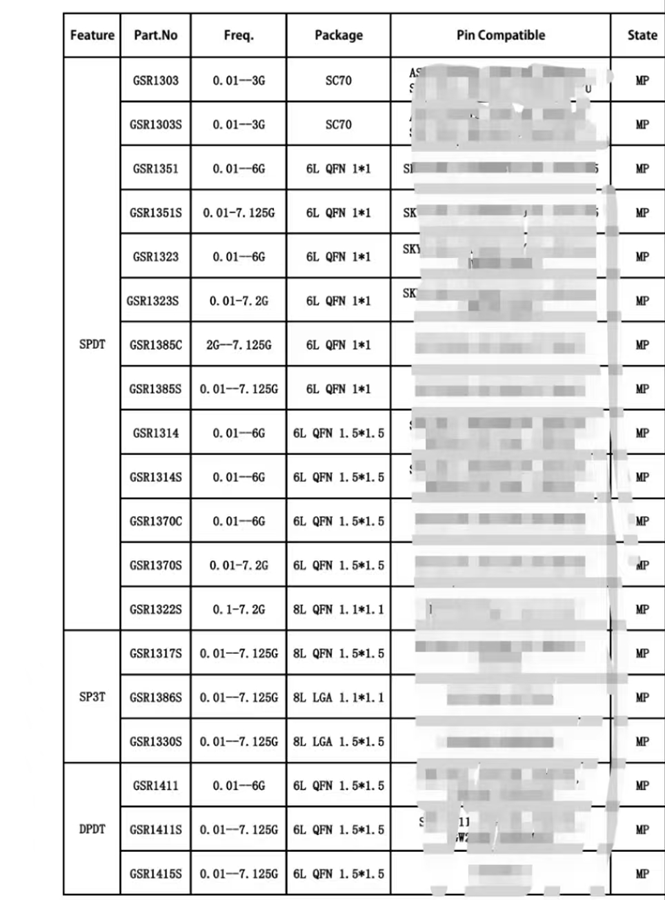

一顆射頻開關的獨白

一顆小小退偶電容的布局布線與取值技巧

一顆小小退偶電容的布局布線與取值技巧

評論