1.引言

DDS頻率合成器具有頻率分辨率高,輸出頻點(diǎn)多,可達(dá)2N個頻點(diǎn)(假設(shè)DDS相位累加器的字長是N);頻率切換速度快,可達(dá)us量級;頻率切換時相位連續(xù)的優(yōu)點(diǎn),可以輸出寬帶正交信號,其輸出相位噪聲低,對參考頻率源的相位噪聲有改善作用;可以產(chǎn)生任意波形;全數(shù)字化實(shí)現(xiàn),便于集成,體積小,重量輕。

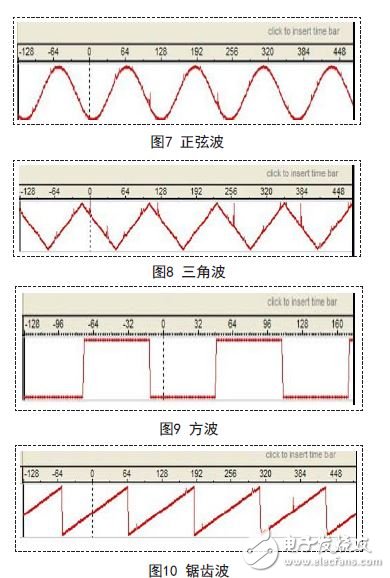

本文介紹了DDS的基本原理,同時針對DDS波形發(fā)生器的FPGA實(shí)現(xiàn)進(jìn)行了簡要介紹,利用SignalTapII嵌入式邏輯分析儀對正弦波、三角波、方波、鋸齒波進(jìn)行仿真驗證。

2.DDS波形發(fā)生器的FPGA實(shí)現(xiàn)

FPGA的應(yīng)用不僅使得數(shù)字電路系統(tǒng)的設(shè)計非常方便,而且它的時鐘頻率已可達(dá)到幾百兆赫茲,加上它的靈活性和高可靠性,非常適合用于實(shí)現(xiàn)波形發(fā)生器的數(shù)字電路部分。使用FPGA設(shè)計DDS電路比采用專用DDS芯片更為靈活,只需改變FPGA中的ROM數(shù)據(jù),DDS就可以產(chǎn)生任意波形,具有相當(dāng)大的靈活性。

2.1 FPGA設(shè)計流程

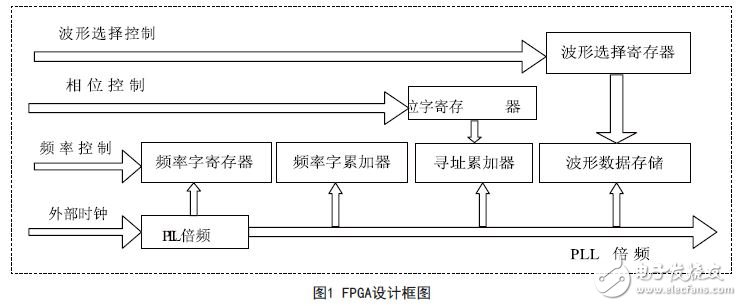

FPGA的設(shè)計框圖如圖1所示,F(xiàn)PGA的主要功能是:產(chǎn)生與外圍電路的接口電路,使其能夠接受外圍邏輯控制信號;保存頻率字,并構(gòu)成相位累加器,產(chǎn)生與主時鐘相同頻率的RAM尋址字;用內(nèi)部的存儲塊構(gòu)成存放多種波形數(shù)據(jù)的ROM,并通過相應(yīng)的控制線進(jìn)行選擇;構(gòu)造出兩個多波形選擇輸出的輸出通道,其中的一路通道可具備移相功能;用內(nèi)部的PLL倍頻外部低頻晶振,并輸出與主時鐘同頻的時鐘,驅(qū)動片外高速D/A.

2.2 時鐘模塊

根據(jù)耐奎斯特采樣定理要得到輸出頻率為10MHz的信號,其所輸入的信號時鐘頻率必須達(dá)20MHz以上。采樣頻率越高,輸出波形的平坦度越好,同時波形的的采樣點(diǎn)數(shù)也越多,那么獲得的波形質(zhì)量也就越好。本設(shè)計中的DDS模塊是一高速模塊,所以對系統(tǒng)時鐘就有很高的要求,不僅需要有較高的頻率,而且還要有非常高的穩(wěn)定性,如果在FPGA的時鐘端直接加一高頻晶振,不僅時鐘不穩(wěn)定,而且功耗大,費(fèi)用高,在本設(shè)計中,直接調(diào)用Altera公司的PLL核,在FPGA時鐘端只需加一低頻晶振,通過FPGA內(nèi)部PLL倍頻達(dá)到系統(tǒng)時鐘要求,輸出的時鐘相位偏移在允許范圍內(nèi)。

2.3 DDS控制模塊

(1)頻率控制字輸入模塊

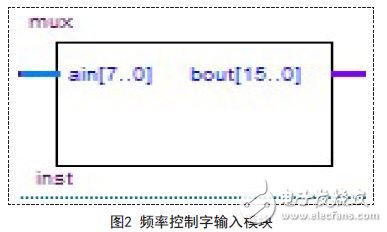

頻率控制字輸入模塊如圖2所示,數(shù)據(jù)選擇器控制輸入16位頻率控制字。

(2)步進(jìn)頻率控制模塊

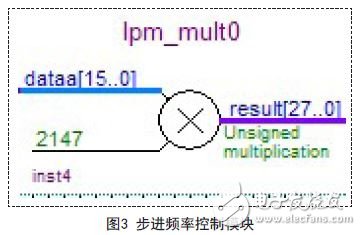

步進(jìn)頻率控制模塊如圖3所示,通過一個乘法器來控制步進(jìn)頻率,具體算法如下:f步進(jìn)=fc*2147/232.

通過改變乘法器的乘數(shù)來改變步進(jìn)頻率。要使步進(jìn)為1Hz那么乘法器的乘數(shù)為22.

(3)頻率累加器

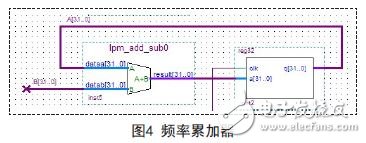

頻率累加器模塊如圖4所示,通過一個32位加法器跟32位寄存器構(gòu)成頻率累加器,頻率控制字高4位為0.

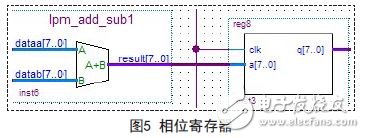

(4)相位寄存器

相位寄存器模塊如圖5所示,通過一個8位加法器跟8位寄存器構(gòu)成相位寄存器并產(chǎn)生8位波形數(shù)據(jù)地址。

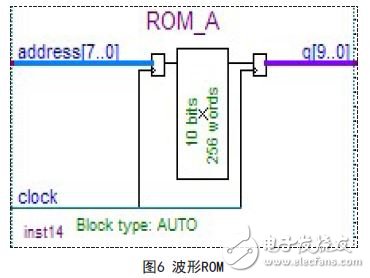

(5)波形存儲器設(shè)計

波形數(shù)據(jù)ROM就是存放波形數(shù)據(jù)的存儲器,大多波形發(fā)生器產(chǎn)品都將波形數(shù)據(jù)存放在外部的ROM中,這樣使得各部分結(jié)構(gòu)清晰,測試、維護(hù)更加方便但由于ROM本身讀取速度慢的缺點(diǎn),使得整個系統(tǒng)性能下降,工作頻率下降,為了解決以上問題,本設(shè)計使用的是用FPGA設(shè)計出ROM,在FPGA中存放波形數(shù)據(jù),使用Quartus II9.0中的Mega Wizard Plug-In Manager來生成一個ROM,如圖6所示。

Mega Wizard Plug-In Manager的設(shè)置,根據(jù)設(shè)計的要求,經(jīng)過七步的設(shè)置,就可以生成一個ROM的IP核。當(dāng)在波形ROM中固化所需波形的一個周期的幅度值后,由地址發(fā)生器產(chǎn)生的地址對波形ROM尋址,依次可取出送至D/A轉(zhuǎn)換及濾波后即可得到所需的模擬波形輸出。計算波形數(shù)據(jù)可以有兩種方法:C語言與matlab計算。

3.仿真實(shí)驗結(jié)果

按照第2節(jié)的系統(tǒng)設(shè)計,設(shè)計程序下載到FPGA芯片,使用QuartusII軟件自帶SignalTapII嵌入式邏輯分析進(jìn)行仿真,觀察信號波形圖,正弦波如圖7,三角波如圖8,方波如圖9,鋸齒波如圖10.

4.總結(jié)

經(jīng)實(shí)驗結(jié)果表明,通過DDS技術(shù)合成的波形具有良好的穩(wěn)定性,易于控制和調(diào)節(jié),利用FPGA能在很短時間內(nèi)快速構(gòu)建任意波形,提高了設(shè)計效率,具有實(shí)際應(yīng)用價值。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603014 -

DDS

+關(guān)注

關(guān)注

21文章

633瀏覽量

152631 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1605瀏覽量

80580

發(fā)布評論請先 登錄

相關(guān)推薦

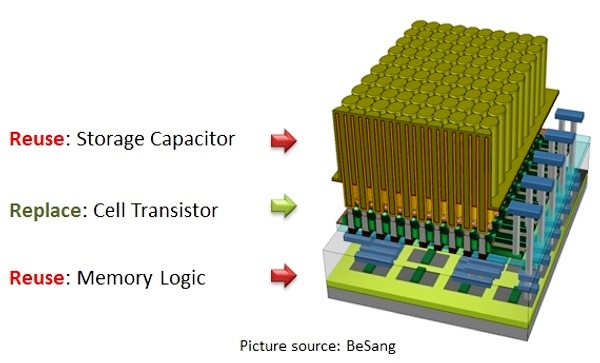

為了延長DRAM存儲器壽命 必須短時間內(nèi)采用3D DRAM

DDC264短時間內(nèi)超出電壓范圍,是否還能正常測量?

為什么Type-C接口能在短時間內(nèi)迅速取代Micro USB接口呢

如何在開機(jī)后的最短時間內(nèi)從LIS2DH讀取有效數(shù)據(jù)嗎?

DIY短時間應(yīng)急燈

中國電信總裁:短時間內(nèi)未有回A股上市的決定

新發(fā)明的四翼飛行器可在短時間內(nèi)不受束縛地飛行

深圳的企業(yè)運(yùn)營成本在不斷上漲,這不是其他城市短時間內(nèi)能夠趕上的

如何設(shè)計出在5秒或更短時間內(nèi)具有完美平坦輸出阻抗的VRM

暴雪游戲平臺持續(xù) DDOS 攻擊:短時間內(nèi)完全解決該問題

如何在短時間內(nèi)解決電廠鍋爐風(fēng)機(jī)軸修復(fù)問題?

華強(qiáng)北芯片需求短時間內(nèi)暴漲 本地芯片供應(yīng)很難跟上

如何最短時間內(nèi)找出Linux性能問題?

電力電容器為什么不允許短時間內(nèi)過電壓運(yùn)行

精軋機(jī)彎輥缸傳動側(cè)襯板安裝面磨損,短時間內(nèi)快速高效修復(fù)

能在很短時間內(nèi)快速構(gòu)建任意波形的FPGA

能在很短時間內(nèi)快速構(gòu)建任意波形的FPGA

評論