以下文章來源于ICPMS冷知識(shí) ,作者gz07apple

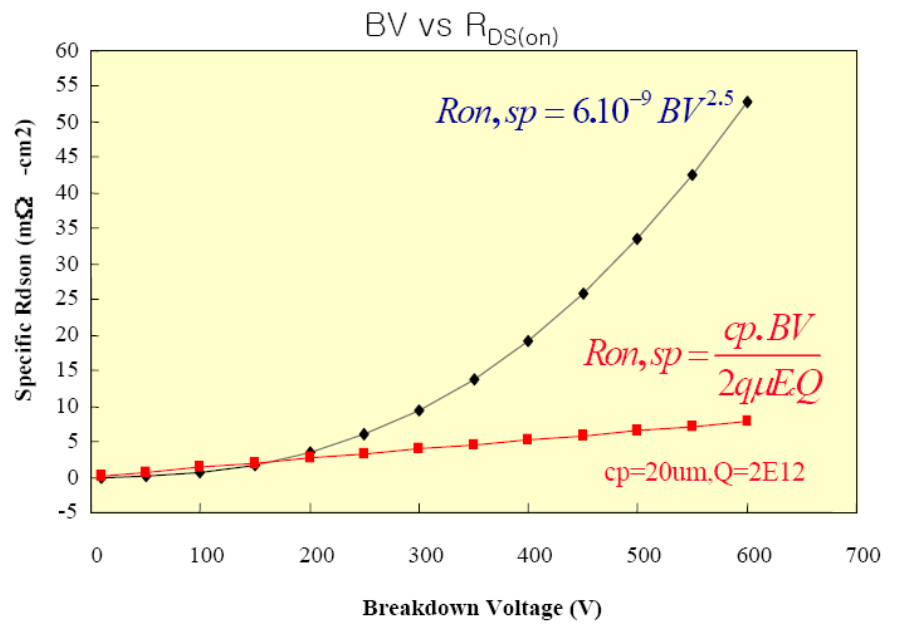

在過去的二十年,MOSFET主要用作開關(guān)器件,得到了長足的發(fā)展,由于它是多子器件,有相對較小的開關(guān)損耗,但其通態(tài)功耗較高,要降低通態(tài)功耗,導(dǎo)通電阻受擊穿電壓限制(導(dǎo)通電阻與擊穿電壓的2.5次方呈正比)無法再下降而存在一個(gè)極限,被稱為“硅極限(Silicon Limit)”

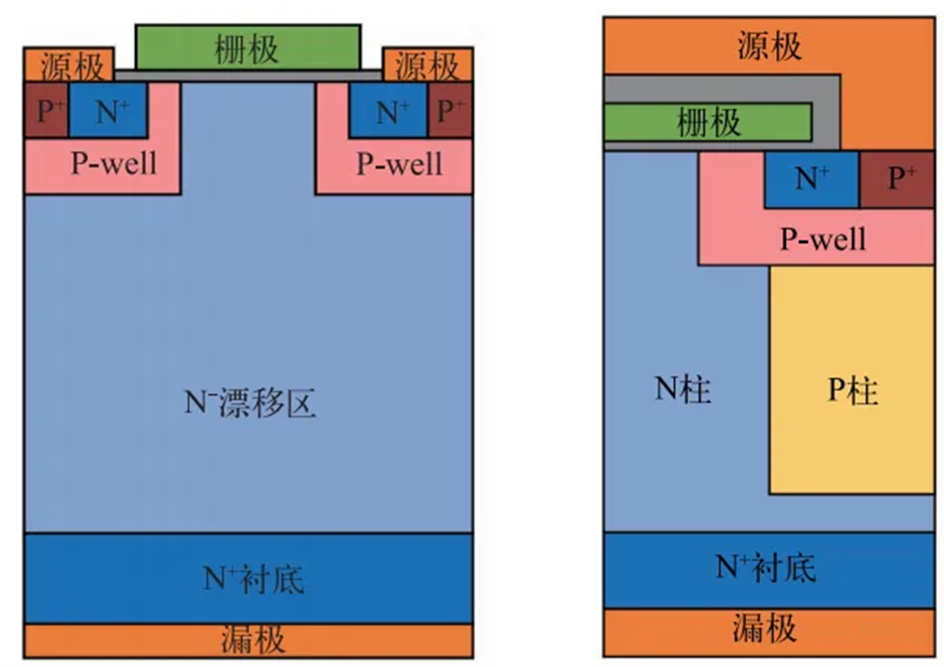

垂直雙擴(kuò)散金屬氧化物半導(dǎo)體(VDMOS)是一種發(fā)展迅速、應(yīng)用廣泛的新型功率半導(dǎo)體器件。它在常規(guī)VDMOS基礎(chǔ)上,引入超結(jié)(Superjunction)結(jié)構(gòu),使之既具有VDMOS輸入阻抗高、開關(guān)速度快、工作頻率高、電壓控制、熱穩(wěn)定性好、驅(qū)動(dòng)電路簡單的特性,又克服了VDMOS的導(dǎo)通電阻隨擊穿電壓急劇增大的缺點(diǎn),提升了系統(tǒng)效率。目前超結(jié)VDMOS已廣泛應(yīng)用于電腦、手機(jī)、照明等消費(fèi)電子領(lǐng)域、服務(wù)器電源、通訊電源等工業(yè)電子領(lǐng)域、以及充電樁、車載充電器等汽車電子領(lǐng)域。

在超結(jié)VDMOS中,耐壓層由交替的高摻雜N柱和P柱構(gòu)成(右側(cè)圖為超結(jié)),且N柱和P柱中的摻雜總量相等。在導(dǎo)通狀態(tài)下,電流從源極經(jīng)N柱流到漏極,P柱中不存在導(dǎo)電通道,而在阻斷狀態(tài)下,超結(jié)VDMOS的漂移區(qū)通過P柱的輔助耗盡作用在較低漏電壓下就完全耗盡。

由于完全耗盡,P柱與N柱的等量異種電荷相互抵消而實(shí)現(xiàn)電荷平衡,電場在漂移區(qū)中近似于處處相等,因而擊穿電壓約等于臨界電場與漂移區(qū)長度的乘積,這使得超結(jié)VDMOS的特征導(dǎo)通電阻與其擊穿電壓近似呈線性關(guān)系(1.32方甚至到1.03方),而不是傳統(tǒng)器件的2.5方關(guān)系,進(jìn)而可以減小導(dǎo)通電阻。

目前超結(jié)結(jié)構(gòu)主要有兩種工藝實(shí)現(xiàn)方式:多次外延工藝和深槽刻蝕加摻雜。

(一)多次外延工藝

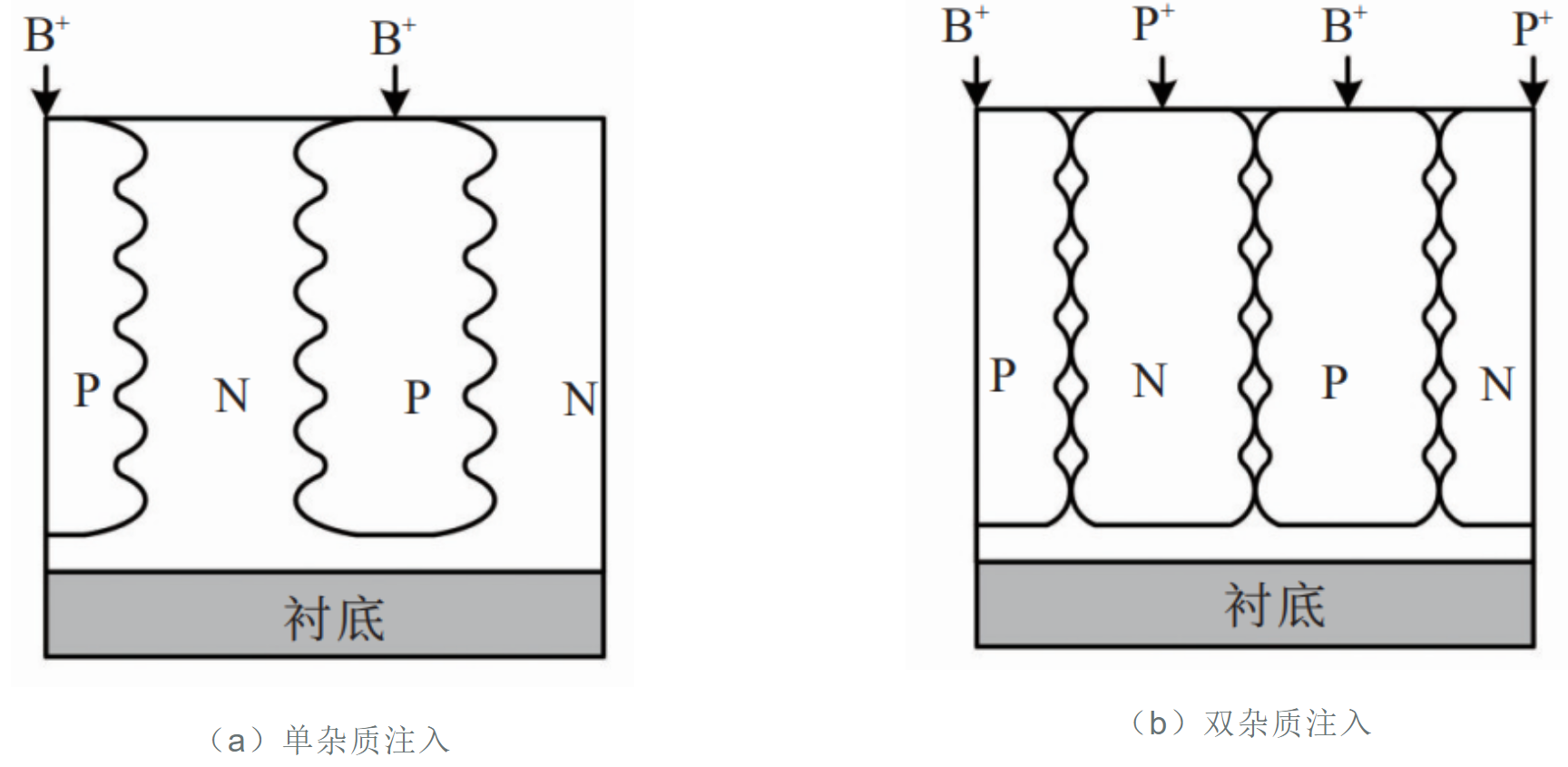

該工藝是在N型襯底上采用多次外延方式生長很厚的漂移區(qū),每一次外延工藝均伴隨一次P型離子注入,隨后推結(jié)形成連續(xù)的P柱。制作一個(gè)約40μm深的P柱,一般需要進(jìn)行5到6次外延生長和離子注入。

多次外延工藝

注意剛剛提到的方法是,通過多次外延一定濃度的N型區(qū),然后僅僅采用單雜質(zhì)(P型)注入補(bǔ)償形成P柱。多次外延工藝實(shí)際上還有第二種方法(雙雜質(zhì)注入),是每次外延濃度較低,然后同時(shí)引入N和P型注入,分別形成超結(jié)的N柱和P柱,第二種工藝可以控制更好的均勻性,但工藝上需增加一次光刻與離子注入。

此類工藝的優(yōu)點(diǎn)是形成超結(jié)耐壓層的晶格質(zhì)量較好,缺陷與界面態(tài)少。然而為形成較好超結(jié)形貌,每次外延層厚度相對固定且較薄,外延次數(shù)將隨著器件耐壓增大而增多,導(dǎo)致成本增加。

(二)深槽刻蝕加摻雜

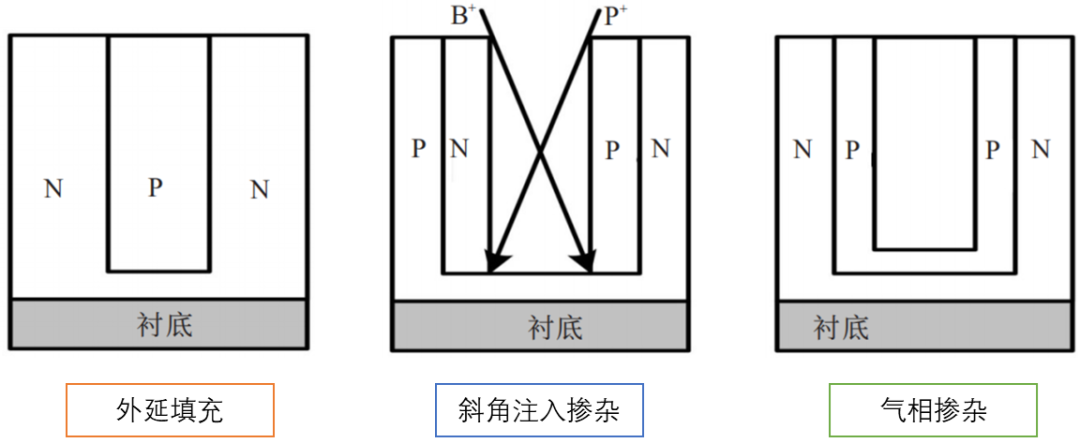

該工藝是在外延層上刻蝕出深溝槽,然后再對槽做內(nèi)部摻雜。摻雜的方式通常分為三種:

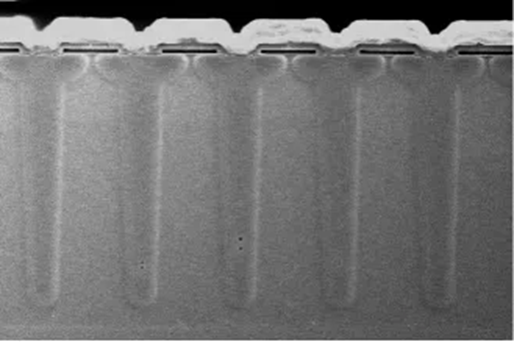

第一種方式是外延填充。在槽內(nèi)外延填充P型硅,然后采用化學(xué)機(jī)械拋光(CMP)實(shí)現(xiàn)平坦化;當(dāng)然也可以先在槽壁上形成薄氧化層結(jié)構(gòu),再進(jìn)行多晶硅填充形成P柱。

第二種方式是斜角注入摻雜。采用傾斜注入方式分別在槽壁上形成N柱和P柱,這樣可以通過控制N和P型雜質(zhì)的注入劑量來實(shí)現(xiàn)電荷平衡。

第三種方式是氣相摻雜,通過對槽壁進(jìn)行氣相摻雜形成P柱。

深槽外延工藝

采用深槽刻蝕加外延填充工藝實(shí)現(xiàn)的超結(jié)耐壓區(qū),較多次外延工藝更易實(shí)現(xiàn)較小的深寬比,同時(shí)形成的超結(jié)區(qū)摻雜分布也較均勻,有利于降低導(dǎo)通電阻。

-

MOSFET

+關(guān)注

關(guān)注

148文章

7806瀏覽量

217047 -

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28285瀏覽量

229420 -

VDMOS

+關(guān)注

關(guān)注

0文章

28瀏覽量

20066 -

開關(guān)器件

+關(guān)注

關(guān)注

1文章

192瀏覽量

17077

原文標(biāo)題:【推薦】超結(jié)(SJ)制造工藝簡介

文章出處:【微信號(hào):芯長征科技,微信公眾號(hào):芯長征科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

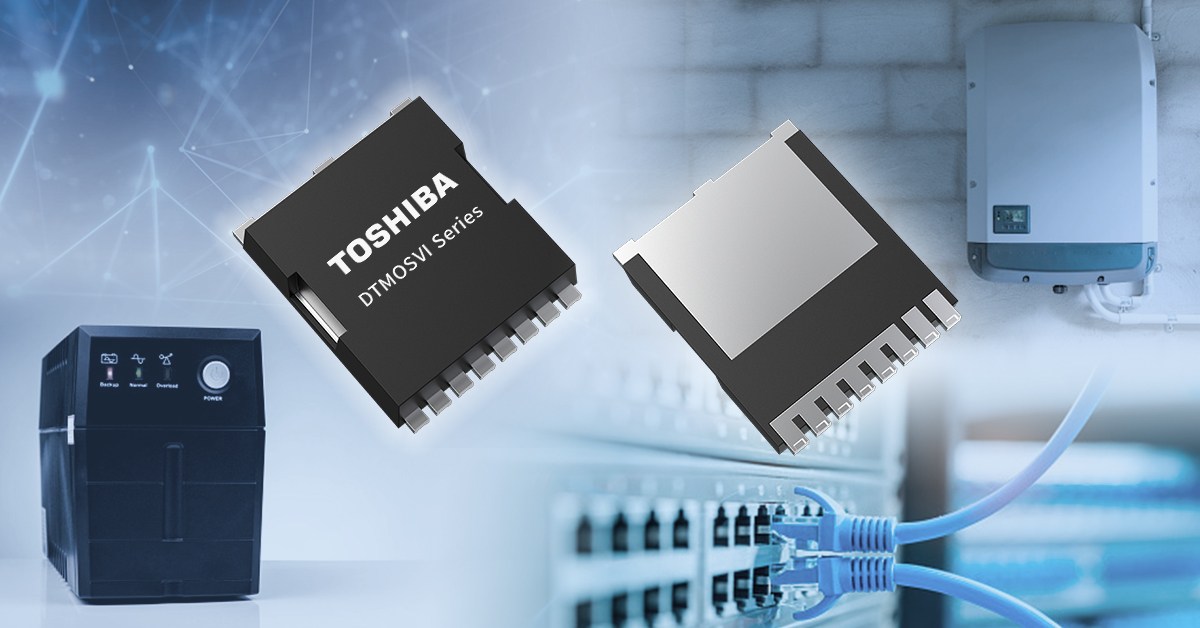

東芝推出采用超級結(jié)結(jié)構(gòu)的600V N溝道功率MOSFET,助力提高電源效率

COMSOL Multiphysics在超材料與超表面仿真中的應(yīng)用

研究生畢業(yè)繼續(xù)送資料——超經(jīng)典復(fù)旦大學(xué)微電子工藝教案

多核DSP與超核DSP的基本結(jié)構(gòu)討論

LTCC多層濾波器的工藝怎么實(shí)現(xiàn)?

MCU總結(jié)結(jié)構(gòu)和程序運(yùn)行機(jī)制的相關(guān)資料分享

應(yīng)用面結(jié)結(jié)構(gòu)的圓柱形鋰電池的簡介和3大優(yōu)勢分析

OPPO RenoTP超窄邊框點(diǎn)膠工藝揭秘

東芝拓展650V超結(jié)結(jié)構(gòu)N溝道功率MOSFET新品 景嘉微發(fā)布JH920

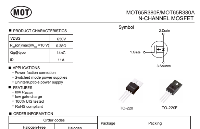

超結(jié)MOS管65R380的特點(diǎn)及應(yīng)用領(lǐng)域

FPGA的基本結(jié)構(gòu)、數(shù)據(jù)存儲(chǔ)及配置方式

超結(jié)高壓功率MOSFET驅(qū)動(dòng)參數(shù)對開關(guān)特性有什么影響

為什么超結(jié)高壓功率MOSFET輸出電容的非線性特性更嚴(yán)重?

功率MOSFET基本結(jié)構(gòu):超結(jié)結(jié)構(gòu)

評論