1 引言

射頻功率放大器是無線發射機中的核心模塊之一,也是無線收發機*耗最大的模塊,為了 降低功耗,延長電池壽命,要求它具有高效和大功率輸出。隨著硅CMOS 工藝的不斷改進,采用 標準CMOS 工藝實現高性能的功率放大器是當今射頻電路向尺寸更小、價格更低以及全片集成方 向發展的必然趨勢,科研工作者們在相關理論研究以及電路性能的改進方面做了大量工作[1~5]。 本文基于0.18μm CMOS 工藝,主要從高效率和集成化的角度優化考慮,設計實現了一個工作頻 率在2.4GHz 處的兩級全集成E 類開關模式功率放大器,獲得較好的仿真效果。

2 工作原理

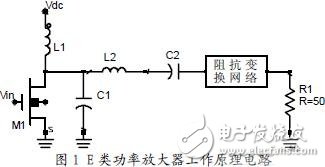

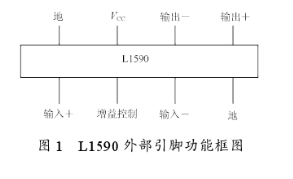

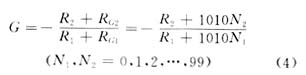

圖1 給出了標準E 類功率放大器工作原理電路。其中,扼流電感 L1 阻止交流信號通過,并 給晶體管提供直流電流。 L2 、 C2 組成一個串聯諧振網絡,以使流過該網絡的電流為理想的正弦 信號,所有諧波成分都被濾除。并聯接地電容 C1 由兩部分組成,一部分是晶體管的寄生電容,另 一部分是實際引入的電容。驅動電壓過驅動使得晶體管M1 可近似作為開關來使用,當它導通時,晶體管上壓降為零;而當它截止時,流過晶體管的電流為零。E 類功率放大器正是通過對開關上 的電壓整形,使得在開關導通瞬間,開關上的電壓和電壓變化斜率都近似為零,從而達到減小開 關損耗,提高效率的目的。通常電路元件參數可由以下公式大致確定[6]:

其中,Q為電路品質因數,ω 為工作頻率, dc V 、dc I 為漏端電壓、電流, RL 為獲得所需功率out P 而將終端50Ω 電阻進行阻抗變換得到的匹配電阻。

3 電路設計與分析

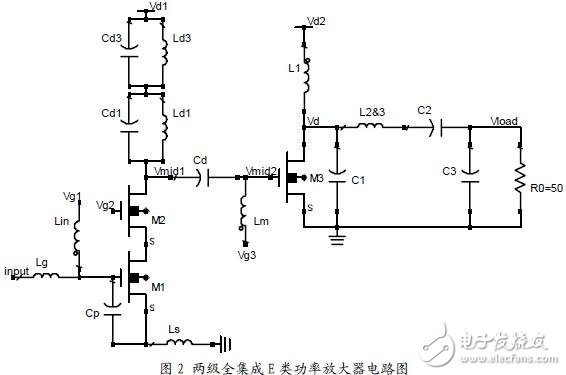

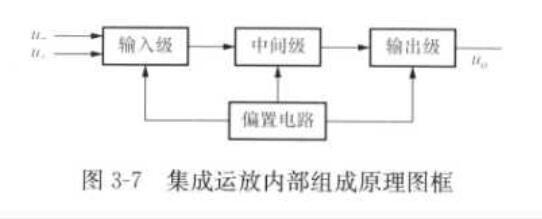

通常情況,單級功率放大器增益僅為 10dB 左右,需要增加高增益的驅動級來提高整體功放 的增益。因此,功率放大器設計一般就分為功率輸出級、輸出匹配、增益驅動級、級間匹配、輸 入匹配等部分。圖2 為本文基于這種結構思想、采用0.18μm CMOS 工藝設計實現的兩級全集成 E 類開關模式功率放大器的具體電路,其中驅動級為準F 類,輸出級為E 類。

3.1 功率輸出級

功率輸出級采用工作原理中介紹的標準 E 類功率放大器結構,這種直接由M3 管構成的共源 結構能夠充分利用電源電壓的幅度,提高輸出電壓擺幅。由于E 類功率放大器的漏端最高電壓可 能升高到3.6Vd 2 [1],為保證MOS 管不被擊穿,電路選用2V 電壓供電。功率輸出級是射頻功率 放大器中最關鍵的一級,它的性能特性包括輸出功率、效率等將直接影響整個放大器的性能。晶 體管必須選取在最小電壓降時至少可以提供dc I 大小的直流電流,且工作在線性區。同時,還得 對該晶體管的輸出功率和效率進行掃描*估,以確保選取的晶體管可以達到預設計的性能指標要 求。我們在設計過程中的經驗表明,通過負載牽引(Load-Pull)技術能有效的預測輸出晶體管的 輸出功率和效率,并在整體電路設計好后這兩項指標還會有所提高。

3.2 輸出匹配網絡

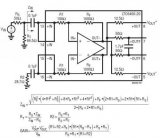

通常電路終端接的是 50Ω 的電阻,為獲得理想的輸出功率由公式(1)計算得到的實際負載 RL 通常比較小,需要阻抗變換。輸出匹配網絡的目的就是提供器件的輸出端到負載阻抗之間的最大 功率傳輸所需要的阻抗。為了最小化無源器件和有效濾除高次諧波分量,電路選用如圖3 線框中 所示的L 型低通阻抗匹配結構。這樣, L 型低通阻抗變換電路電感 L3 便可與功率輸出級的串聯 諧振電感 L2 合二為一成電感L2&3 ,從而有效減少片上電感所占據的芯片面積。由于功率放大器 工作頻率較高,使得晶體管阻抗特性的各參數受到工作頻率、輸入電平、輸出端負載阻抗、電源 偏置以及溫度等的影響。功率放大器晶體管的阻抗一般來講是一個復數,并且不僅會隨著頻率的 變化而變化,還會隨輸出信號的電壓和電流而變化,這樣輸出級與天線之間的阻抗變換網絡的實 現就比較困難。在設計中,輸出阻抗變換網絡我們采用Load-Pull 技術來獲取最佳負載阻抗,然 后根據該阻值利用Smith 圖解設計工具便可獲得低通阻抗匹配元件的具體參數。

3.3 增益驅動級

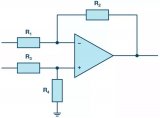

增益驅動級采用由 M1、M2 組成的共源共柵(Cascode)結構加兩個諧振網絡一起構成的準 F 類放大器模式。共源共柵結構可以有效降低Miller 電容的影響,提高輸入-輸出之間的隔離度。 兩個諧振網絡中: Cd1 和L d1 構成的諧振器調諧在ω 處, Cd 3 和Ld 3 構成的諧振器調諧在3ω 處。 通過適當地調諧這四個參數,確保諧振網絡對二次諧波短路,輸出電路為基波和三次諧波疊加, 從而獲得E 類放大器所需的近似方波驅動信號。在電路性能測試中我們發現,由于準F 類放大器 結構的開關電壓峰峰值可達到2Vd1,因此增益驅動級的電源電壓可以大大降低,從而可以有效減 少整個電路的直流功耗,提高電路的整體效率。

3.4 級間匹配網絡

級間匹配網絡需要匹配前一級器件的輸出阻抗和后一級器件的輸入阻抗,應選擇高增益的級 間拓撲,并實現平坦的增益響應。級間匹配還應具備級間隔直流功能,通常加入隔直電容Cd 。 電路并聯電感 Lm 可使功率輸出級輸入端看到的MOS 管寄生電容Cm 減小,從而提高電壓傳輸效 率[5]。級間匹配等效電路如圖4 所示,從增益驅動級輸出端看到的等效阻抗為:

增益驅動級的方波信號是由基波和三次諧波疊加而成,因此通過公式(5)要確保增益驅動 級輸出端看到的三次諧波和基波等效阻抗必須具有相同的容性或感性,否則會由于相位相反無法 形成方波。此外,測試中我們還發現Cd 值對傳輸效率影響比較敏感,為提高電壓傳輸效率, Cd 一般需要取較大值。

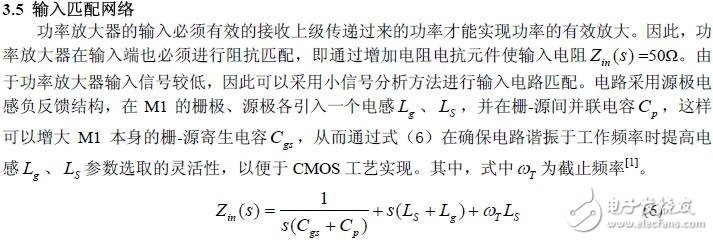

4 仿真分析

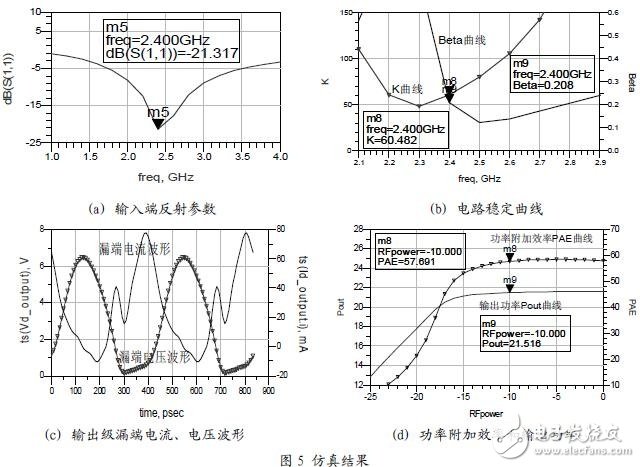

本設計基于0.18μm CMOS 工藝,充分考慮了片上電感品質因數不高、電感值較小和占有面 積較大的局限條件下,實現了電路的全片集成。在2V 電源電壓條件下利用ADS2005A 進行仿真, 仿真結果如圖5 所示。

當電流Id 趨于零時電壓Vd達到峰值,而當電流Id 達到峰值時電壓Vd趨于零,這與理想E 類開關 模式功率放大器的輸出目標基本吻合,從而實現電路較大功率和較高效率的輸出。圖(d)表明,電 路在輸入功率為-10dBm 時的輸出功率約為21.5dBm,功率附加效率達到了57.69%的較好結果, 相應功率增益為31dB。

在性能仿真過程中我們發現,電路各級的阻抗匹配對電路的影響都非常大,阻抗匹配是電路 設計成敗的關鍵。采用Load-Pull 技術是獲取最佳輸出匹配負載和預測晶體管輸出功率和效率的 有效且便捷的手段。此外,輸出晶體管尺寸對整體電路的輸出功率和效率有著密切的聯系,存在 最佳尺寸,使得電路主要性能達到最優化,但相應對電路的工作條件如驅動級電源電壓等的要求 更高,因此需要折中考慮。

5 結論

本文的創新點在于在輸入匹配晶體管柵-源間并接電容 Cp 極大的提高了在片電感選擇的靈 活性;同時采用準F 類放大器作為驅動級,獲得了E 類功率放大器所需要的方波驅動信號。本文 設計的E 類開關模式功率放大器達到了全集成、高效、大功率輸出的目的,與國內外設計相比達 到先進水平[3-5]。隨著CMOS 工藝和電感工藝的不斷改進,由該技術實現的功率放大器在未來無 線通信領域必將有著廣泛的應用前景。

-

放大器

+關注

關注

143文章

13589瀏覽量

213482 -

電路設計

+關注

關注

6674文章

2453瀏覽量

204361 -

射頻功率

+關注

關注

0文章

40瀏覽量

12927

發布評論請先 登錄

相關推薦

基于高增益單片中頻放大器L1590實現AGC放大電路的設計

兩款固定增益放大器消除設計方案難題

淺析CMOS高線性變增益放大器

基于LMP8358的高精度可編增益儀表放大器設計方案

基于采用分立元件設計的LC諧振放大器的設計方案

采用固定增益集成型電阻器實現至差分放大器的阻抗匹配

采用包含增益驅動級,實現了全片集成的放大器設計方案

采用包含增益驅動級,實現了全片集成的放大器設計方案

評論