初學(xué)STM32,我這個地方卡了很久,現(xiàn)在終于有些明白了,現(xiàn)在把我的理解寫下與大家共享,如果有不對的地方,還請指出。

TIM_OCMode選擇定時器模式。該參數(shù)取值見下表:

TIM_OCInitStructure.TIM_Pulse = CCR1_Val; //設(shè)置跳變值,當(dāng)計數(shù)器計數(shù)到這個值時,電平發(fā)生跳變

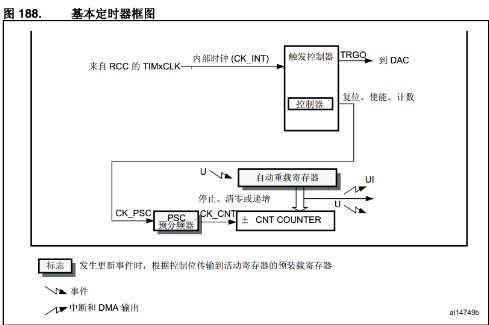

TIM_OC2PreloadConfig(TIM3, TIM_OCPreload_Enable); //使能TIMx在CCR1上的預(yù)裝載寄存器 TIM_ARRPreloadConfig(TIM3, ENABLE); //使能TIMx在ARR上的預(yù)裝載寄存器

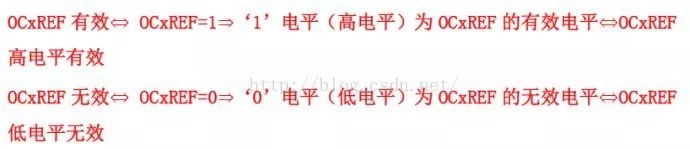

OCxREF就是一個參考信號,并且約定:OCxREF=1,稱OCxREF有效。反之,OCxREF=0,稱OCxREF無效;‘1’電平(高電平)稱為OCxREF的有效電平,‘0’ 電平(低電平)稱為OCxREF的無效電平。——依據(jù)參考手冊:The output stage generates an intermediate waveform which is then used for reference:OCxRef (active high). The polarity acts at the end of the chain.(翻譯)輸出階段產(chǎn)生一個中間波形OCxRef(高有效)作為參考。輸出信號的極性體現(xiàn)在信號鏈的末端。

現(xiàn)在解釋幾個名詞之間的關(guān)系:

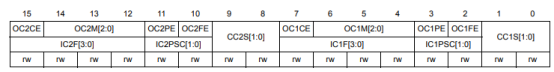

然后來理解輸出比較的幾個模式(PWM模式是輸出比較模式的特例)查看TIMx_CCMR1寄存器的OC1M域,有如下定義(摘自最新版的參考手冊

翻譯如下:000:凍結(jié)——輸出比較寄存器TIMx_CCR1中的內(nèi)容與計數(shù)器TIMx_CNT中的內(nèi)容之間的比較對輸出無影響。(此模式用于時基的生成)001:當(dāng)匹配時,設(shè)置通道1為有效電平。當(dāng)計數(shù)器TIMx_CNT中的內(nèi)容與捕捉/比較寄存器1(TIMx_CCR1)中的內(nèi)容相匹配時,強行拉高OC1REF 信號。010:當(dāng)匹配時,設(shè)置通道1為無效電平。當(dāng)計數(shù)器TIMx_CNT中的內(nèi)容與捕捉/比較寄存器1(TIMx_CCR1)中的內(nèi)容相匹配時,強行拉低OC1REF 信號。011:翻轉(zhuǎn)——當(dāng)TIMx_CNT= TIMx_CCR1時,OC1REF信號取反。100:強制無效電平——強行拉低OC1REF 信號。101:強制有效電平——強行拉高OC1REF 信號。110:PWM模式1——向上計數(shù)模式中,只要TIMx_CNT< TIMx_CCR1,通道1有效,反之無效。向下計數(shù)模式中,只要TIMx_CNT> TIMx_CCR1,通道1無效(OC1REF=0),反之有效(OC1REF=1)。110:PWM模式2——向上計數(shù)模式中,只要TIMx_CNT< TIMx_CCR1,通道1無效,反之有效。向下計數(shù)模式中,只要TIMx_CNT> TIMx_CCR1,通道1有效,反之無效。我用紅色標(biāo)出了提到有效、無效的地方。不難發(fā)現(xiàn),有效與無效分別對應(yīng)OC1REF=1和OC1REF=0。這正是我們先前約定的結(jié)果。到此,不同模式下輸出比較的結(jié)果對OC1REF信號的影響已經(jīng)很清楚了,但是最終的輸出信號是OC1,并不是OC1REF。而且前面有一句話(輸出信號的極性體現(xiàn)在信號鏈的末端)還未做解釋。到底OC1REF與OC1之間有何秘密呢?我們來看下面這個圖:

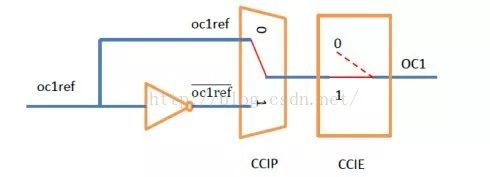

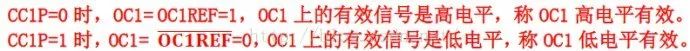

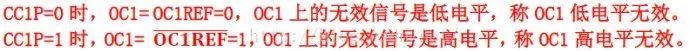

顯然,我們只關(guān)心紅色圈內(nèi)的信號與方框內(nèi)的寄存器位以及信號在它們之間是如何傳播的。oc1ref從輸出模式控制器(Output mode controller)開始,分為兩路,上面一路至主模式控制器(To the master mode controller),這里我們不關(guān)心它的去向,我們關(guān)心的是下面一路,下面一路在進入雙路開關(guān)之前又被分成了兩路——一路是原信號,一路是原信號的非。顯然TIMx_CCER中的CC1P位用來控制這個開關(guān),CC1E位控制著整條信號鏈的通斷。當(dāng)CC1P=0時(CC1E=1):

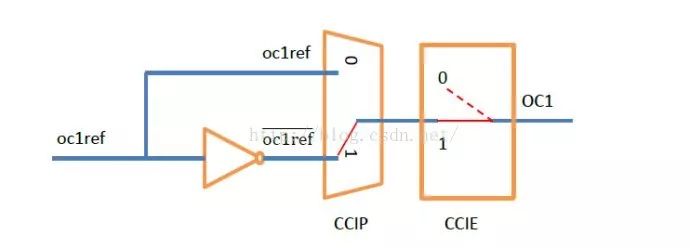

當(dāng)CC1P=1時(CC1E=1):

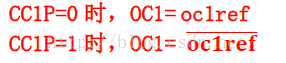

很顯然,OC1與OC1REF的關(guān)系只受CC1P的影響(CC1E=1)

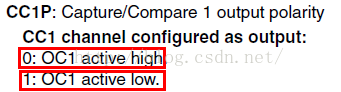

然而參考手冊上對CC1P位是這么描述的:

CC1P=0時:OC1高電平有效CC1P=1時:OC1低電平有效根據(jù)本文開篇的名詞解釋,可以這么理解:CC1P=0時:OC1有效電平是高電平CC1P=1時:OC1有效電平是低電平這時就迷惑了,這個高電平有效和低電平有效是啥意思呢?我們從頭分析(整個過程CC1E=1,OC1的輸出是允許的):①假定OC1REF有效(OC1REF=1),那么從OC1REF到OC1的整條信號鏈上的信號都是有效信號,我們稱OC1輸出了有效信號。那這個有效信號是高電平還是低電平呢?這就是由CC1P決定的:

②假定OC1REF無效(OC1REF=0),那么從OC1REF到OC1的整條信號鏈上的信號都是無效信號,我們稱OC1輸出了無效信號。無效信號的高電平和低電平也是由CC1P決定:

| OC1REF | CC1P | 功能 | OC1 | 描述 |

| 0 | 0 | OC1高電平有效 | 0(低電平) | 無效 |

| 1 | OC1低電平有效 | 1(高電平) | 無效 | |

| 1 | 0 | OC1高電平有效 | 1(高電平) | 有效 |

| 1 | OC1低電平有效 | 0(低電平) | 有效 |

顯然,OC1REF決定了OC1輸出電平是否有效,而CC1P決定了有效電平的極性。我們抽出上表的后四列

| CC1P | 功能 | OC1 | 描述 |

| 0 | OC1高電平有效 | 0(低電平) | 無效 |

| 1 | OC1低電平有效 | 1(高電平) | 無效 |

| 0 | OC1高電平有效 | 1(高電平) | 有效 |

| 1 | OC1低電平有效 | 0(低電平) | 有效 |

我們將表按1、2列合并:

| CC1P | 功能 | OC1 | 描述 |

| 0 | OC1高電平有效 | 0(低電平) | 無效 |

| OC1高電平有效 | 1(高電平) | 有效 | |

| 1 | OC1低電平有效 | 0(低電平) | 有效 |

| OC1低電平有效 | 1(高電平) | 無效 |

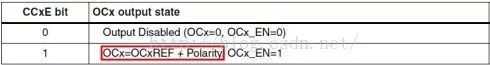

現(xiàn)在很清楚了,從上表中可以清楚地看到CC1P對OC1有效極性的控制。即,OC1的極性只有與CC1P指定的有效極性一致,OC1才能是有效的(綠色部分)。這樣就解釋了“輸出信號的極性體現(xiàn)在信號鏈的末端”這句話。然而這條鏈還未結(jié)束,還有個CC1E呢。當(dāng)然,它就是一個OC1輸出使能位而已。但細(xì)心的你可能會發(fā)現(xiàn),參考手冊上對CC1E位有這樣的描述:

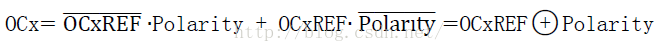

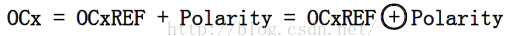

OCx = OCxREF + Polarity這個式子告訴我們OCx與OCxREF和Polarity(極性,即CCxP位)的關(guān)系。我們上面提到了它們的關(guān)系,是分了兩種情況(CC1P=0和CC1P=1)表示的,這個式子幫我們將上面關(guān)系歸納成了一個。這個式子怎么得來的?回憶一下數(shù)字電路里面的半加器(就是不進位的加法),真值表如下:

| OCxREF | Polarity | OCx |

| 0(無效) | 0(高有效) | 0(無效) |

| 0(無效) | 1(低有效) | 1(無效) |

| 1(有效) | 0(高有效) | 1(有效) |

| 1(有效) | 1(低有效) | 0(有效) |

我們寫邏輯函數(shù)(按黃色部分寫):

注意:前面的“+”號表示半加運算(不進位加法),其實是邏輯上的“異或”。

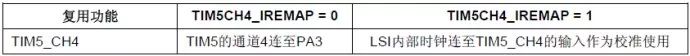

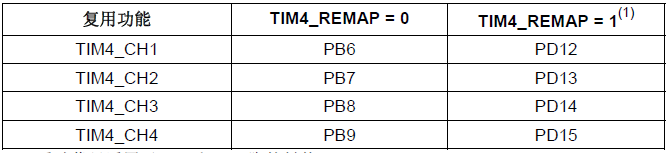

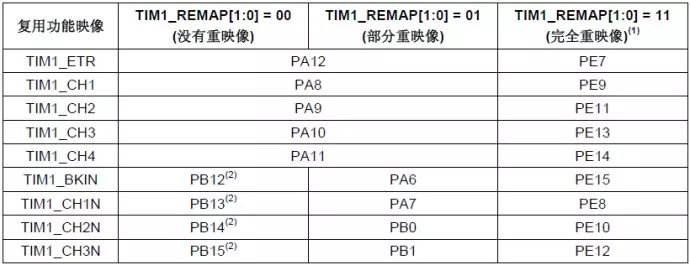

OC1連接到TIMx_CH1上,而TIMx_CH1是復(fù)用的。可在參考手冊上定時器功能復(fù)用部分找到。下面給出一些定時器功能復(fù)用的表格:

-

STM32

+關(guān)注

關(guān)注

2270文章

10896瀏覽量

355757 -

定時器

+關(guān)注

關(guān)注

23文章

3246瀏覽量

114726

原文標(biāo)題:STM32定時器輸出比較模式中的疑惑

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

STM32定時器-基本定時器

stm32之定時器

STM32-通用定時器-定時器中斷

【捕獲比較模式】msp430定時器比較捕獲理解

stm32定時器輸出比較模型翻轉(zhuǎn)電平驅(qū)動步進電機

分享STM32定時器輸出比較模式的理解

分享STM32定時器輸出比較模式的理解

評論